业界领先的全新 1.8V 版 VersaClock® 3S 可编程时钟发生器,为消耗品和计算系统创造具有竞争力的性能、能耗和灵活性。

2017-09-28 10:15:46 8178

8178 Silicon Labs(亦称“芯科科技”)最新发布的Si538x 系列无线时钟发生器利用我们的最新第四代

2017-10-17 09:36:30 7169

7169 Si50122-A5 时钟发生器 计时 评估板

2024-03-14 22:30:31

SI5324-EVB,SI5324评估板,0.002至710 MHz时钟发生器。 SI5324-EVB为评估SI5316任意速率精度时钟提供平台。 SI5316直接使用器件上的配置引脚进行控制

2019-02-22 09:30:51

Si5348 时钟发生器 计时 评估板

2024-03-14 22:30:44

Si5350,Si5351 时钟发生器 计时 评估板

2024-03-14 22:30:46

概述:AD9577是一款既提供一个多路输出时钟发生器功能,又带有两个片上锁相环内核PLL1和PLL2,专门针对网络时钟应用而优化。PLL设计基于ADI公司成熟的高性能、低抖动频率合成器产品系列,确保实现最高的网

2021-04-06 06:49:57

(ADC/DAC))和本振(LO)要求采用低抖动参考时钟以提高性能。其他基带组件也要求各种频率的时钟源。表1.时钟发生器——典型性能表2.时钟分配产品——典型性能图1.面向采用MIMO架构的典型LTE

2018-10-18 11:29:03

系统设计师通常侧重于为应用选择最合适的数据转换器,在向数据转换器提供输入的时钟发生器件的选择上往往少有考虑。然而,如果不慎重考虑时钟发生器的相位噪声和抖动性能,数据转换器动态范围和线性度性能可能受到严重的影响。

2019-07-30 07:57:42

输出时钟分配功能,具有亚皮秒级抖动性能,并且片内集成锁相环(PLL)和电压控制振荡器(VCO)。 产品名称:时钟发生器 AD9520-3BCPZ特征低相位噪声、锁相环(PLL)片内VCO的调谐频率范围为

2019-07-09 11:50:41

`AD9571ACPZPEC时钟发生器产品介绍AD9571ACPZPEC询价热线AD9571ACPZPEC现货AD9571ACPZPEC代理王先生***深圳市首质诚科技有限公司, AD9571具有

2019-07-09 10:19:09

AKD8140A Ver.2,AK8140A可编程多时钟发生器评估板。评估抖动性能和功能很容易

2020-07-27 15:01:46

本应用指南讨论了CY2254 PLL时钟发生器的内部结构,并提出一些使用建议。

2014-09-23 10:00:14

STM32F767 SAI SPDIF 输出、NODIV 和时钟发生器当在 SAIx->CR1 中设置 NODIV 位时,SPDIF 输出频率是它应该的。例子:时钟输入为 25.6 MHz

2022-12-05 06:05:47

概述:MAX3625B是MAXIM公司生产的一款提供三路输出的低抖动,高精度时钟发生器。该MAX3625B是为网络应用而优化的低抖动,高精度时钟发生器。该器件集成一个晶体振荡器和锁相环(PLL)时钟

2021-05-18 07:39:05

专业销售、维修、回收 高频 二手仪器。 产品型号: CG635美国斯坦福时钟发生器信息描述:时钟可调频由0.001Hz到2.05GHz少于1PS的RMS抖动可支持CMOS。PECL,ECL,LVDS

2020-08-18 09:08:58

可编程音频时钟发生器MAX9485资料下载内容主要介绍了:MAX9485引脚功能MAX9485功能和特性MAX9485应用范围MAX9485内部方框图MAX9485极限参数MAX9485典型应用电路

2021-04-02 06:21:48

SI5340-EVB,评估板用于评估Si5340低抖动任意频率时钟发生器。 Si5340采用获得专利的Multisynth技术,可产生多达10个独立时钟频率,每个频率具有0 ppm的合成误差

2019-02-26 09:28:56

SI5341-EVB,评估板用于评估Si5341低抖动任意频率时钟发生器。 Si5341采用获得专利的Multisynth技术,可产生多达10个独立时钟频率,每个频率具有0 ppm的合成误差

2019-02-25 07:03:01

我要做毕业设计 叫 基于lmk03806的高性能可编程时钟发生器的设计与fpga实现,需要有protel 99se画 lmk03806的原理图和fpga的配置电路,用vhdl编程仿真,用fpga来配置lmk03806,求高手求助{:1:}

2013-05-03 23:06:27

我正在使用planahead 14.4在VC707上添加7系列MIG(IP版本1.07a)。当我使用第一个具有200MHz振荡器输入的时钟发生器驱动MIG时,我的设计可以完全路由,我尝试

2020-08-11 10:07:25

在我们的设计中,其中一个模块从外部可配置时钟发生器芯片接收其时钟信号。现在在我们的ML507上使用这个时钟发生器芯片IDT5V9885就在那里任何跳线设置?我们问这个是因为在我们的申请中软件我们

2019-09-02 08:12:30

找不到联系方式,请在浏览器上搜索一下,旺贸通仪器仪 产品型号: CG635美国斯坦福时钟发生器信息描述:时钟可调频由0.001Hz到2.05GHz少于1PS的RMS抖动可支持CMOS。PECL,ECL

2019-06-16 12:07:43

专业销售、维修、回收 高频 二手仪器。 产品型号: CG635美国斯坦福时钟发生器信息描述:时钟可调频由0.001Hz到2.05GHz少于1PS的RMS抖动可支持CMOS。PECL,ECL,LVDS

2020-12-03 08:39:05

AD9525 / PCBZ,用于AD9525时钟发生器的评估板。 AD9525旨在支持长期演进(LTE)和多载波GSM基站设计的转换器时钟要求。 AD9525提供低功耗,多输出,时钟分配功能和低抖动

2019-02-25 08:38:34

AD9576 / PCBZ,AD9576评估板提供多输出时钟发生器功能,包括两个专用锁相环(PLL)内核,具有灵活的频率转换功能,经过优化,可作为整个系统的强大异步时钟源,提供扩展功能通过监控和冗余

2019-02-25 09:40:01

SI52147-EVB,用于PoE无线接入点的时钟发生器评估板。 Si52147是一款符合PCIe Gen1,Gen2和Gen3标准的9端口PCIe时钟发生器

2020-08-27 14:27:11

描述TIDA-00597 可为时钟发生器提供噪声非常低的输出电源。主要特色低噪声,适用于时钟发生器输出电流高达 800mA低相位噪声输出功率启用和禁用

2018-08-22 07:43:40

AC1571时钟发生器一款基于PLL的、适用于5G基站应用的时钟发生器。采用数字锁相环技术,以实现最佳的高频低相噪性能,具有低功耗和高PSRR能力。采用ADPLL技术,管脚兼容843N571,可以

2022-08-11 16:26:33

SI52112-B6-GTR,PCI-EXPRESS GEN 3 双输出时钟发生器 描述

2023-02-13 17:51:33

针对直接数字频率合成(DDS)和集成锁相环(PLL)技术的特性,提出了一种新的DDS 激励PLL 系统频率合成时钟发生器方案。且DDS 避免正弦查找表,即避免使用ROM,采用滤波的方法

2009-12-14 10:22:00 36

36 SI5338Q-B-GM,SILICON/芯科,I2C可编程任意频率、任意输出 四路时钟发生器SI5338Q-B-GM,SILICON/芯科,I2C可编程任意频率、任意输出 四路时钟发生器

2023-10-17 17:02:33

AC1571 是用于 5G 基站应用的基于 PLL的时钟发生器,该芯片采用全数字锁相环技术,以实现最佳的高频低相噪性能,并具有低功耗和高PSRR能力。典型应用场景:· 无线基站·

2023-12-12 14:25:17

时钟发生器芯片厂家 时钟芯片是一种基于PLL的时钟发生器,采用ADPLL(全数字锁相环)技术,以实现的高频低相噪性能,并具备低功耗和高PSNR能力,可实现小于0.3ps RMS的相位抖动性能

2023-12-29 09:29:50

时钟发生器芯片厂家 时钟芯片是一种基于PLL的时钟发生器,采用ADPLL(全数字锁相环)技术,以实现的高频低相噪性能,并具备低功耗和高PSNR能力,可实现小于0.3ps RMS的相位抖动性能

2024-02-04 11:41:14

MAX9489/MAX9471多输出时钟发生器构建集成时钟源

摘要:与典型的“本地”时钟方案相比,集成的多输出时钟发生器有许多优势。本文探讨了集中时钟发生器(如

2008-10-04 20:43:25 922

922

Si5338 业界首个任意频率、任意输出的时钟发生器

高性能模拟与混合信号领导厂商Silicon Laboratories日前发表全新的时钟发生器和缓冲器系列,可为业

2008-11-10 09:39:44 1763

1763

精密时钟发生器电路图

2009-03-25 09:35:22 1054

1054

振荡器时钟发生器电路图

2009-04-13 08:54:22 720

720

摘要:MAX9450/MAX9451/MAX9452是集成了VCXO,具有相同PLL内核和三种不同输出(LVPECL, HSTL,LVDS)的高精度时钟发生器。MAX945x时钟发生器具有四个主要的特点:集成VCXO,工作频率范围宽,PLL

2009-04-22 09:42:01 966

966

摘要:与典型的“本地”时钟方案相比,集成的多输出时钟发生器有许多优势。本文探讨了集中时钟发生器(如MAX9489和MAX9471)的优点,如:降低系统成本、良好的信号完整性、抑制干

2009-04-22 10:11:53 407

407

摘要:与典型的“本地”时钟方案相比,集成的多输出时钟发生器有许多优势。本文探讨了集中时钟发生器(如MAX9489和MAX9471)的优点,如:降低系统成本、良好的信号完整性、抑制干

2009-05-03 11:07:05 653

653

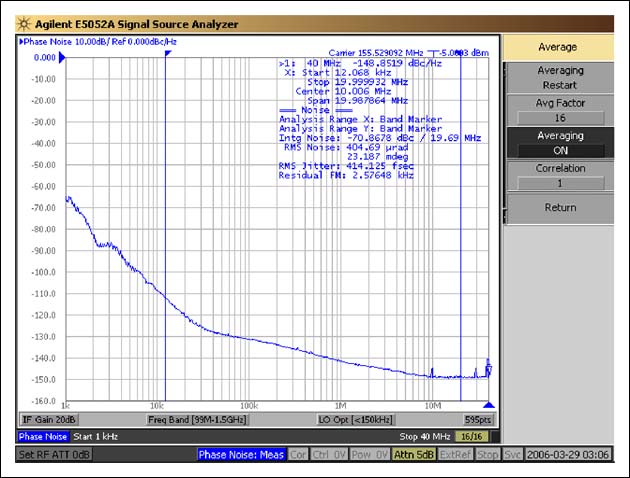

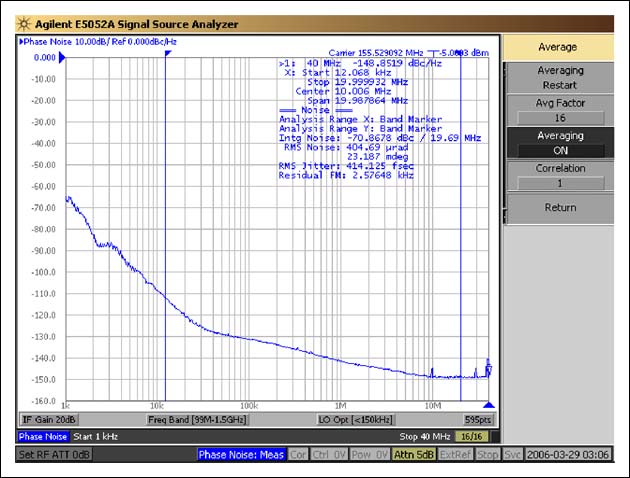

评估低抖动PLL时钟发生器的电源噪声抑制性能

本文介绍了电源噪声对基于PLL的时钟发生器的干扰,并讨论了几种用于评估确定性抖动(DJ)的技术方案。推导出的关系式提

2009-09-18 08:46:32 1461

1461

MAX3625B 抖动仅为0.36ps的PLL时钟发生器

概述

MAX3625B是一款低抖动、精密时钟发生器,优化用于网络设备。器件内置晶体振荡器和锁相环(PLL)

2010-03-01 08:56:18 1345

1345

MAX3679A高性能四路输出时钟发生器(Maxim)

Maxim推出用于以太网设备的高性能、四路输出时钟发生器MAX3679A。器件采用低噪声

2010-04-14 16:51:49 778

778 如何利用GPS OEM来进行二次开发,产生高精度时钟发生器是一个研究的热点问题。在电力系统、CDMA2000、DVB、DMB等系统中,高精度的GPS

2010-07-24 15:45:26 780

780 在电力系统、CDMA2000、DVB、DMB等系统中,高精度的GPS时钟发生器(GPS同步时钟)对维持系统正常运转有至关重要的意义。

那如何利用GPS OEM来进行二次开发,产生高精度时钟发生

2010-09-17 22:02:44 1273

1273 DS1091L是一款低成本的时钟发生器,输出频率由工厂预置到130kHz至66.6MHz,标称精度为±0.25%。器件可产生中心抖动或降频抖动扩频输出,具有引脚可选的抖动幅度和抖动速率。

2011-03-16 10:57:41 1037

1037

IDT面向便携应用推出全球首款集成可编程时钟发生器的音频子系统。新器件通过集成,可实现占板空间的最小化、降低系统成本,同时由于无需长货期的外部晶体和振荡器,缩短产品上

2011-08-10 09:01:55 920

920 在有效抑制EMC 干扰的扩频时钟发生器(SSCG)中内置FRAM 的新产品MB88R157A 被纳入富士通的产品阵容。针对10MHz ~ 50MHz 的输入频率,该产品的输出时钟频率可以在1MHz ~ 134MHz 范围内任意设

2011-08-31 17:26:32 40

40 MAX3636是一个高度灵活,高精度锁相环(PLL)时钟发生器为下一代网络设备的要求低抖动时钟发生器和强大的高速数据传输的分布进行了优化。

2011-10-11 11:15:22 1329

1329

Silicon Laboratories (芯科实验室有限公司)日前宣布扩展其PCI Express(PCIe)时钟发生器和时钟缓冲器产品组合。

2012-02-02 09:31:56 1395

1395 DS1086 EconOscillator™是可编程的时钟发生器,它可以在260kHz至133MHz的频率范围内产生扩展频谱(抖动)方波输出。

2012-03-22 15:43:01 1175

1175

DS1088C是一种低成本的时钟发生器,无需外部定时元件产生的方波输出。是在工厂校准的频率为133MHz的固定频率振荡器。该设备具有掉电引脚为功耗敏感的应用。

2012-03-30 17:13:43 945

945

10GHz扩频时钟发生器的设计_胡帅帅

2017-01-07 21:28:58 1

1 Microchip基于MEMS的时钟发生器

2018-06-07 13:46:00 4534

4534

Microchip基于MEMS的时钟发生器

2018-07-08 01:23:00 3933

3933 Silicon Labs(亦称“芯科科技”)最新发布的Si5332任意频率的时钟发生器可以为10/25/100G 数据中心的时钟设计提供最高级别的集成度,包含通信和工业应用程序中的完整时钟树整合,进而降低系统的物料成本并加快开发时程。

2018-08-24 17:51:28 6116

6116 据麦姆斯咨询报道,Microchip推出了业界尺寸最小的MEMS时钟发生器DSC613。这款新器件可在电路板上最多替换掉三个晶振和振荡器,从而减少高达80%的时钟元件布板空间。

2018-11-15 16:38:26 3910

3910 AD9523:14路LVPECL/LVDS/HSTL输出 或29路LVCMOS输出 低抖动时钟发生器

2019-07-04 06:18:00 3604

3604 Si5338是一种高性能、低抖动的时钟发生器,能够在设备的四个输出驱动器上合成任意频率。这种定时集成电路能够替换多达四个不同频率的晶体振荡器或作为频率转换器工作。Si5338采用其专利

2019-10-29 08:00:00 0

0 系统设计师通常侧重于为应用选择最合适的数据转换器,在向数据转换器提供输入的时钟发生器件的选择上往往少有考虑。然而,如果不慎重考虑时钟发生器的相位噪声和抖动性能,数据转换器动态范围和线性度性能可能受到严重的影响。

2020-11-22 11:34:38 2666

2666

AD9520-0:12路LVPECL/24路CMOS输出时钟发生器,集成2.8 GHz VCO

2021-03-19 09:02:27 0

0 AD9525: 8路LVPECL输出低抖动时钟发生器

2021-03-21 15:00:20 0

0 AD9518-1:6输出时钟发生器,集成2.5 GHz压控振荡器数据表

2021-03-22 19:55:03 1

1 AD9517-2:12输出时钟发生器,集成2.2 GHz压控振荡器数据表

2021-04-13 11:57:48 0

0 AD9517-1:12输出时钟发生器,集成2.5 GHz压控振荡器数据表

2021-04-13 12:02:55 1

1 AD9571:以太网时钟发生器,10个时钟输出

2021-04-16 10:21:56 3

3 AD9520-3:12集成2 GHz压控振荡器数据表的LVPECL/24 CMOS输出时钟发生器

2021-04-16 18:38:03 3

3 AD9522-1:12 LVDS/24 CMOS输出时钟发生器,集成2.4 GHz压控振荡器数据表

2021-04-16 20:21:52 1

1 AD9522-0:12集成2.8 GHz压控振荡器数据表的LVDS/24 CMOS输出时钟发生器

2021-04-17 20:08:52 0

0 AD9520-1:12集成2.5 GHz压控振荡器数据表的LVPECL/24 CMOS输出时钟发生器

2021-04-18 11:48:20 8

8 AD9520-2:12集成2.2 GHz压控振荡器数据表的LVPECL/24 CMOS输出时钟发生器

2021-04-18 16:07:52 6

6 AD9520-5:12 LVPECL/24 CMOS输出时钟发生器数据表

2021-04-27 21:31:55 2

2 AD9516-5:14-输出时钟发生器数据表

2021-04-27 21:41:19 5

5 AD9551:多业务时钟发生器数据表

2021-04-28 10:30:52 0

0 AD9522-3:12集成2 GHz压控振荡器数据表的LVDS/24 CMOS输出时钟发生器

2021-04-28 10:38:36 7

7 AD9522-5:12 LVDS/24 CMOS输出时钟发生器数据表

2021-04-28 10:53:01 0

0 AD9522-4:12集成1.6 GHz压控振荡器数据表的LVDS/24 CMOS输出时钟发生器

2021-04-29 19:06:06 1

1 集成2.2 GHz VCO数据表的AD9522-2:12 LVDS/24 CMOS输出时钟发生器

2021-04-29 20:28:12 11

11 AD9517-4:12输出时钟发生器,集成1.6 GHz压控振荡器数据表

2021-04-30 15:51:42 10

10 AD9520-4:12集成1.6 GHz压控振荡器数据表的LVPECL/24 CMOS输出时钟发生器

2021-05-07 09:37:39 9

9 AD9575:网络时钟发生器,双输出数据表

2021-05-09 11:06:44 1

1 AD9516-3:14输出时钟发生器,集成2.0 GHz压控振荡器数据表

2021-05-25 12:00:10 2

2 集成2.2 GHz压控振荡器数据表的AD9517-2 12输出时钟发生器

2021-06-17 12:31:30 3

3 集成2.5 GHz压控振荡器数据表的AD9517-1 12输出时钟发生器

2021-06-17 15:57:38 6

6 时钟发生器AD9516-0技术手册

2022-01-25 15:59:42 7

7 Cypress时钟发生器应用在车辆、工业生产、消费品和网络服务的EMI降低和非EMI降低时钟发生器。 Cypress具有广泛的时钟发生器组合,兼容700MHz的频率和不超过0.7PS的RMS相位抖动

2022-04-22 09:02:09 806

806 这是带有板上芯片(COB)的1Hz时钟发生器电路。通常,为数字时钟和计数器电路应用产生1Hz时钟的电路将IC与晶体和微调电容器等结合使用。

2022-06-07 10:43:50 1886

1886

CY25200是一种具有扩频功能的可编程时钟发生器。扩频在小范围内调制输出时钟频率,扩展能量并降低能量峰值。这是一种在各种应用中降低EMI的强大技术。它使用外部参考时钟或晶体作为输入。它还使用PLL生成扩展频谱输出时钟,该时钟可以与输入频率不同。最多有六个输出时钟可用,其中两个可以是REFCLK。

2023-02-14 16:19:04 0

0 9ZXL1951D PCIe 时钟发生器评估板用户指南

2023-03-21 19:21:13 0

0 本文讨论电源噪声干扰对基于PLL的时钟发生器的影响,并介绍几种用于评估由此产生的确定性抖动(DJ)的测量技术。派生关系显示了如何使用频域杂散测量来评估时序抖动行为。实验室台架测试结果用于比较测量技术,并演示如何可靠地评估参考时钟发生器的电源噪声抑制(PSNR)性能。

2023-04-11 11:06:39 811

811

极景微发布超小封装PCIe5.0时钟发生器日前,极景微(UltraSilicon)宣布,推出两款支持PCIe5.0接口标准的1输出及2输出时钟发生器,分别为US6D101和US6D102。该芯片具有

2023-02-02 15:25:54 999

999

时钟发生器/PLL频率合成器SOP-82~15V2MHz封装:SOP-8

2022-08-19 15:57:46 3

3 时钟合成器和时钟发生器是两种用于产生时钟信号的电子器件,它们在功能和应用上有一些区别。

2023-11-09 10:26:56 298

298 的时钟发生器件的选择上往往少有考虑。目前市场上有性能属性大相径庭的众多时钟发生器。然而,如果不慎重考虑时钟发生器、相位噪声和抖动性能,数据转换器、动态范围和线性度性能可能受到严重的影响。...

2023-11-28 14:33:57 0

0

电子发烧友App

电子发烧友App

评论