在同步电路设计中,边沿检测是必不可少的!

例如:在一个时钟频率16MHz的同步串行总线接收电路里,串行总线波特率为1Mbps。在串行总线的发送端是在同步时钟(1MHz)的上升沿输出数据,在接收端在同步时钟的下降沿对输入数据进行接收采样。在这个接收电路里检测同步时钟的下降沿是必不可少的。假设主时钟-clk,同步时钟-rck,同步数据-data。

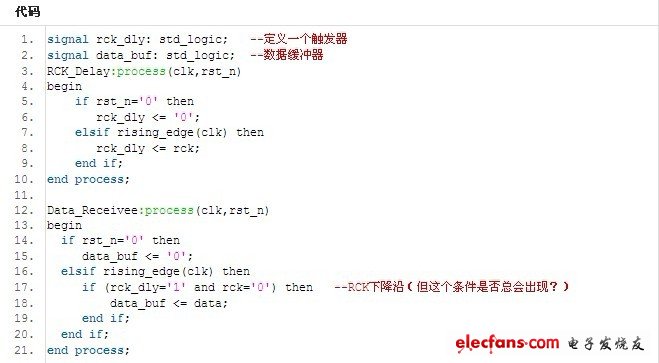

有些人在边沿检测的时候就喜欢这样做:

但是大家忽略了一种情况,就是clk与rck之间比没有必然的同步关系,当rck的下降沿刚好略滞后于clk的上升沿(大概几个ns),这样就会使高电平 保持时间不足,就会发现在本时钟上升沿时还是rck_dly=‘1’ and rck=‘1’,而在下一个时钟的上升沿来的时候,就会出现rck_dly=‘0’ and rck=‘0’,所以就不会有rck_dly=‘1’ and rck=‘0’的情况出现!! 从而导致丢失数据。

用户评论

共 0 条评论