由于半导体工艺进步,相同芯片面积中可以放入愈来愈多的晶体管,致使这10多年来业界开始积极发展所谓的系统单芯片SoC,而可组态性处理器IP概念就像自助餐式的自组拼盘,提供嵌入式系统更宽广的应用空间…

过往需多颗芯片才能组构的运算系统,现在透过半导体的整合工艺,单一SoC芯片即可实现,但无论是用多颗芯片构成的系统,还是用单颗芯片就实现的系统,系统中都包含各种属性、功效电路,而在SoC需求愈来愈普遍,同时内部设计愈形复杂后,芯片公司已难完全以自力、自主完成SoC设计,若完全自力设计,则电路的设计、验证过程费时更长,影响SoC上市时间与研发成本。

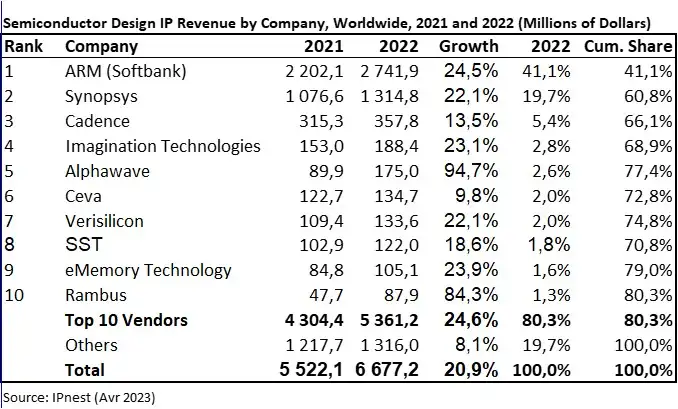

为能用更简便、快速方式完成SoC设计,半导体产业衍生新经营型态的公司,称为IP Provider(硅知识产权供货商),IP Provider只专注于芯片内各功效电路研发设计,并将功效电路设计成果授权给其它业者使用,而技术授权费或芯片量产后的权利金,就成了IP Provider的主要收益来源。

不过,并不是只有IP Provider才能授权芯片的功效电路设计,半导体产业中其它经营型态业者,也提供类似服务,包括整合装置制造商(IDM)、晶圆代工厂(Foundry)、无晶圆厂的芯片公司(Fabless)、芯片设计服务业者(Design House)、以及电路设计自动化的工具供货商(EDA Vendor)等也多有提供,差别只在于专营与兼营,IP Provider属专营业者,其余各种型态的业者属于兼营。

事实上硅知识产权概念最初来自Foundry,Foundry业者为让投单客户芯片电路设计可尽快投产,所以向客户提供现成、已完成各项验证的功效电路设计,当这类型的设计累积数量够多后,才逐渐开展出更高层次的硅知识产权产业。

处理器IP是SoC的最核心

了解IP能简化、加速SoC设计后。如今的SoC,芯片内多半会使用1个或1个以上的IP,在用及各种IP中,又以控制器、处理器的IP最为基础与关键。每颗SoC设计之初就要决定控制器/处理器架构,此等于决定SoC的最核心设计,接着才能决定外围功效电路,最后才能完成SoC整体设计。

也因为控制器/处理器的需求最基础、普遍,所以如英国ARM(安谋国际)、美国MIPS(美普思)等业者在硅知识产权业界中相当活跃,因为ARM、MIPS等皆以处理器的IP授权为主业务。今日多数SoC均直接使用ARM、MIPS业者授权的处理器IP,已少有完全自力设计的SoC执行核心。

图 英国ARC公司可组态性处理器IP的展望规划图(Roadmap),图上半年为ARC 700系列的展望规划,下半年则为600系列的展望规划。

Soft IP与Hard IP之别

虽然IP可以加速SoC设计,但进一步还要了解IP层次,大体而言IP可分成Soft IP与Hard IP 2个层次;Soft IP是偏向电路功效逻辑层面设计,而Hard IP则是除了具备电路功效逻辑外,连带已完成芯片实际投产前的实体性电路设计。

如果SoC业者期望对IP部分电路设计能有较高的再修改性,或者是更高度的电路设计整合,则必须选择Soft IP,反之Hard IP难以再修改,整合度也有限。不过Hard IP设计完成度较高,已经完成逻辑、实体2部分的设计,相对的Soft IP仅完成前期性的功效逻辑,所以就SoC整体设计的加速性而言,此方面Hard IP优于Soft IP。(附注2)

Soft IP的调修弹性仍有其限

所以,若为了追求较高的设计弹性,则必须选择Soft IP,但即便是Soft IP模式,其设计弹性也有限。以处理器IP来说,多数的处理器IP其处理架构均已经固定,如处理器内有多少个缓存器、管线阶数等,虽技术上依然可以对这些架构再行调修,但IP的授权业者通常不乐见、甚至不允许这么做,因为对架构进行调整将会阻碍执行软件的移植性与兼容性。

因此,提供处理器IP的业者,通常实行另一种作法,那就是提供多种型款(但各款的设计架构皆已固定)的处理器IP让客户选择,若客户认为某款的IP不合用,则可以再评估另一款IP,直到选定最贴近需求的款式为止。

可组态性处理器IP的意涵

用多种型款的现成固定式设计,来因应客户对处理器IP的各种不同需求,这是目前较普遍的作法,事实上ARM、MIPS、PowerPC等皆是如此。然而业界也有另一种作法,就是提供更高度的弹性设计,此称为可组态性处理器(Configurable Processor)。

可组态性处理器,是SoC设计者可以决定处理器的细节设计,包括增/减缓存器、执行单元、指令数...等设计,借以建构出更合乎需求的处理器核心。如此,可组态性处理器IP,提供更高度的设计弹性,目前以可组态性著称的处理器IP,主要有英国ARC公司的ARC 600、ARC 700核心,以及美国Tensilica公司的Xtensa 7、Xtensa LX2核心。

要注意的是,此类IP虽提供可组态性,但并不表示处理器内的任何环节都可重新调整,仍有其不变的主架构存在,倘若各环节都可以再行调修,此已等于是100%的自主设计,如此就没有向外取得IP授权的必要。

实行可组态性处理器IP的动机

前面提到,为了更高的设计弹性、为了更切合设计要求,所以需要可组态性处理器IP,但「弹性」、「要求」仍是相当浮泛的概念性形容,以下将更具体说明实行可组态性处理器IP的动机。

1.减少芯片电路面积

将原本的多芯片系统整合成SoC,为的就是要精省系统电路面积,同时也精省实现成本,不过要将原有的多芯片整合成单芯片,多半要对电路功效进行权衡取舍,甚至牺牲部分规格、性能、功效,所以设计时都会尽力缩小各功效电路面积,而可组态性处理器IP因具备更高弹性,能将「电路面积」视为第一要求,组态出占用面积最小的处理核心。

2.减少芯片的功耗用电

许多SoC是用于手持式应用装置中,手持式应用装置除力求芯片小体积化外,也相当讲究功耗用电,原因是手持装置的电池电力有限。此外能源成本愈来愈高,用于机房设备内的芯片也得讲究省电,其它各类应用芯片亦有类似趋势发展。因此,可组态性处理器IP在组态时,即能针对功耗用电进行最佳化设计。

3.增加芯片的运算效能、反应速率

能以电路面积来组态、能以功耗用电来组态,那么也可以从运算效能为取向来进行组态,尤其是硬性实时控制(Hard Real-Time Control)的应用格外有需求。事实上,一直以来处理器首要讲究的特性表现,是价格效能比(Price/Performance Ratio),近年来才开始重视功耗用电性的每瓦效能比(Performance Per Watt)。

4.减少芯片的授权成本

使用处理器IP要支付一笔技术授权费,且在SoC设计完成、投入量产后,还要针对每颗出厂后的SoC抽取量产权利金,为了减少授权费及权利金等成本支出,实行可组态作法有机会减少此方面的成本支出,例如不需要浮点运算单元则在组态设计时将可弃舍该单元,需要数字信号处理单元才放入该单元,透过逐项的权衡增减,有可能降低整体「技术授权费/量产权利金」成本。即便不能减少「技术授权费/量产权利金」成本,电路面积也可以获得精省,进而让芯片投产成本得到精省(与前述的第一项动机相近)。

5.针对SoC的应用进行最佳化

SoC的应用非常多,有的是数字相机(DSC)的SoC,有的是可携式媒体播放器(PMP)的SoC,或是导航机(PND)的SoC,不同的SoC其应用设计也不同,例如DSC SoC不重视音讯处理,而PND SoC只专注静态视讯处理及简易的音讯处理,但却需要重视数字信号的处理(接收卫星定位信号后的相关处理),至于PMP、STB(视讯机上盒)则重视动态、高质量的音/视讯处理,也重视信号处理(接收、处理节目信号)。

由上可知,不同的执行处理特性、不同的运算负荷度,若用单一架构处理器IP则难以满足设计,而可组态性处理器IP却可以针对不同的应用需求来进行组态,以合乎各种应用取向的SoC设计。

可组态性处理器IP的隐忧

虽可组态性处理器IP有如上的5种优点,但也不表示没有缺点,事实上,随半导体技术及市场演化,可组态性处理器也面临一些隐忧、威胁,以下我们简要讨论。

1.工艺持续缩密,芯片面积资源获得宽解

芯片的缩密工艺技术仍持续精进,从90nm、65nm、到45nm,并持续往下探,使芯片电路面积成本愈来愈低,因此芯片设计者已不如过往般重视面积成本,事实上处理器的多核化发展,无论是同质多核、异质多核,都表示「透过电路面积倍增的作法来争取效能提升」已属可行、值得。如此,透过组态作法让执行核心的面积最佳化,此种需求将逐渐减少。

2.芯片上市的时间压力愈来愈大

使用IP为的就是要节省芯片设计的验证心力、加速芯片的开发,让芯片更早上市销售,而今市场竞争更加激烈,芯片Time To Market压力比过去更大,使许多SoC项目都舍弃从Soft IP阶段开始设计,直接取用Hard IP加速设计。

然而可组态性处理器IP可说是比Soft IP更Soft(软)性的IP,是从「比Soft IP」更前期的设计阶段开始着手,好处是获得更高的设计弹性,但相对的就是增加SoC的设计时间,甚至为实现组态化而必须学习、熟悉另一套前期设计工具,即处理器的组态工具。

3.软件风险

此点前面已约略提及,事实上,除有软件移植性、兼容互通性等疑虑,软件的后续维护也将令人担忧,同时协力业者提供的宏程序(Macro)也可能无法立即适用,这些都须再行斟酌、调修。特别是软件开发、维护成本在整体SoC方案中所占的比重愈来愈高,许多原有以硬件电路方式设计成的功效,而今多半转成软件方式实现。

4.固定组态处理器IP的转向

ARM、MIPS等皆是以固定组态性处理器IP为主,不过为因应客户需求也开始有些转变,或允许部分的特例,例如MIPS的Pro系列IP就拥有组态性,或如ARM的OptimoDE Data Engines能因应不同需求的应用设计。

附注1:ARM、MIPS在处理器IP的主要授权业务逐渐成熟后,也开始进行相关延伸,如ARM延伸至实体IP领域,MIPS延伸到模拟/混讯IP领域,此外两家业者皆开始跨入32位的控制器IP市场。

附注2:除了Soft IP、Hard IP外也有Firm IP,Firm IP的设计完成度介于前两者之间,不过在产业的实际运用中却不如前两者普遍。

图 Tensilica Xtensa系列可组态性处理器IP的组态设计示意图,左上是勾核需求的功效项、特性项,例如需不需要硬件乘法器、桶式移位器等,右上则是延伸处理器架构,例如增加缓存器、增加VLIW数据路径等,左下则进行设计应用最佳化,右下则是软件自动化产生工具。

过往需多颗芯片才能组构的运算系统,现在透过半导体的整合工艺,单一SoC芯片即可实现,但无论是用多颗芯片构成的系统,还是用单颗芯片就实现的系统,系统中都包含各种属性、功效电路,而在SoC需求愈来愈普遍,同时内部设计愈形复杂后,芯片公司已难完全以自力、自主完成SoC设计,若完全自力设计,则电路的设计、验证过程费时更长,影响SoC上市时间与研发成本。

为能用更简便、快速方式完成SoC设计,半导体产业衍生新经营型态的公司,称为IP Provider(硅知识产权供货商),IP Provider只专注于芯片内各功效电路研发设计,并将功效电路设计成果授权给其它业者使用,而技术授权费或芯片量产后的权利金,就成了IP Provider的主要收益来源。

不过,并不是只有IP Provider才能授权芯片的功效电路设计,半导体产业中其它经营型态业者,也提供类似服务,包括整合装置制造商(IDM)、晶圆代工厂(Foundry)、无晶圆厂的芯片公司(Fabless)、芯片设计服务业者(Design House)、以及电路设计自动化的工具供货商(EDA Vendor)等也多有提供,差别只在于专营与兼营,IP Provider属专营业者,其余各种型态的业者属于兼营。

事实上硅知识产权概念最初来自Foundry,Foundry业者为让投单客户芯片电路设计可尽快投产,所以向客户提供现成、已完成各项验证的功效电路设计,当这类型的设计累积数量够多后,才逐渐开展出更高层次的硅知识产权产业。

处理器IP是SoC的最核心

了解IP能简化、加速SoC设计后。如今的SoC,芯片内多半会使用1个或1个以上的IP,在用及各种IP中,又以控制器、处理器的IP最为基础与关键。每颗SoC设计之初就要决定控制器/处理器架构,此等于决定SoC的最核心设计,接着才能决定外围功效电路,最后才能完成SoC整体设计。

也因为控制器/处理器的需求最基础、普遍,所以如英国ARM(安谋国际)、美国MIPS(美普思)等业者在硅知识产权业界中相当活跃,因为ARM、MIPS等皆以处理器的IP授权为主业务。今日多数SoC均直接使用ARM、MIPS业者授权的处理器IP,已少有完全自力设计的SoC执行核心。

图 英国ARC公司可组态性处理器IP的展望规划图(Roadmap),图上半年为ARC 700系列的展望规划,下半年则为600系列的展望规划。

Soft IP与Hard IP之别

虽然IP可以加速SoC设计,但进一步还要了解IP层次,大体而言IP可分成Soft IP与Hard IP 2个层次;Soft IP是偏向电路功效逻辑层面设计,而Hard IP则是除了具备电路功效逻辑外,连带已完成芯片实际投产前的实体性电路设计。

如果SoC业者期望对IP部分电路设计能有较高的再修改性,或者是更高度的电路设计整合,则必须选择Soft IP,反之Hard IP难以再修改,整合度也有限。不过Hard IP设计完成度较高,已经完成逻辑、实体2部分的设计,相对的Soft IP仅完成前期性的功效逻辑,所以就SoC整体设计的加速性而言,此方面Hard IP优于Soft IP。(附注2)

Soft IP的调修弹性仍有其限

所以,若为了追求较高的设计弹性,则必须选择Soft IP,但即便是Soft IP模式,其设计弹性也有限。以处理器IP来说,多数的处理器IP其处理架构均已经固定,如处理器内有多少个缓存器、管线阶数等,虽技术上依然可以对这些架构再行调修,但IP的授权业者通常不乐见、甚至不允许这么做,因为对架构进行调整将会阻碍执行软件的移植性与兼容性。

因此,提供处理器IP的业者,通常实行另一种作法,那就是提供多种型款(但各款的设计架构皆已固定)的处理器IP让客户选择,若客户认为某款的IP不合用,则可以再评估另一款IP,直到选定最贴近需求的款式为止。

可组态性处理器IP的意涵

用多种型款的现成固定式设计,来因应客户对处理器IP的各种不同需求,这是目前较普遍的作法,事实上ARM、MIPS、PowerPC等皆是如此。然而业界也有另一种作法,就是提供更高度的弹性设计,此称为可组态性处理器(Configurable Processor)。

可组态性处理器,是SoC设计者可以决定处理器的细节设计,包括增/减缓存器、执行单元、指令数...等设计,借以建构出更合乎需求的处理器核心。如此,可组态性处理器IP,提供更高度的设计弹性,目前以可组态性著称的处理器IP,主要有英国ARC公司的ARC 600、ARC 700核心,以及美国Tensilica公司的Xtensa 7、Xtensa LX2核心。

要注意的是,此类IP虽提供可组态性,但并不表示处理器内的任何环节都可重新调整,仍有其不变的主架构存在,倘若各环节都可以再行调修,此已等于是100%的自主设计,如此就没有向外取得IP授权的必要。

实行可组态性处理器IP的动机

前面提到,为了更高的设计弹性、为了更切合设计要求,所以需要可组态性处理器IP,但「弹性」、「要求」仍是相当浮泛的概念性形容,以下将更具体说明实行可组态性处理器IP的动机。

1.减少芯片电路面积

将原本的多芯片系统整合成SoC,为的就是要精省系统电路面积,同时也精省实现成本,不过要将原有的多芯片整合成单芯片,多半要对电路功效进行权衡取舍,甚至牺牲部分规格、性能、功效,所以设计时都会尽力缩小各功效电路面积,而可组态性处理器IP因具备更高弹性,能将「电路面积」视为第一要求,组态出占用面积最小的处理核心。

2.减少芯片的功耗用电

许多SoC是用于手持式应用装置中,手持式应用装置除力求芯片小体积化外,也相当讲究功耗用电,原因是手持装置的电池电力有限。此外能源成本愈来愈高,用于机房设备内的芯片也得讲究省电,其它各类应用芯片亦有类似趋势发展。因此,可组态性处理器IP在组态时,即能针对功耗用电进行最佳化设计。

3.增加芯片的运算效能、反应速率

能以电路面积来组态、能以功耗用电来组态,那么也可以从运算效能为取向来进行组态,尤其是硬性实时控制(Hard Real-Time Control)的应用格外有需求。事实上,一直以来处理器首要讲究的特性表现,是价格效能比(Price/Performance Ratio),近年来才开始重视功耗用电性的每瓦效能比(Performance Per Watt)。

4.减少芯片的授权成本

使用处理器IP要支付一笔技术授权费,且在SoC设计完成、投入量产后,还要针对每颗出厂后的SoC抽取量产权利金,为了减少授权费及权利金等成本支出,实行可组态作法有机会减少此方面的成本支出,例如不需要浮点运算单元则在组态设计时将可弃舍该单元,需要数字信号处理单元才放入该单元,透过逐项的权衡增减,有可能降低整体「技术授权费/量产权利金」成本。即便不能减少「技术授权费/量产权利金」成本,电路面积也可以获得精省,进而让芯片投产成本得到精省(与前述的第一项动机相近)。

5.针对SoC的应用进行最佳化

SoC的应用非常多,有的是数字相机(DSC)的SoC,有的是可携式媒体播放器(PMP)的SoC,或是导航机(PND)的SoC,不同的SoC其应用设计也不同,例如DSC SoC不重视音讯处理,而PND SoC只专注静态视讯处理及简易的音讯处理,但却需要重视数字信号的处理(接收卫星定位信号后的相关处理),至于PMP、STB(视讯机上盒)则重视动态、高质量的音/视讯处理,也重视信号处理(接收、处理节目信号)。

由上可知,不同的执行处理特性、不同的运算负荷度,若用单一架构处理器IP则难以满足设计,而可组态性处理器IP却可以针对不同的应用需求来进行组态,以合乎各种应用取向的SoC设计。

可组态性处理器IP的隐忧

虽可组态性处理器IP有如上的5种优点,但也不表示没有缺点,事实上,随半导体技术及市场演化,可组态性处理器也面临一些隐忧、威胁,以下我们简要讨论。

1.工艺持续缩密,芯片面积资源获得宽解

芯片的缩密工艺技术仍持续精进,从90nm、65nm、到45nm,并持续往下探,使芯片电路面积成本愈来愈低,因此芯片设计者已不如过往般重视面积成本,事实上处理器的多核化发展,无论是同质多核、异质多核,都表示「透过电路面积倍增的作法来争取效能提升」已属可行、值得。如此,透过组态作法让执行核心的面积最佳化,此种需求将逐渐减少。

2.芯片上市的时间压力愈来愈大

使用IP为的就是要节省芯片设计的验证心力、加速芯片的开发,让芯片更早上市销售,而今市场竞争更加激烈,芯片Time To Market压力比过去更大,使许多SoC项目都舍弃从Soft IP阶段开始设计,直接取用Hard IP加速设计。

然而可组态性处理器IP可说是比Soft IP更Soft(软)性的IP,是从「比Soft IP」更前期的设计阶段开始着手,好处是获得更高的设计弹性,但相对的就是增加SoC的设计时间,甚至为实现组态化而必须学习、熟悉另一套前期设计工具,即处理器的组态工具。

3.软件风险

此点前面已约略提及,事实上,除有软件移植性、兼容互通性等疑虑,软件的后续维护也将令人担忧,同时协力业者提供的宏程序(Macro)也可能无法立即适用,这些都须再行斟酌、调修。特别是软件开发、维护成本在整体SoC方案中所占的比重愈来愈高,许多原有以硬件电路方式设计成的功效,而今多半转成软件方式实现。

4.固定组态处理器IP的转向

ARM、MIPS等皆是以固定组态性处理器IP为主,不过为因应客户需求也开始有些转变,或允许部分的特例,例如MIPS的Pro系列IP就拥有组态性,或如ARM的OptimoDE Data Engines能因应不同需求的应用设计。

附注1:ARM、MIPS在处理器IP的主要授权业务逐渐成熟后,也开始进行相关延伸,如ARM延伸至实体IP领域,MIPS延伸到模拟/混讯IP领域,此外两家业者皆开始跨入32位的控制器IP市场。

附注2:除了Soft IP、Hard IP外也有Firm IP,Firm IP的设计完成度介于前两者之间,不过在产业的实际运用中却不如前两者普遍。

图 Tensilica Xtensa系列可组态性处理器IP的组态设计示意图,左上是勾核需求的功效项、特性项,例如需不需要硬件乘法器、桶式移位器等,右上则是延伸处理器架构,例如增加缓存器、增加VLIW数据路径等,左下则进行设计应用最佳化,右下则是软件自动化产生工具。

电子发烧友App

电子发烧友App

评论