介绍

最新的纳微GaNFast™ 电源集成电路NV6123/25/27,集成在6mmx8mm的QFN封装内。这个封装增加了一个大的冷却片,用于降低封装的热阻和提高散热性能。

这种封装使高密度电源的设计更加可靠,特别是对于没有气流的全封闭充电器和适配器应用中。能够充分利用这些热效益,就必须在PCB布局、热接口和散热,全部设计妥当。正确的热管理可以最大限度地提高使用GaN功率电路时的效率和功率密度。

本文介绍PCB布局指南和示例,以帮助设计师设计;提供NV612X(3/5/7)的封装图,供工程师朋友设计电源layout使用。

概述

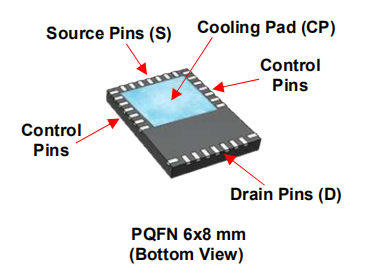

普遍的NV6113/15/17 GaN功率器件(QFN 5x6mm )设计在各种高密度PD电源。对于具有更具挑战性的热环境的设计,这个更大的QFN 6x8mm GaN功率器件产品能更有效地去除热量。新的6x8 mm QFN封装的集成电路引脚包括(见图1)漏极(D)、源极(S)、控制管脚和一个大的冷却片(CP)。

控制管脚栅极驱动和GaN功率FET的开/关控制,并且外部功率转换电路的大部分开关电流从漏极流过GaN功率FET,并流向源管脚。一小部分开关电流确实流过芯片的硅衬底,并通过衬底流出。在封装内部,集成电路直接安装在冷却片上。图2所示。

因此,GaN功率管的功率损耗产生的热量必须通过冷却片(CP)、焊料和PCB排出。图3所示;

尽可能多地使用铜来连接装焊接层增加散热面积是有帮助的。

使用热通孔将热量传递到PCB的另一侧或具有大铜平面的内层,然后在那里进行扩散和冷却。

冷却片连接到芯片基板,芯片基板可以相对于源极电平浮动+/-10V。

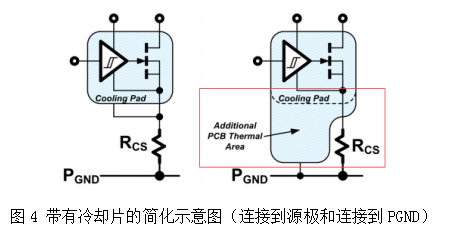

对于使用电流检测电阻的应用(CS采样),冷却片可以连接(图4)到源极引脚(在电流检测电阻RCS的顶部),或者连接到PGND以获得额外的PCB散热面积。

PCB指南(不带CS检测电阻)

在设计氮化镓GaN功率电路的PCB版图时,为了达到可接受的器件温度,必须遵循几个准则。

必须使用热通孔将热量从顶层IC焊盘传导到底层,并使用大面积铜进行PCB散热。

以下布局步骤和说明了最佳实践布局,以实现最佳的IC热性能。

1) 将GaN IC 6x8 mm QFN封装在PCB顶层。

2) 将控制所需的附加SMD部件放置在顶层(CVCC、CVDD、RDD、DZ)。将SMD部件尽可能靠近IC引脚!

3) 布置SMD部件、走线连接全部在顶层。

4) 在冷却片和侧边的顶层放置大片铜区域。

5) 在冷却片内部和侧边放置热通孔。

6) 在所有其他层(底部、mid1、mid2等)上放置较大的铜区域。

PCB指南(带CS检测电阻)

当使用放置在电源和PGND之间的电流检测电阻Rcs时,浮动冷却片允许PCB铜区延伸穿过电流检测电阻Rcs并直接连接到PGND。

当设计带有CS检测电阻的PCB时,应遵循以下步骤:

1) 将GaN IC 6x8 mm PQFN封装在PCB顶层。

2) 将控制所需的附加SMD部件放置在顶层(CVCC、CVDD、RDD、DZ)。将SMD部件尽可能靠近IC引脚!

3) 在顶层布置SMD组件、控制管脚、排水管脚和源管脚的连接。

4) 在冷却片和侧边的顶层放置大型铜区域。

5) 在冷却片内部和侧边放置热通孔。

6) 在所有其他层(底部、mid1、mid2等)上放置较大的铜区域。

7)用通孔将冷却垫铜区电位连接到PGND。

NV6125与NV6115热比较

在65w高频准谐振反激演示板上测试和比较了NV6125(6x8mm)和NV6115(5x6mm)的热性能。两个部分在相似的交流输入、直流输出和效率条件下进行了测试。通过遵循推荐的PCB布局指南,对两个GaN功率IC的PCB布局进行了优化。

结果表明,在低压AC 90V输入和满负荷条件下,NV6125在其外壳温度降低9.4摄氏度。

NV6125 vs NV6115 Thermal Comparison (65 W HFQR, Ta = 25 C)

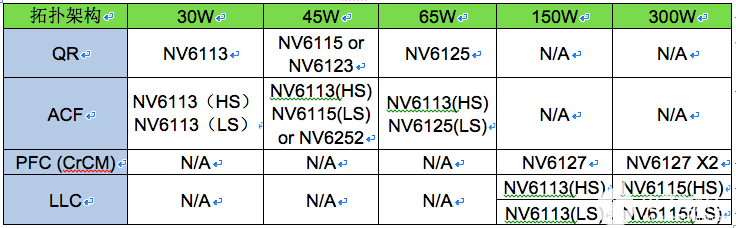

产品选择指南

下表显示了纳微针对不同电路拓扑和功率水平的GaN器件选型建议(仅限典型)。

-

功率器件

+关注

关注

41文章

1764浏览量

90431 -

氮化镓

+关注

关注

59文章

1631浏览量

116332 -

GaN

+关注

关注

19文章

1935浏览量

73372 -

热处理

+关注

关注

0文章

115浏览量

18236 -

功率半导体

+关注

关注

22文章

1154浏览量

42964

发布评论请先 登录

相关推荐

【基础知识】功率半导体器件的简介

什么是基于SiC和GaN的功率半导体器件?

基于GaNSense™技术的NV6169 PQFN 8×8 GaNFast™功率IC

关于NV612X GaNFast™ 功率半导体器件的热处理

纳微半导体发布第三代氮化镓平台NV6169功率芯片

纳微半导体发布采用GaNSense技术的 NV624x GaNFast半桥功率芯片

纳微半导体推出智能GaNFast氮化镓功率芯片

NV612X GaNFast™ 功率半导体器件的热处理

NV612X GaNFast™ 功率半导体器件的热处理

评论