Xilinx的SoC在业界应用非常广泛。对应的开发工具SDK也很成熟。在SDK里,每一个baremetal工程,对应一个BSP工程,它包含一些Xilinx提供的公共模块,比如硬件的驱动、freertos、LWIP等。在BSP工程的右键菜单中,选择BSP setting,可以配置BSP工程包含的的公共模块。

在Xilinx为异构计算打造的全新开发工具Vitis里,BSP被包含在Platform工程里。双击Platform工程里里的platform.spr,等界面初始化完成后,点击右边的“Modify BSP Settings”, 也可以配置BSP工程包含的的公共模块。点击“Reset BSP Source”, 可以生成BSP代码。

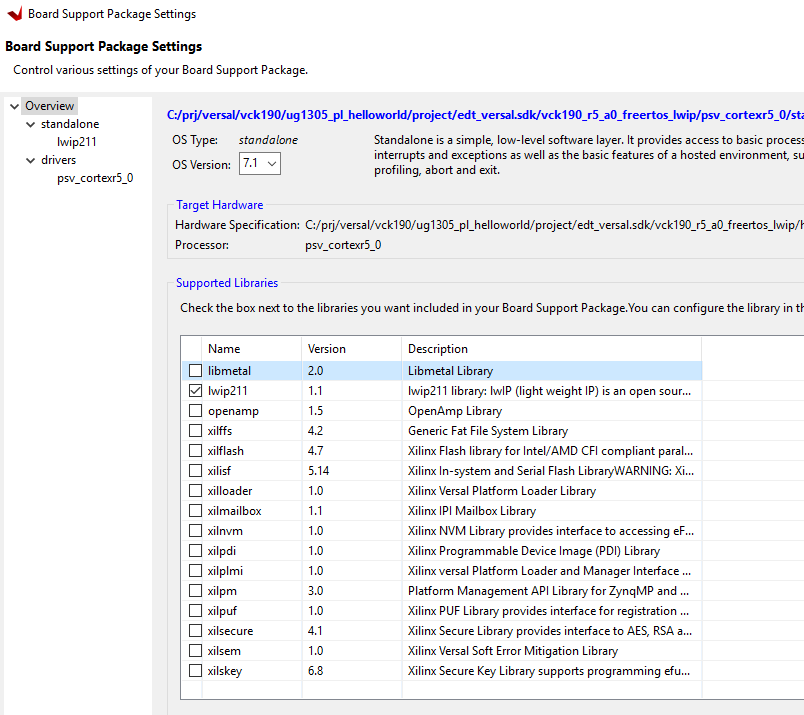

配置BSP工程的的公共模块的界面如下:

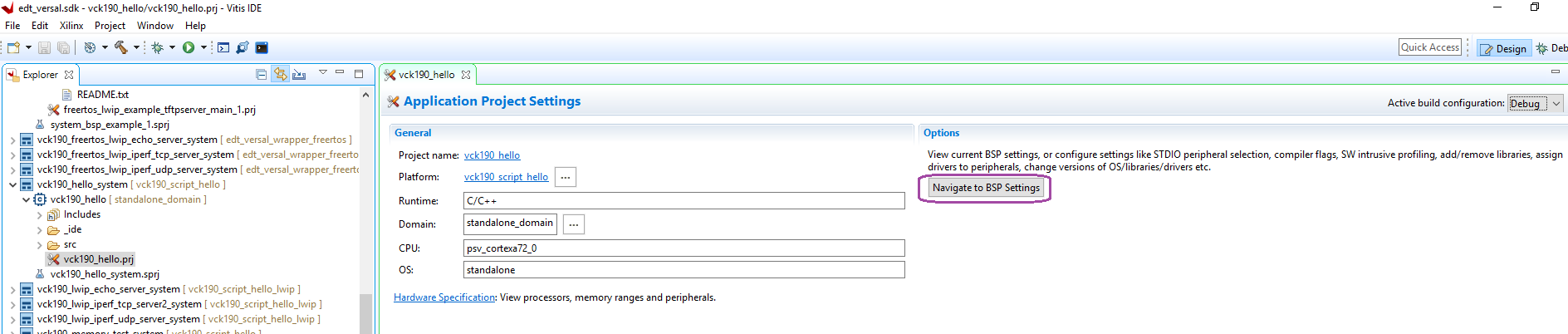

打开应用程序工程的prj文件,在右侧的"Navigate BSP settings", 也可以进入配置BSP的界面。

bsp的源代码,在Platform工程里的处理器子目录下的standalone_domain/bsp的目录里。比如,r5-0的lwip的代码目录是psv_cortexr5_0/standalone_domain/bsp/psv_cortexr5_0/libsrc/lwip211_v1_1/src/lwip-2.1.1/src。

-

soc

+关注

关注

38文章

4161浏览量

218164 -

Xilinx

+关注

关注

71文章

2167浏览量

121304 -

BSP

+关注

关注

1文章

87浏览量

26147

发布评论请先 登录

相关推荐

快使用yml看护主线bsp,让bsp维护更简单!

【RA-Eco-RA0E1-32PIN-V1.0开发板试用】使用 RASC 建立 Keil 工程、烧录测试

LORA模块的安装与配置指南

zynq7000 BSP无法在u-boot加载运行怎么解决?

zynq7000 BSP无法在u-boot加载运行,为什么?

公共 IP 地址前缀如何进行网络资源配置?

激活BT/BLE双模式配置文件时,可以使用相同的Mac地址(公共地址)吗?

想通过CYUSB3014配置xilinx FPGA,如何下载CYUSB3014的FPGA配置实用程序工具?

怎么在IAR中在一个工程里面配置不同的文件包含关系?

适用于 Xilinx® MPSoC 和 FPGA的可配置多轨PMU TPS650864数据表

适用于 Xilinx® MPSoC 和 FPGA 的可配置多轨PMU TPS650864数据表

AMD Xilinx 7系列FPGA的Multiboot多bit配置

Xilinx如何配置BSP工程包含的的公共模块

Xilinx如何配置BSP工程包含的的公共模块

评论