也许与此主题相关的最根本的问题是问为什么使用并行模块?将2个200A模块并联成一个400A模块有什么好处,为什么不简单地使用400A零件呢?在商业方面,在1200V级中,IGBT模块提供多种额定电流,并且封装的最大电流为3600A。

对于SiC MOSFET,更高电流(》 400A)时的选择受到更多限制,特别是在需要行业标准封装或多个电源的情况下。而且,与机械较大的较低产量的包装相比,通常可以以较低的成本生产大批量制造的物理较小的包装。

但是,并联模块的主要原因是技术原因,这些原因对于SiC MOSFET而言比对IGBT更为重要,原因如下:

多个封装可以散布在散热器上并改善冷却效果。这样可以从更昂贵的SiC MOSFET模块提供更多电流。

较大的物理封装由于机械间距以及用于承载较高电流的螺钉端子连接的使用,在电源回路和栅极驱动器电路中均具有较高的电感。

使用大量芯片会使所有芯片的内部对称布局和栅极电感均衡变得非常关键,并且很难使用具有有限端子选项的封装进行优化。

前两个点可实现更快的开关速度,因此使用这些较小的封装可实现更低的开关损耗和更低的关断期间电压过冲。

IGBT和SiC MOSFET之间的并联差异

经过仔细检查,尽管并联SiC MOSFET的开关速度很快,但与IGBT相比它们仍具有一些优势。

与Si IGBT VCE sat特性相比,SiC MOSFET通常具有更高的Rdson正温度系数。这在静态电流共享期间充当负反馈。如果一台设备消耗的电流更大,则增加芯片的Rdson值,从而减小电流。这种负反馈减少了热不平衡的程度。

Si IGBT的开关损耗随温度升高而大大增加,这对温度不平衡具有正反馈作用。较热的芯片具有较高的损耗,因此变得更热。SiC MOSFET的开关损耗随温度的增加非常小,大大降低了这种影响。

SiC MOSFET的跨导曲线更柔和,这意味着当在栅极阈值区域工作时,栅极电压的细微变化对漏极电流的影响要小于等效的Si IGBT。这有助于动态电流共享。

对英飞凌沟槽栅极器件的统计分析表明,就参数分布而言,具有较高RDS的模块具有较低的开关损耗,这有助于使损耗在部件之间匹配。

并行测试平台的经验我们将考虑此设计平台的多个方面。

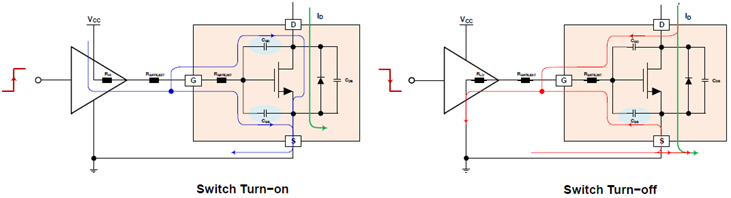

并联必须首先考虑模块内部电源和栅极布局。内部芯片布局和模块引脚布局可设计为为多个并行芯片提供相等且对称的电源和栅极驱动器布局。这是在保持低电感布局的开关环路电感的同时实现的。通常,基于PCB的模块样式的管脚网格阵列允许灵活地优化布局。

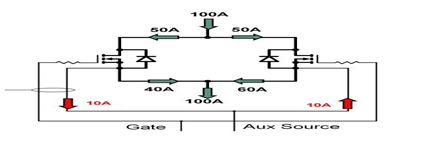

图1:具有公共辅助电源连接的电流路径

电源PCB布局

对于电源布局,该模块分为两个对称的两半。为了与这种对称性相匹配,将电源布局制成像蝴蝶翅膀一样沿着中心线向下镜像的镜像。这是保持模块内部芯片之间相等的电流共享所必需的。四个模块中的每个模块均使用了精确的布局传真,以使模块之间的电流共享相等。保持外部开关环路电感低也很重要,这可以通过将DC +和DC-总线连接与多个PCB铜层重叠并使用本地去耦电容器来实现。

栅极驱动器电路设计

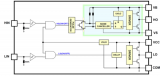

当对具有多个栅极连接的所有4个模块使用公共栅极驱动器电路时,重要的是减少在辅助源极连接中流动的任何电流。图1以两个模块的简化示例显示了辅助电源连接如何向主电流路径提供自然的并联传导路径。我们称其为“青少年电子”的某些电子,因为它们喜欢采取不同于其他所有人的路径,因此可以在此辅助源平行路径中流动。该电流可能足够大,以引起栅极振荡,甚至使模块内部辅助键合线熔断。

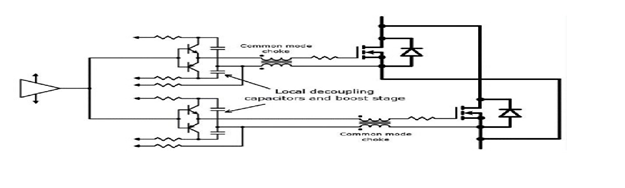

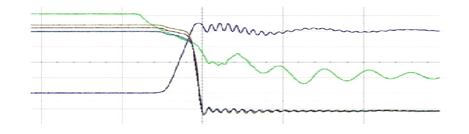

图2所示的电路用于减少这些有害的循环电流。它是共模扼流圈的组合,对流入和流出电流相等的正常栅极电流显示低阻抗,而对仅在源极连接中流动的不想要的源电流显示高阻抗。除此之外,每对设备栅极连接均使用单独的局部升压级。这允许在源极连接中产生电阻,但是使用本地电容器时,在该路径中流动的任何电流都不会影响栅极波形。如果仅使用简单的源极电阻,则情况并非如此,因为流入该源极电阻的任何电流都会影响栅极源极电压,从而降低直接控制的电平并增加栅极振荡的可能性。

图2:栅极驱动器电路

栅极驱动器PCB布局

6mΩ模块具有双栅极源极引脚以及双电源漏极和源极连接点,以降低电感并改善模块内部SiC MOSFET芯片之间的电流共享。栅极布局的第一个挑战是使两对栅极源极连接都具有对称的布局。

之后,关键是同时打开和关闭所有四个模块的门。“树”结构通过具有相似长度的低电感走线栅极/源极对实现了这一目标。同样对于每对栅极源极连接的局部升压级,布局也是对称的。测量显示,更糟的情况是,在切换期间门之间的时序偏斜小于5nS。

仪器仪表

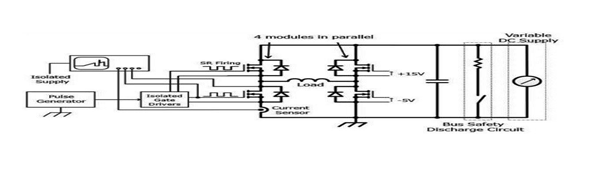

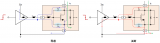

图3显示了用于双脉冲测试(DPT)的示意图。使用拓扑结构作为H桥来测量电流共享很重要,这样电流和磁场才能匹配最终应用。此外,还要求具有为被测互补器件产生同步整流器开关脉冲的能力,且其死区时间满足系统死区时间要求。

图3:双脉冲测试(DPT)原理图

为了测量漏极和源极电流,直流总线PCB走线的两侧都带有孔,以允许使用Rogowski线圈。这些功能允许测量DCbus中的电流(即下部开关的源电流)和DC +总线电流(即上部设备的漏极电流)。还留出了余地,以便能够测量两组模块输出引脚之间的输出电流平衡

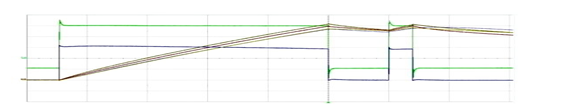

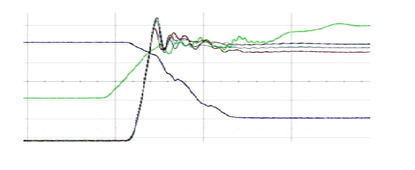

图4:4个并联模块的DPT电流波形(50 µs /格和50 A /格)绿色Vgs 5 V /格。蓝色Vds 100V /分区

图5:4个并联模块的DPT电流波形(50 µs /格和50 A /格)

静态电流共享

图4显示了在DPT期间四个下部器件中的源电流。在空载时间之后,在第一个脉冲之后使用同步整流打开上侧SiC MOSFET。但不是在第二个脉冲之后,第二个脉冲允许电流通过上体二极管空转。四个匹配模块的电流共享为+/- 3%。请注意,当MOSFET未选通且仅体二极管导通电流时,在第二个脉冲之后,电流共享变得更糟。

图6:4个并联模块的DPT关断波形(200 ns /格和50 A /格)绿色Vgs 5 V /格。蓝色Vds 100V /分区

图7:4个并联模块的DPT开启波形(200 ns /格和50 A /格)绿色Vgs 5 V /格。蓝色Vds 100V /分区

最初的测试是使用RDS偏差小于2%的模块进行的。还对RDS为7%的模块进行了测试,而共享仅在+/- 4%时稍差。在高温下进行的其他测试以及切换上部设备均显示出同样出色的性能。图5是图4中电流波形的放大图。

实验室中的当前共享与大批量生产

因此,在实验室中以很小的样本就显示出了出色的均流性能。但是,如果必须将此设计转换为大批量的商业产品,则必须计算出随机选择的模块及其电参数的正态分布的电流共享。用于此的方法称为蒙特卡洛分析,以蒙特卡洛著名的赌场命名。从RDS的统计生产分布和开关损耗值中选择一组四个模块(每个模块一个)。使用每个模块的这些参数,可以计算每个模块中的电流并估算结温。由于RDS的导通和开关损耗取决于温度,因此使用迭代来计算每个模块的最终电流和结温。可以重复这个过程,例如说50,000组随机选择的模块并计算Tj的归一化分布。在这种情况下,结果是在+/- 7 +/- +/- 3 sigma的变化。计算中的另一个难题是RDS导通与开关损耗Etot之间存在互相关性,其中RDS导通较低的零件趋向于更高的Etot值。

编辑:hfy

-

英飞凌

+关注

关注

67文章

2248浏览量

139429 -

散热器

+关注

关注

2文章

1065浏览量

37905 -

IGBT

+关注

关注

1270文章

3865浏览量

250920 -

栅极驱动器

+关注

关注

8文章

778浏览量

39157

发布评论请先 登录

相关推荐

栅极驱动器的定义和结构

SiC MOSFET如何选择栅极驱动器

电隔离栅极驱动器选型指南

使用隔离式 IGBT 和 SiC 栅极驱动器的 HEV/EV 牵引逆变器设计指南

栅极驱动器是什么?栅极驱动器有什么用?

什么是栅极驱动器?栅极驱动器的工作原理

Littelfuse发布IX4352NE低侧SiC MOSFET和IGBT栅极驱动器

Littelfuse宣布推出IX4352NE低侧SiC MOSFET和IGBT栅极驱动器

用于SiC MOSFET和高功率IGBT的IX4352NE低侧栅极驱动器

PMP30629.1-具有集成开关PSR反激式转换器的隔离式2.5W SiC和IGBT栅极驱动器 PCB layout 设计

用于IGBT和MOSFET的5.7 kVRMS增强型隔离栅极驱动器ISO5852S数据表

用于IGBT和MOSFET的 5.7 kVRMS 增强型隔离栅极驱动器ISO5452数据表

IGBT和SiC MOSFET差异 栅极驱动器电路设计

IGBT和SiC MOSFET差异 栅极驱动器电路设计

评论