1 YCbCr颜色空间

YCbCr颜色空间是YUV颜色空间的缩放和偏移版本。Y定义为8bit,标称颜色范围为16-235;Cb和Cr标称颜色表示范围为16-240。YCbCr的采样格式一般有44、42、41、和40。

1.1 44 YCbCr格式

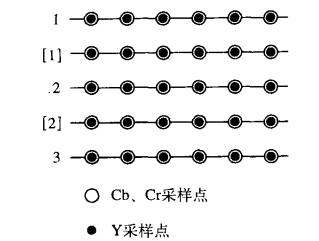

图1表示44格式YCbCr采样点的定位。每个采样点有Y、Cb和Cr值,每个颜色值的颜色分量为8bit(典型),因此每个采样点24bit。

图1 44采样

1.2 42 YCbCr格式

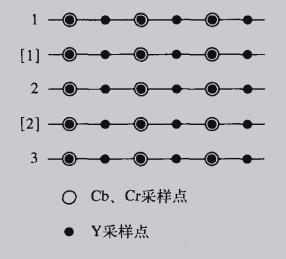

图 2表示42格式YCbCr采样点定位。对于每两个水平Y采样点,有一个Cb和一个Cr采样点。

图2 42协调位置采样

2 matlab YCbCr444转YCbCr422

首先将rgb图像转为YCbCr444然后再由YCbCr444转为YCbCr422。

close all clear all clc I=imread('1.bmp'); [H ,W ,D]=size(I); R=double(I(:,:,1)); G=double(I(:,:,2)); B=double(I(:,:,3)); Y0= double(zeros(H,W)); Cb0 =double(zeros(H,W)); Cr0 = double(zeros(H,W)); Cb1 =double(zeros(H,W/2)); Cr1 = double(zeros(H,W/2)); CbCr = double(zeros(H,W)); %RGB转YCbCr444 for i = 1:H for j = 1:W Y0(i, j) = 0.299*R(i, j) + 0.587*G(i, j) + 0.114*B(i, j); Cb0(i, j) = -0.172*R(i, j) - 0.339*G(i, j) + 0.511*B(i, j) + 128; Cr0(i, j) = 0.511*R(i, j) - 0.428*G(i, j) - 0.083*B(i, j) + 128; end end for i=1:1:H for j=2:2:W Cb1(i,j/2)=(Cb0(i,j-1)+Cb0(i,j))/2; end end for i=1:1:H for j=2:2:W Cr1(i,j/2)=(Cr0(i,j-1)+Cr0(i,j))/2; end end for i=1:1:H for j=1:1:W if rem(j,2)==0 CbCr(i,j)=Cr1(i,j/2); else CbCr(i,j)=Cb1(i,(j+1)/2); end end end Iycbcr(:,:,1)=Y0; Iycbcr(:,:,2)=Cb0; Iycbcr(:,:,3)=Cr0; Iycbcr=uint8(Iycbcr); Y0=uint8(Y0); Cb0=uint8(Cb0); Cr0=uint8(Cr0); Cb1=uint8(Cb1); Cr1=uint8(Cr1); CbCr=uint8(CbCr); figure(1), subplot(211),imshow(I),title('RGB'); subplot(212),imshow(Iycbcr),title('YCbCr444'); figure(2), subplot(221),imshow(Cb1),title('Cb1'); subplot(222),imshow(Cr1),title('Cr1'); subplot(223),imshow(Cb0),title('Cb0'); subplot(224),imshow(Cr0),title('Cr0'); figure(3), subplot(211),imshow(Y0),title('Y0'); subplot(212),imshow(CbCr),title('CbCr');

Cb2和Cr2

CbCr交错显示

`timescale 1ns/1ps module YUV444_422 ( input clk, input rst_n, input iVsync, input iHsync, input iDVAL, input[23:0] YUV444_D, output reg oVsync, output reg oHsync, output reg oDVAL, output reg[15:0] YUV422_D ); reg iDVAL_reg0,iDVAL_reg1,iDVAL_reg2,iDVAL_reg3; reg iVsync_reg0,iVsync_reg1,iVsync_reg2,iVsync_reg3; reg iHsync_reg0,iHsync_reg1,iHsync_reg2,iHsync_reg3; reg[8:0] YUV444_Cr_Sum0; reg[8:0] YUV444_Cb_Sum0; wire [7:0] temp_Y,temp_Cb,temp_Cr; reg [7:0] temp_Y0,temp_Y1,temp_Y2,temp_Y3; reg [7:0] temp_Cb0,temp_Cb1; reg [7:0] temp_Cr0,temp_Cr1; reg[7:0] Cr,Cb,Crbuf; reg Sel; assign temp_Y=YUV444_D[23:16]; assign temp_Cb=YUV444_D[15:8]; assign temp_Cr=YUV444_D[7:0]; always@(posedge clk) begin iDVAL_reg0 <= iDVAL; iDVAL_reg1 <= iDVAL_reg0; iDVAL_reg2 <= iDVAL_reg1; iDVAL_reg3 <= iDVAL_reg2; oDVAL <= iDVAL_reg3; end always@(posedge clk ) begin iVsync_reg0 <= iVsync; iVsync_reg1 <= iVsync_reg0; iVsync_reg2 <= iVsync_reg1; iVsync_reg3 <= iVsync_reg2; oVsync <= iVsync_reg3; end always@(posedge clk) begin iHsync_reg0 <= iHsync; iHsync_reg1 <= iHsync_reg0; iHsync_reg2 <= iHsync_reg1; iHsync_reg3 <= iHsync_reg2; oHsync <= iHsync_reg3; end always@(posedge clk ) begin //delay 3 clock Y temp_Y0<=temp_Y; temp_Y1<=temp_Y0; temp_Y2<=temp_Y1; temp_Y3<=temp_Y2; //delay 2 clock Cb temp_Cb0<=temp_Cb; temp_Cb1<=temp_Cb0; //delay 2 clock Cr temp_Cr0<=temp_Cr; temp_Cr1<=temp_Cr0; //delay 1 clock YUV444_Cr_Sum0 <= temp_Cr1 + temp_Cr0;//cr0+cr1 YUV444_Cb_Sum0 <= temp_Cb1 + temp_Cb0;//cb0+cb1 //delay 2clock Cr <= YUV444_Cr_Sum0[8:1]; Cb <= YUV444_Cb_Sum0[8:1]; end always@(posedge clk or negedge rst_n) begin if(~rst_n) Sel <= 1'b0; else if(iDVAL_reg3) Sel <= ~Sel; else Sel <= 1'b0; end always@(posedge clk or negedge rst_n)begin if(~rst_n) YUV422_D <= 16'd0; else if(iDVAL_reg3) begin YUV422_D[15:8] <= temp_Y3; YUV422_D[7:0] <=(!Sel)?Cb:Crbuf; Crbuf <= Cr; end end endmodule

fpga实现CbCr22

责任编辑:xj

原文标题:YCbCr444转YCbCr422

文章出处:【微信公众号:FPGA开源工作室】欢迎添加关注!文章转载请注明出处。

-

YCB

+关注

关注

0文章

2浏览量

7834 -

颜色空间

+关注

关注

0文章

3浏览量

1468

原文标题:YCbCr444转YCbCr422

文章出处:【微信号:leezym0317,微信公众号:FPGA开源工作室】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

如何使用MATLAB实现一维时间卷积网络

OptiSystem应用:用MATLAB组件实现振幅调制

TSH8135的三组数据线输入,分别对应的RGB的数据?还是需要转换成YCbCr信号?

typec转hdmi 10k60hz转换方案/typec音视频转换方案/CS5569设计方案

TVP7002 YCBCR422 embedded SYC输出,对接HI3520D BT1120口的疑问求解

基于TDA处理器的360度全景实现YUV422输出的方案

利用Matlab函数实现深度学习算法

MATLAB如何使用训练好的网络

一款通用的USB转RS-485/422转换器DAM-3232N

国产SR-422收发器的作用有哪些?

422转232转接器异常

将YCbCr转换成RGB565,并丢到显示RAM中去,为什么显示的图像不对?

CS5802专用HDMI转Type-C转换控制芯片方案

3.3YPbPr/YCbCr接口静电浪涌保护方案介绍

实现matlab YCbCr444转YCbCr422实例

实现matlab YCbCr444转YCbCr422实例

评论