1 引言

为适应摩尔定律的突飞猛进,微电子封装技术日新月异,高密度先进封装技术中的多芯片封装MCP、系统级封装SIP或SOP、多芯片组件MCM、板上芯片COB、芯片直接焊接系统DCA、可更换芯片组件RCM、层叠式管芯组装、分立器件复合化(阵列化)等封装成为发展热点,封装与芯片制造同等重要。另一方面,芯片厂商始终与封装业密切合作,探索各种工艺流程及方法,提高产品质量,经多年理论研究与实践,认识到真正决定其质量和可靠性的因素是生产过程中的管理方法、技术途径,确保IC产品所要的性能持续转移延伸人封装业,确保芯片所具有的最佳性能和可靠性沿IC产业链传递至最终客户。确好芯片KGD(Known Good Die)就是在这一发展理念基础上产生的,芯片厂商整合老化筛选资源,从高端寻找市场突破口,将与前工序生产有关的失效、缺陷隐患的芯片(芯粒、籽芯、管芯)及早剔除在封装之前,满足高密度多芯片封装减少生产费用与时间,促进产品尽快上市的要求。在翻阅文献资料过程中,有幸接触到KGD方面的部分内容,通过进一步查询、比较、归纳相关资料,将评述如下。

2 KGD发展内涵

封装是对芯片提供物理保护,芯片是封装的精髓灵魂,只有芯片本无缺陷,正本清源,才能达到封装的目的,展现IC极限(最优)性能。就当前国内外实际情况而言,封装厂家所需芯片来源是从各芯片厂商购人,特别是那些国内现阶段无法生产的电路芯片,还要进行多渠道全球采购,无论从哪种方式购人的芯片,其质量好坏主要是通过批次验收或者通过选定级别的检测来确定,芯片的可靠性与半导体工艺的成熟程度有很大关系,大部分是芯片生产厂家在25℃下只做功能特性测试,有的称为中测或初测、半成品测试,国外称其为探针测试芯片PD(Probed Die),挑选参数指标基本合格的芯片,但其性能并不稳定,未完全测试芯片对封装后的可靠性影响非常大。另有一类芯片与已封装产品一样做全功能测试,称之为全测试芯片KTD(Known Tested Die),其质量和可靠性仍无法完全保障,最终的封装成品率受到一定影响。随着封装中芯片数量的增加,尤其在MCP、SIP、MCM、混合IC内部,由大量的多个芯片合而为一,若任何一个芯片有缺陷,都意味着整个产品不合格,给返修率、成品率、研制费用、生产周期造成直接影响。

高密度多芯片封装的发展促进了采用更新、更快、更小芯片的市场需求,这从根本上与依靠芯片生产工艺成熟性来提供高品质水平和可靠性的芯片制造策略相矛盾。为解决这一问题,国外一些厂家提出KGD概念,意思是已确认的好芯片,或称为被确认的优质芯片,已知良好芯片,信得过芯片,其定义是与等效的封装器件具有相同质量和可靠性的芯片,通过对芯片在线功能测试、老化筛选、参数测试,使芯片在性能、质量、可靠性指标上达到封装产品的等级要求。

KGD已成为一种涉及IC产业链中大部分参与者,并相互联系在一起的技术,芯片与封装协同,采用试验方法提供与封装IC水平相当的KGD,确保封装性能指标,在高密度多芯片封装的设计及应用中的重要作用凸显。

3 KGD技术研发动向

从芯片发展到KGD是一个在已制作完成电路图形的晶片的直接老化筛选、测试的工艺流程,所选测试系统必须很容易地适用于自动化,能与原有设备一道兼容使用,在筛选、测试工序达到与封装产品一样性能所要求的规范值,在恶劣环境下的可重复性。测试方法通常涉及到临时的,可重复使用的测试载体及夹具的设计制作,确保测试工序本身不对芯片产生任何功能性的伤害,用于筛选、测试系统的互连也必须确保无任何损伤诱发,以建立一个更为全面、综合的在线KGD测试系统,适应封装业对芯片高品质要求。

在国外,美国航空航天局NASA为满足空间技术对MCM的要求,率先提出采用KGD方法,制定出KGD保证计划,KGD的测试与可靠性是保证空间应用微波MCM的关键技术之一,并制定空间应用KGD保证技术导则。美国政府1994年拿出l亿美元资金,组织多个厂家对KGD的处理、芯片供给的质量保证、MCM用芯片的标准和试验方法等进行研究。美国电子工业协会(EIA)在1996年制订了有关KGD的“EIA/JESD—49—1996 Procurement Standard Of Known Good Die(KGD)”标准,美国半导体工业协会SIA的KGD技术研究计划的最终目标是要在2010年左右,完全实现在晶片阶段进行IC的电测试和老化筛选,从而真正保证MCM用芯片的质量和成品率。日本厂家追随美国开发KGD技术,日本电子工业协会(EIAJ)在1999年制订出EIAJ/EDR—4073—1999 Quality Assurance Guide Lines for Bare Die including KGD”标准,欧洲于2000年制订针对KGD的ES59008标准。对KGD质量和可靠性保证提出指导性规范,资源配置上标准共享,有助于扩大芯片供应商及封装合作伙伴的选择,生产适合各行业市场,并被客户接受的产品,促进产业升级和技术进步。技术标准化也一直受到各生产厂商的普遍关注,标准是组织生产的技术纲领、规范和依据,深入开展KGD工作的保证,根据宇航用、军用、工业用、商业用等相应的质量级别和要求,制定出不同的KGD生产流程和判定数据,确保产品质量,降低成本,提高市场竞争力。

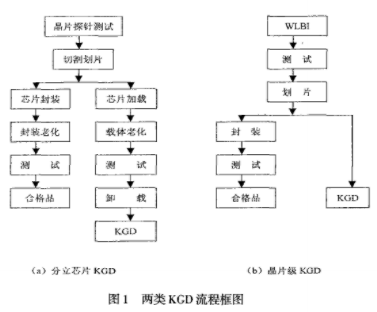

KGD的工艺流程分为两种情况,如图1所示,其一是在分立芯片阶段进行的KGD技术,即已制作电路图形晶片经切割划片后,直接对单个芯片进行临时封装的加载、老化、测试、卸载,获得KGD,其特点为临时封装的载体夹具使用灵活,适合批量不大的高可靠产品;另一种是晶片级KGD技术,采用损耗金属(Sacrificial Metal)的晶片级老化WLBI,所谓的损耗金属就是在WLBI与测试期间,暂时为芯片提供电气通道的金属,这种金属在完成老化筛选与测试之后被刻蚀去掉。WLBI与晶片级可靠性WLR(Wafer Level Reliability)技术十分相似,无须封装,热阻较低,可采用较高的温度、较大的电流密度老化筛选而不致于引入新的失效机理。WLBI测试系统费用较高,适合大批量生产,在有足够的需求批量条件下采用。

美国和欧洲有与KGD技术相关的两个重要国际会议,即“KGD Packaging and Test Workshop”与“The GOOD-DIE International Workshop”,报道KGD技术研发进展。目前,海外有多家公司商品化生产KGD加载/卸载装置及夹具,加载/卸载避免对芯片引入损伤,夹具可重复使用。一些顶级半导体厂商开发KGD技术,例如,德州仪器的Die Mate技术,英特尔的Smart Die生产线专用于研发KGD,Micro-ASI公司的Si-Star KGD测试系统,AEHR公司的Die PAC,IBM微电子部、摩托罗拉、微技术、国家半导体、日本松下,冲电气等公司关注KGD,生产扩展到一个较宽范围的芯片种类及型号系列。KGD的不足是其成本为封装产品的0.7-1.5倍,微波KGD则更高,生产周期加长,交货时间滞后,在这些方面不易被普遍接受,国外正试图开发低成本的测试载体,夹具、测试仪器来改变这种局面,扩大市场范围,市场是KGD发展最直接的驱动力。

4 KGD工艺流程

KGD的成功之道是使芯片的性能和可靠性达到同类封装IC产品的水平,将老化筛选整合到芯片生产线,被业界认为是高可靠芯片的重要解决方案,有利于提高多芯片封装的成品率及可靠性,尤其受到不太计较价格因素的航天/军用领域的选用,应用拉动发展。

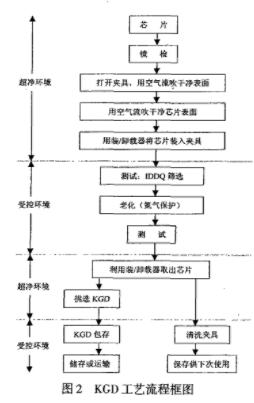

KGD工艺流程与芯片老化筛选技术息息相关,必须经历IC封装相类似的筛选过程,图2示出KGD主要工艺流程,整个工艺流程中均需要进行静电泄漏ESD保护,完成每道工艺均依据相关的技术文件进行。芯片加载/卸载载体及其系统是无损检测、老化筛选的关键,芯片安装在临时载体的夹具中如同在封装外壳内一样,完成老化筛选、测试出KGD。临时性芯片载体系统一般包括临时、可重复使用的夹具,带特定互连的基板,特殊设计的插座以及老化测试板。整个载体适用于带接触焊盘的芯片和带凸点芯片,接触焊盘和凸点可以是四周排布,也可以是阵列形式的。电连接金属凸点对质量要求较高,要弹性大,耐疲劳,抗腐蚀。夹具的主要功能是提供承载芯片和基板的机械支撑,以及测试接触接口,夹具包含基座、可选择的阵列片来排列芯片和衬底,悬盖和压板对芯片提供一定的压力,弹锁锁定悬盖等几个部分。

Si-star的KGD测试系统的灵活性使得单个芯片测试的自动化成为可能,它由导电聚脂凸点粘附有导电聚酯凸点的陶瓷基板(用来与单个芯片相接触)、拾片头,用于完成高低温试验的热电致冷器TEC组成,将芯片置入一个临时载体的夹具中,然后连同载体一起进行老化、测试,最后取出芯片,淘汰掉功能、参数不合格品。

DieMate测试系统的临时性可重复使用的封壳载体从上至下可分解为盖子、被测芯片、一体化的基板夹具、老化测试座等几大部分,盖子带有一个旋转式锁定机构,芯片通过封壳载体接受老化筛选。每个芯片在基板上的定位精确度必须达到微米级,由加载/卸载器的拾取可视对准系统完成,专用的特别放置吸嘴在运行中能很好地吸持住芯片。

目前,生产的大多数KGD都采用晶片检验阶段的试验方法,提供客户所需要的质量和可靠性服务,试验方法包括增强的电压筛选和ID DQ以及晶片级的温度试验,试验方法上有共同点,也有和生产线相关的差异,例如,汽车应用中的KGD测试,采用KGD的倒装芯片,在线KGD测试技术。为降低KGD的成本,积极开发晶片级的KGD保障技术,建立一种大规模、多批量连续生产模式。

5 KGD的应用

在激烈的市场竞争中,芯片厂商千方百计生产出满足客户需求的各类芯片,攻占市场,扩大占有率。KGD的性价比是客户首先考虑的问题,必须达到客户认为合理,可接受的范围,否则就伞选择成品筛选的非KGD之路。

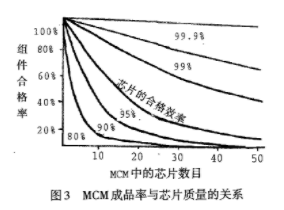

MCM是高密度多芯片封装中发展之最,它将多个芯片与其他片式元器件组装在同一块多层互连基板上,然后封装在一个外壳内。目前普遍采用的2D—MCM的组装效率达85%以上,发展到利用三维(X、Y、Z方向)结构形式,对多芯片和元器件进行组装的3D-MCM,其效率达200%。KGD在MCM研制中具有举足轻重的作用,直接决定MCM研发水平及产品技术性能,可缩短研发周期,降低制作成本。随着3D-MCM中芯片品种数目、数量的增加,更能体现KGD提高产品合格率的作用及价值。例如,一个系统被设计成带有12个电路芯片的MCM,假设其优质品的概率全部是95%,那么该MCM合格的概率就等于0.95的12次幂,即合格率降为54%,这样的结果导致大约两个MCM就有一个需要返修、重做,生产成本会增加。图3示出MCM的成品率与芯片质量的关系,当采用KGD后,其合格率将大大提高,对航天/军用电子整机、超级巨型和大型计算机、工作站、通信产品、汽车电子等产生重大影响。

航天/军用微波MCM中大量采用单片微波集成电路MMIC芯片,通常使用共晶焊接和环氧导电胶粘接方法,分别将大功率MMIC芯片焊接以及小信号MMIC芯片粘接到多层互连基板上,为保证焊、粘接所用MMIC芯片质量,可用HP8510C矢量网络分析仪、CASCADE公司的微波探针测试台和共面波导微探针组成测试系统,对MMIC芯片进行无损芯片的电性能参数测试。测试时先在一个阻抗标准基板ISS上进行传输—反射—匹配校准,然后用真空拾取器将被测MMIC芯片放置于测试平台上的真空吸口位置,打开测试平台侧面的真空开关,使被测MMIC芯片吸附在测试平台上,分别调节定位器上的X-Y-Z三个方向的定位旋钮,将射频探针和直流探针的探头接触到被测MMIC芯片相应的焊盘上,根据测试条件在直流探针端接人馈电电源,在HP8510C矢量网络分析仪上进行MMIC芯片性能参数的测量与数据读取,据此剔除不合格品。最后进行互连、封装、试验验证,在没有批量或批量不大时,总会筛选出一些满足要求的微波MCM产品。微波MCM的技术难度大,要求高,并非一般低频和数字电路封装可替代的。

混合集成电路将功率器件、驱动电路、控制电路、保护电路、阻容及磁性元件封装到一个集成模块内部,构成一个功能相对完整的,具有一定通用性的组件,KGD也是其中很关键的芯片,有不同的方案。例如,控制和驱动电路采用商品化元器件,而功率器件采用未封装芯片或KGD,需要解决芯片的安装、散热、布线、结构以及强弱电之间的电热隔离所有器件均采用未封装的芯片或KGD,通过多层布线和互连一次封装,表成—个功能模块或功率模块。

KGD技术日渐成熟起来,通过功能测试、老化筛选、电参数测试、温度检测试验,在技术、可靠性指标上达到TQFP、PLCC、PBGA等封装产品的等级要求,能直接安装,使用简便,无论是价格低廉的商用芯片,还是技术含量高的高附加值芯片,都存在可观的客户群。因此,KGD不仅仅是一个技术话题,而且还存在一个可以拓展的市场。

6 结束语

当今,各种电子整机以及子系统、系统的体积越来越小,功能越来越强,性能及可靠性要求增高,对于已完成封装的关键性基础承制产品IC而言,通过封装后的老化筛选(施加电应力、热应力、机械应力)技术,可以保证99.999%封装产品的电性能与可靠性达到整机要求。但对单一芯片来讲,要保证其良好的稳定性和一定的可靠性较难,其几率只有50-99%,推广KGD不仅能大幅度提高多芯片封装的性能,满足电子整机对其可靠性增长的需要,更能给封装产业带来降低成本,提升管理,增强竞争力等多种效益,去不断寻求新的市场。

-

芯片

+关注

关注

459文章

51604浏览量

429936 -

SiP

+关注

关注

5文章

508浏览量

105627 -

测试系统

+关注

关注

6文章

837浏览量

62346

发布评论请先 登录

相关推荐

确好芯片KGD的工艺流程、应用范围和发展分析

确好芯片KGD的工艺流程、应用范围和发展分析

评论