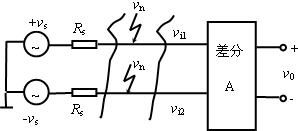

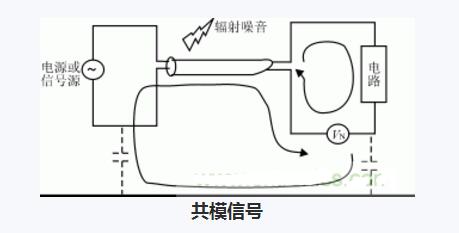

与差分输入电路打交道时,共模抑制比(CMRR)是基本概念,但常常被误解。使用仪表放大器时,关于电路中共模信号的影响,遇到不正确的期望并不罕见。

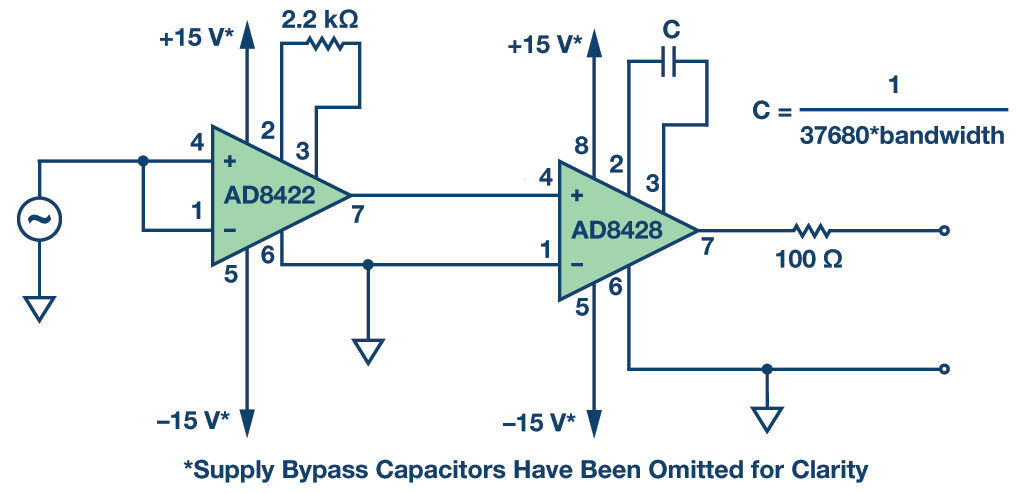

例如,仪表放大器的一项常用CMRR测试是将同一信号施加于两个输入端,然后测量输出。图1所示为 AD8422B的测试电路示例(配置为10 V/V的增益)。第二放大器 AD8428以增益2000工作,将被测器件产生的小误差放大,从而更容易利用标准实验室设备(如示波器)测量。1

图1.CMRR测试电路

在这种设置下,对于输入端的2 V共模变化,可以观察到输出改变40 mV,相当于AD8422B输出端改变20 µV。这一点也不差,但有人可能会争辩说:10 µV/V对应于100 dB的抑制,但数据手册保证至少114 dB的CMRR!难道是器件有缺陷?CMRR去了哪里?

如果您读过非常见问题解答"钻石图",您应当记得必须验证的第一个条件是确认测试是在放大器的共模范围以内进行。利用新的 Diamond Plot tool on analog.com,不需要一分钟便可完成验证!如果一切都很好,下一步便是检查CMRR定义。

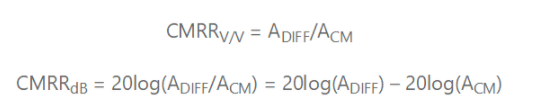

CMRR就是差分增益与共模增益之比。根据如下公式,其单位可以是V/V或dB:

之前测量的10 µV/V相当于–100 dB的共模增益,而不是CMRR。由于放大器增益设置为10 V/V(或20 dB),因此总CMRR为20 dB – (–100 dB) = 120 dB,大于器件的114 dB规格值。如果增益提高到100 V/V,CMRR会再提高20 dB,达到140 dB!不过,使用新增益并将相同的2 V信号施加于输入端时,AD8422输出仍会改变10 µV。您可能要问,如何能说这更好呢?难道是我们在弄虚作假?

并非如此,CMRR的定义对每个人都是一样的。保持这样很重要,我们不会改变它。虽然不需要的共模信号会污染输出,但它保持不变,与增益无关。不过,如果差分增益很大,此"污染"也会变小。换言之,若将共模误差除以增益,再与输入信号进行比较,它将变得非常小。因此,输出端的10 µV/V误差相当于10倍增益时的1 µV/V,100倍增益时的100 nV/V。当测量小信号时,这显然是好事情,道理不言而喻。

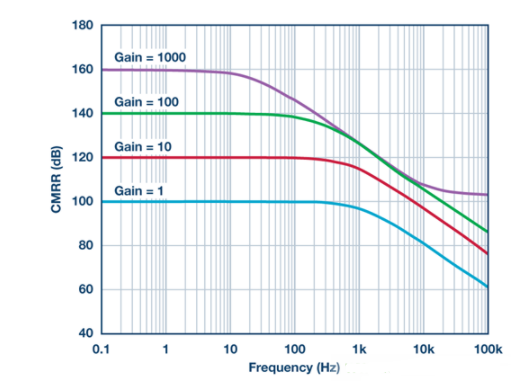

注意:并非所有仪表放大器的CMRR都随增益提高而提高,某些仪表放大器的CMRR在较大增益时会逐渐降低。换言之,假设一个仪表放大器的CMRR为120 dB,当增益提高20 dB时,CMRR可能仅提高到130 dB。我们把这种效应称为"CMRR压缩"。然而,我们看到AD8422的CMRR提高到160 dB,没有压缩。朋友们,这样的CMRR性能是非常稀有的。

图2.AD8422 CMRR与频率的关系。

尾注

1请注意,噪声和高增益(20,000)使该测量具有挑战性。因此,需要对信号源进行滤波,使其噪声贡献最小化。AD8428的滤波器引脚之间使用一个电容来降低测量带宽。此外,必须采用适当的屏蔽和布线来避免拾取外部噪声。

编辑:hfy

-

示波器

+关注

关注

113文章

6303浏览量

186038 -

仪表放大器

+关注

关注

17文章

412浏览量

71377 -

CMRR

+关注

关注

0文章

84浏览量

14876 -

共模信号

+关注

关注

1文章

85浏览量

14209

发布评论请先 登录

相关推荐

RS485防雷保护中的接地问题分析

电路中共模噪声的产生和抑制机理

隔离电源在高铁门控系统应用中共模浪涌拉弧案例分析和整改

电路基础之:差模信号与共模信号

关于电路板中共模电感的摆放思路指导

为什么输出端共模信号的影响大于CMRR规格

关于电路中共模信号的影响分析

关于电路中共模信号的影响分析

评论