Silicon Labs(亦称“芯科科技”)近日推出“Clock Talk”时钟线上系列研讨会的第二场随选即播中文演讲主题“为56G/112GSerDes选择XO/VCXO时钟参考时的设计考量”,提供了中文及英文演说版本供用户选择。 为56G/112G SerDes选择XO/VCXO时钟参考时的设计考量

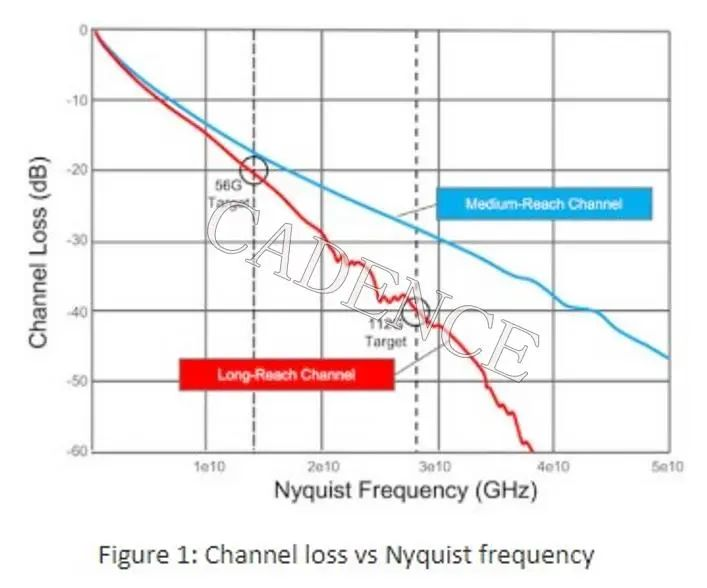

电信、无线基础设施、光学模块、广播视频、医学成像和其他工业市场的下一代参考时钟要求大量采用FPGA、ASIC和SoC,它们使用56G 或112G SerDes 来支持更高的数据速率和带宽功能。SerDes 带宽增加和相关参考时钟的RMS 相位抖动要求之间存在直接的相关性。

随着SerDes 速度的增加,参考时钟所需的 RMS 相位抖动性能随之减少。在本次网络研讨会上,我们概述最新一代FPGA、光学DSP、相干DSP 和网络处理器的参考时钟要求,并重点介绍Si54x Ultra Series XO 和 VCXO 产品家族的关键功能,这些功能可确保参考时钟RMS 相位抖动性能保持在最大限度内;从而为系统设计者在其系统抖动预算中增加了更多馀欲。

责任编辑:lq

-

FPGA

+关注

关注

1625文章

21663浏览量

601670 -

时钟

+关注

关注

10文章

1720浏览量

131339 -

网络处理器

+关注

关注

0文章

48浏览量

13941

原文标题:Clock Talk中文随选即播新单元上线-选择XO/VCXO时钟参考的设计考量

文章出处:【微信号:SiliconLabs,微信公众号:Silicon Labs】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

PCM186X在做从模式时,SCKI和XO,XI不接,使用BCK做时钟是否可以?

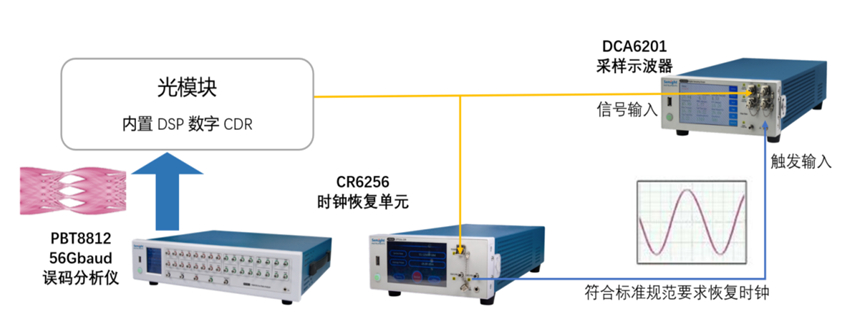

56Gbaud CR6256!400G/800G单多模光模块及接口的时钟提取

AD9694输入时钟低于337.5MHz时,serdes锁相环无法锁定怎么解决?

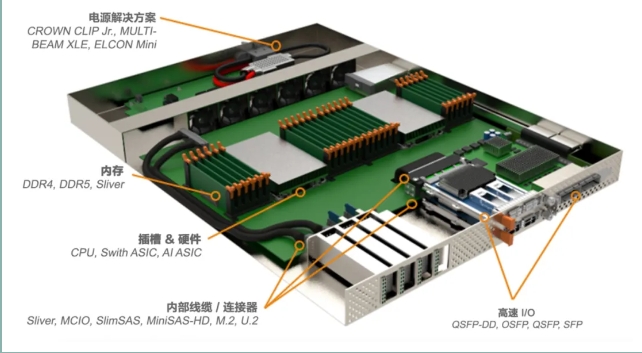

TE 112G 产品解决方案,助力“通关”高速互连挑战

高速板材为什么贵?单看这一点你们就明白了!

Achronix的FPGA有哪方面的优势?

AMD硅芯片设计中112G PAM4串扰优化分析

56G QSFP+ SR4光模块最新解决方案

从56G到112G,高速互连带来的新挑战

200G InfiniBand HDR线缆和光模块:为高速网络应用带来新的突破

为56G/112G SerDes选择XO/VCXO时钟参考时的设计考量

为56G/112G SerDes选择XO/VCXO时钟参考时的设计考量

评论