在不久前召开的IC CHINA 2020(中国国际半导体博览会)上,中国工程院院士、浙江大学微纳电子学院院长吴汉明预测,“随着工艺节点演进,摩尔定律越来越难以持续,预计将走到2025年。”半导体企业的制程工艺正向这个终点进发。最新消息是,台积电将在2022年量产3纳米工艺芯片,2024年推行2纳米工艺。

1纳米会是摩尔定律的终点吗?现有制程工艺下,也许会。除非新工艺和新材料出现突破。台积电曾乐观预测,在此前提下,或许到2050年,制程工艺可以达到0.1纳米。

但无论如何,那将是一个少数人的游戏,而基于众所周知的原因,中国在这个游戏中暂时落后。“后摩尔时代”,中国芯片的机会在哪里?

01

不可承受的“AI之重”

“产业发展的驱动是算力,根据OpenAI预估,AI算力约每3.4个月翻倍,但算力需求增长速率是10倍/年增长,就算摩尔定律不放缓,都难以满足日益增速的算力需求。”IC CHINA2020上,上海燧原科技有限公司创始人兼CEO赵立东如是说。

AI算力虽然从2012年开始大约每3.4个月翻一倍,但依然低于算力需求的增速,图源:OpenAI

摩尔定律认为,一块芯片中可容纳的晶体管数量每隔18至24个月就会增加一倍,性能也将提升一倍。自1965年摩尔提出此观点后,芯片性能的提升基本以每5年增长10倍,每10年增长100倍的速度前进。

但是,制程工艺从22nm进入“后摩尔时代”,摩尔定律开始放缓,英伟达创始人黄仁勋甚至在CES2019上表示,摩尔定律每年只能增长几个百分点,芯片性能的增速已降至每10年可能只有2倍。

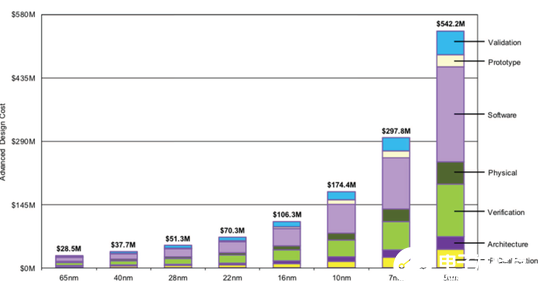

不同工艺节点时的芯片设计成本水涨船高。据调查机构IBS估算,16纳米制程开发费用达1亿美元,10纳米为 1.74亿美元,目前主流7纳米要冲上3亿美元,5纳米要价约4.36亿美元,3纳米更飙到6.5亿美元。

芯片不同工艺节点开发成本,图源:IBS

美国半导体行业协会总裁兼首席执行官John Neuffer透露,美国半导体公司每年大约将五分之一的收入用于应对芯片设计成本上升的挑战。

制程工艺同样面临挑战,吴汉明表示,我国集成电路产业发展艰难,尤其是芯片制造工艺存在三大挑战:光刻是基础挑战、新材料&工艺是核心挑战、提升良率是终级挑战。

02

20纳米以上还有很大空间

算力和摩尔定律的矛盾显而易见,但现状是,先进制程工艺基本被台积电、三星垄断,加上今年以来复杂的国际关系,仅仅依靠工艺升级已经不能满足算力的需求。

但对中国企业而言,未尝不是件好事。吴汉明预测,“新材料、新工艺将是未来成套工艺研发的主旋律,包括光刻技术、薄膜技术在内的很多关键技术,进行完整的工艺集成后,形成可以商用的成套工艺。

2019年全球 82%的晶圆代工产能都是 20nm以上节点,20nm以下节点先进产能仅占12%,这为企业留下了巨大的创新空间。”

事实上,晶体管密度更高的芯片,大多被用于手机制造,而随着AI时代的到来,当万事万物都需要增加一个“大脑”时,大多数智能化产品不会像手机一样,对单位面积内的计算速度有不可替代的需求。

换句话说,很多AI芯片,可以在并不需要顶尖制程工艺的前提下,通过成套工艺的创新,达到和先进制程工艺同样的计算能力。

如果说台积电和荷兰ASML公司“锁死”了中国通过制程工艺改良制造高端芯片的方向,那么中国芯片必须“另辟蹊径”。

“全球半导体产业经过三次转移,而每次转移都是因为需求发生变化,从20世纪90年代开始,随着PC和手机相继普及,产业链从韩国、中国台湾逐渐转移至中国大陆,等到了智能物联网时代,轻设计厂商将成为主流。”芯原股份董事长戴伟民表示。

数据显示,中国已经成为全球规模最大、增速最快的集成电路市场。John Neuffer透露,2019年,中国市场贡献了美国半导体公司36%的收入,中国的PC、手机、电视、可穿戴设备的出口额在全球份额中均是第一位。

2016年统计的美国半导体行业的公司对中国市场的依赖性,图源:Quartz

国内边缘计算芯片企业地平线创始人余凯认为,未来自动驾驶对于车载智能算力的需求是一种机遇,新的封装技术、软件硬件的高度协同、面向自动驾驶人工智能所做的创新型架构设计以及编译器操作系统,会使人工智能算力以指数级的“摩尔定律”向前发展,但这要求人工智能企业要有全新的思维设计芯片。

03

突破:Chiplet的尝试

创新之路在哪里?新结构、新材料、新集成设计创新,是业内基本公认的三条路,但设备和材料方面,日本崛起较早,如今是市场领头羊,中国最有可能在设计领域有所突破。

戴伟民认为Chiplet(芯粒)是一条可行之路。所谓Chiplet,是由Marvell创始人周秀文提出的MoChi(Modular Chip,模块化芯片)架构,顾名思义,就是将不同工艺节点的die(裸片)通过异构的方式混装,这样可以大大降低企业在先进工艺制程方面的成本。

比如苹果A13在16纳米工艺下成本为4.98美元/10亿晶体管,但在7纳米工艺下成本只需2.65美元/10亿晶体管。

但正如前文所言,高制程的芯片设计开发成本惊人,一般企业无法承受。

戴伟民认为,Chiplet新形态是未来芯片重要趋势之一。比如一块芯片可以做到CPU用7nm工艺,I/0则用14nm工艺,这样与完全由7nm打造的芯片比成本大约降低50%。

但Chiplet的问题在于,不同芯片间互连的功耗和性能如果没有标准,可能效果适得其反。

目前芯原提出IP即Chiplet,可以将ISP(图像处理)、NPU(神经网络处理器)、VPU(视频处理器)、GPU(图形处理器)等芯片形成基于不同工艺节点的Chiplet,并做到“即插即用”。

如此,对中国企业而言,Chiplet将大规模降低芯片设计的门槛;半导体IP授权商能升级为Chiplet供应商,提升IP的价值且有效降低芯片客户的设计成本。

更重要的是,Chiplet可以更好利用中国的封装资源,尽管在先进制程上被“卡脖子”,但中国的封装工艺基本接近世界顶级水平。

“领头羊”长电科技如今正在持续推进Chiplet的量产和2.5D/3D的封测技术开发,预计到2021年,可以实现2.5D封装工艺,从而推动Chiplet更快落地。

04

未来:减少试错成本

2019年,我国集成电路产业规模实现7000多亿元,同比增长15.8%。工业和信息化部电子信息司副司长杨旭东在IC China上表示,中国在全球市场份额中占比接近50%。

尽管近年来美国开始实行“脱钩”政策,但中国芯片产业正在迅速崛起。数据显示,今天中国已经拥有世界17%的芯片产量。John Neuffer预计,到20世纪末,这一比例将增加到28%,尤其是在无晶圆厂和OSAT(封测代工厂)领域,中国具有明显优势。

但中国的劣势也很明显。2020年,美国半导体行业协会最新调研显示,中美摩擦将改变全球IC产业格局,目前中国本土IC自给率只有14%,中国本土IC设计业的全球市占率为15%,整体IC产业全球市占率只有5%。相比之下,美国的各项占比均在50%以上。

据上海集成电路产业投资基金管理有限公司总经理陈刚介绍,从材料、装备、制造/封测、设计四个环节来看,科创板对于光掩模、12寸抛光片等材料领域的企业寻求二级市场资本有了一定覆盖,但在先进工艺所需的高端材料和光刻机设备、抛光机方面,仍是空白,设计领域的EDA、CPU、FPGA、DRAM、NAND等领域也都存在空白。

在最为核心的半导体设备市场,中国与全球差距甚远。2019年,中国的半导体设备国产化率为18.8%,但盛美半导体设备股份有限公司董事长王晖坦承,其中核心设备占比很小。

从各国研发经费分配来看,我国与世界先进国家的差距仍然很大,尤其在基础研究领域,大部分研发停留在试验阶段,难以产生革命性的创新。

吴汉明指出,中国的集成电路研发经费的总额不比英美法日少,但比例严重失衡,只有5%经费投入基础研发,尤其是一些芯片制造企业,试错成本占了整个研发经费的84%,“我们必须要有一个基础引导,使这种所谓试错式研发变成实验式研发。”

责编AJX

-

芯片

+关注

关注

455文章

50848浏览量

423859 -

摩尔定律

+关注

关注

4文章

634浏览量

79048 -

AI

+关注

关注

87文章

30941浏览量

269185

发布评论请先 登录

相关推荐

击碎摩尔定律!英伟达和AMD将一年一款新品,均提及HBM和先进封装

破万亿!中国芯片出口迎来里程碑

后摩尔定律时代,提升集成芯片系统化能力的有效途径有哪些?

中国芯片新锐50强

观点评论 | 芯片行业,神奇的一年

高算力AI芯片主张“超越摩尔”,Chiplet与先进封装技术迎百家争鸣时代

“自我实现的预言”摩尔定律,如何继续引领创新

持续发力布局成熟制程,中国芯片产能未来三年或提升达60%

摩尔定律的终结:芯片产业的下一个胜者法则是什么?

2024年,功率器件的机会在哪里呢?

2025年摩尔定律或迎来终点,中国芯片的机会在哪里?

2025年摩尔定律或迎来终点,中国芯片的机会在哪里?

评论