1 MAX121芯片的性能与特点

MAX121芯片是一个带串行接口的14位模数转换集成电路(ADC),它包含有跟踪/保持电路 的一个底飘溢、底噪声、掩埋式齐纳电压基准电源。它的转换速度快、功率消耗底、采样速率高达308 ks/s点,满量程输入电压范围为±5V,功耗为210 mW。可与大多数流行的数字信号处理器的串行接口直接接口,该输入可以接收TTL或CMOS的信号电平,时钟频率为0.1-5.5MHz。

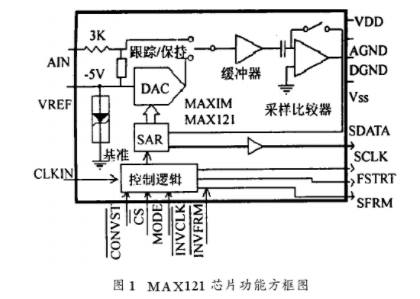

MAX121芯片的功能方框图如图1所示。它有16脚和20脚模式,16脚有DIP和SO封装,20脚有 SSOP封装。特点如下:

14位分辨率;2.9 μS转换时间/308 ks/s吞吐率;400 ns采样时间;底噪声和低失真:78Db SINAD -85Db THD;±5V双极性输入范围,可时承受±15V的过电压;210 mW功耗;可用连续转换模式;30 ppm/C,-5V内部基准源;与DSP处理器接口;16脚DIP和SO封装,20脚SSOP封装。

极限参数:VDD对DGND 0.3-+6V;VSS对DGND +0.3--7V;AIN对AGND±15V;AGND对DGND ±0.3V数字输入对DGND(CS,CONVST,MODE,CLKIN,INVCLK,INVFRM);-0.3(Vdd+0.3V);数字输出对DGND(SFRM,FSTRT,SCLK,SDATA )+0.3(Vdd+0.3V);连续功率消耗(TA=+70 ℃)

强度超出上述极限参数可能导致器件的永久性损坏。这些仅仅是极限参数,并不意味着在极限参数条件下,或在任何其他超出技术规范规定的工作条件下,器件能有效地工作。延长在极限参数条件下的运行时间,会影响器件的可靠性。

2 工作电路

MAX121运用逐次比较技术和跟踪/保持(T/H)电路,将模拟信号转换为14位串行数据输出 码。其控制逻辑接口很容易与大多数微处理器(霵)和数字信号处理器(DSP)相连接,在大多数应用中只需要很少几个无源元件。T/H电路不需要外接电容。

2.1 模拟输入跟踪与保持

根据等效输入电路分析,给出ADC的模拟比较器的采样结构。内部缓冲器给保持电容充电,以减小转换期间所要求的采集时间。模拟输入端呈现6k输入电阻及与其并联的10pF电容。

在两次转换之间,缓冲器输入通过输入电阻连接到AIN端。当转换开始时,缓冲器与AIN端 断开,对输入信号采样。在转换结束时,缓冲器输入端又连接到AIN端,而且保持电容跟踪 输入电压。无论何时,只要转换没有进行,T/H就处于跟踪模式。在转换开始以后,保持模 式启动时间接近10 ns(窗口延迟)。从一次转换到下一次转换延迟变化的典型时间为30 ps(窗口抖动)。

2.2 电路时钟频率

MAX121工作时需要一个与TTL,CMOS电平兼容的时钟,时钟频率的范围从0.1-5.5 MHz。为满足2个时钟周期400 ns采集时间的要求,最大时钟频率限制在5MHz。由于内部T/H 电压下降速率的限制,所有模式的时钟频率不应低于0.1MHz。

2.3 输出数据格式

转换结果以16位串行数据流输出,前14位为数据位(首先为MSB),后2位为零。输出数据 为二进制补码形式。在CLKIN的上升沿,数据在SDATA端同步输出。

输出数据可用FSTRT或者SFRM输出来分帧。FSTRT(平常为低)低于MSB1个时钟周期变为高。FSTRT的下降沿SDATA端输出MSB。

SFRM输出(当INVFRM=Vdd时通常为高)变为低的同时,MSB出现在SDATA端。16个时钟周期以后 SFRM变为高电平。通过输入接到数字地,可反转SFRM的极性。要求每次转换最少为18个时钟周期,以获得有效SFRM输出。

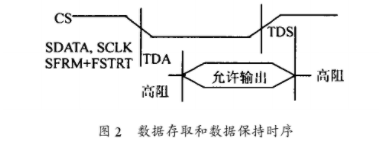

如果有几个器件共用串行总线,可以参看图2的数据存取和数据保持时序。

3 TMS320高速串行接口

3.1 上电后的初始化

如果满足下列条件,上电后MAX121的首次转换将是有效的。提供16个时钟脉冲使T/H进入跟踪模式,再加上跟踪模式中数据采集的最小时间400 ns。确保基准源已经稳定。每1μF基准源旁路电容的稳定时间是0.5 ms(对22μF电容为11ms)。

3.2 串行时钟最大速率

与数字信号处理器接口时,MAX121的串行时钟最大速率取决于处理器的串行数据输入所要 求的最小建立时间和ADC的时钟与数据的最大延迟时间。MAX121有两种方法将数据读入处理器。 CLKIN是MAX121的输入时钟,而SCLK是使数据移位进入处理器的串行时钟,支持异步数据传输的场合。tSU是处理器串行数据输入端所要求的数据建立最小时间;tCD是MAX121的CL KIN到SCLK最大延时时间;tSC是MAX121的SCLK到SDATA的最大延时时间。MAX121 的SCLK输出驱动处理器的串行接口,此时可从以上议程中去掉tCD项,并允许使 用更快的时钟频率。在这种情况下,串行时钟最大速度由下式计算:

fCLKIN=1/2(tSU+tSC)

3.3 高速数据串行接口

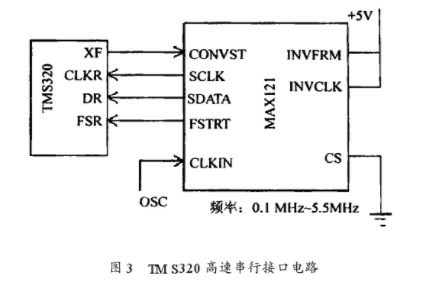

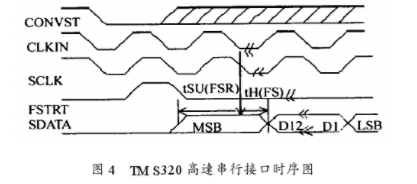

MAX121的灵活性使它可以与德州仪器公司TMS320的各种串行接口连接。高速接口可使MAX121/TM320系统获得最大的数据吞吐率,此时MAX121工作在它的最快时钟。图3示出了完成这种 接口所需的连线。图4为接口的时序图。

MAX121的CLKIN由外部时钟振荡器驱动。TMS320的XF0 I/O口驱动MAX121输入端为低,启动 一次转换。TMS320的CLKR(接收时钟)端配置为输入,并由 MAX121的SCLK输出端驱动。MAX 121的SDATA输出端数据在时钟的上升沿改变状态,而在时钟下降沿,数据被锁存到TMS320的 DR输入端。这样可提供1/2个时钟周期,以满足TMS320DR输入端所需要的数据建立和保持时间。 MAX121SCLK和SDATA之间的最大时滞在+25时为65ns,所以1/2个时钟周期足以满足要求的建立和保持时间。

MAX121的FSTRT输出驱动TMS320的FSR输入,以对数据分帧。FSTRT输出的下降沿指示MSB已准备好,可被锁存。在下一个时钟下降沿,MSB被锁存在TMS320。使用这种接口,TMS320可接收16位字(在TMS320串行口整体控制寄存器中,RLEN=01),于是14位数据被时钟同步移入DSP,同时跟随两位尾随的0。

4 结论

近几年来,随着便携式、手提式电子产品的日益增多,MAXIM系列产品的应用也越来越广 泛,这里详细介绍了MAX121芯片在数字信号处理高速串行接口电路方面的应用。同时MAX121集成电路也在语言识别和合成、DSP伺服合成、频谱分析等领域都有广泛的应用。

编辑:jq

-

芯片

+关注

关注

452文章

50142浏览量

420455 -

集成电路

+关注

关注

5374文章

11289浏览量

360194 -

CMOS

+关注

关注

58文章

5649浏览量

234965 -

TTL

+关注

关注

7文章

496浏览量

70034

发布评论请先 登录

相关推荐

SOC芯片在汽车电子中的应用

串行接口PCB设计指南:优化布局与布线策略

DRV8332芯片在调试的过程中,输出始终达不到24V,为什么?

6芯M16接口的应用探析

FPGA的sata接口设计时需要注意哪些问题

高速串行总线有哪些

高速串行收发器原理及芯片设计

串行音频接口(SAI)中slot是什么意思?

深入探析:DLT8P68SA主控芯片在无线剪毛器中的应用

探析MAX121芯片在高速串行接口电路中的应用

探析MAX121芯片在高速串行接口电路中的应用

评论