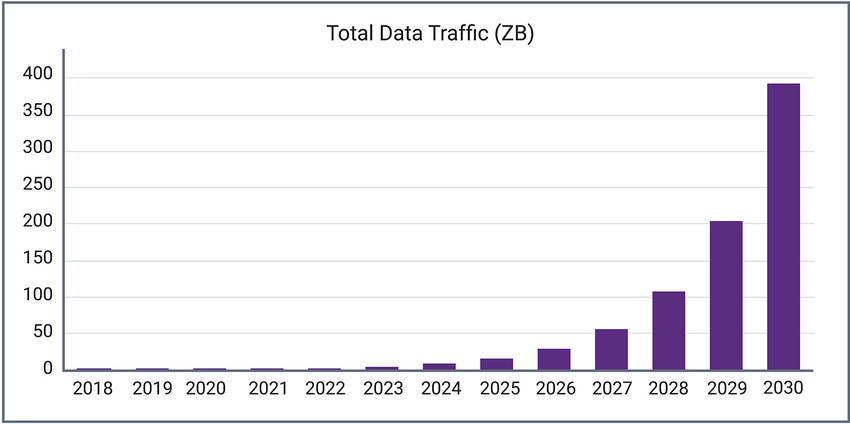

流媒体、监视和监控数据、联网传感器、社交媒体、在线协作、远程学习、增强和虚拟现实、在线游戏……随着无穷无尽的在线应用不断涌现,在线数据量出现激增。预计在未来 10 年中,数据流量的年增长率将超过 400 倍(图 1)。这种数据流量的快速增长,将对数据接口 IP 提出更高要求,需要其在速度和延迟方面,尤其是云基础架构中都有显著改善。本文将解释在数据中心内、数据中心之间、服务器内以及 SoC 内等,加速数据传输和管理的技术发展。

图 1:2030 年之前的总体数据流量预测。来源:《人工智能对于电子和半导体行业的影响》,IBS,2020 年 4 月。

数据中心内部和数据中心之间的长距离数据移动

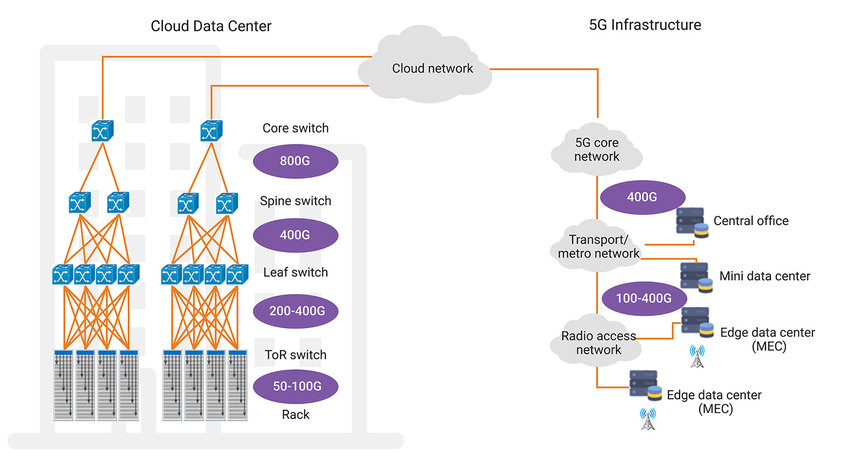

当今,大多数大型数据中心都使用 100Gbps 以太网基础架构,数据跨越长距离(例如,在机架和数据中心之间)进行传输。长距离传输架构通常需要使用 4 个 25 Gbps 或 28 Gbps NRZ SerDes 连接通道。然而,随着数据量的增长,需要速度更快的基础架构来维持数据传输。使用支持 PAM-4 编码的 56 Gbps 和 112 Gbps SerDes IP,在目前正在部署的超大规模数据中心中,可实现 400Gbps 的以太网连接,并在未来会实现高达 800Gbps 的连接速度(图 2)。主要的以太网交换机供应商已经在开发基于 112G SerDes IP 的 800Gbps 交换机,计划在未来几年内推出 1.6Tbps 以太网(使用更快的新一代 SerDes),以满足数据量不断增长带来的需求。

机架内服务器之间的数据通信,由顶层 (ToR) 交换机和网络接口卡 (NIC) 管理。过去几年,云数据中心在该级别最常用的接口速度为 25Gbps。但是,随着基础架构速度提高到 400Gbps,机架内的以太网速度也提高到了 100Gbps。

随着数据速率的提高,接口功耗(通常以“皮焦耳/位”为测量单位)和面积变得越来越重要。物理接口 (PHY) IP 具有明显的优势,可最大限度地减少能耗,同时在所需距离内可靠地提供数据,从而可最大限度地降低基础架构的功耗和散热成本。节省空间的硅 PHY 解决方案可最大限度地降低 SoC 成本,从而为 SoC 供应商提高盈利能力。

图 2:超大规模数据中心基础架构逐渐转向采用 400+GbE

服务器内部的数据传输

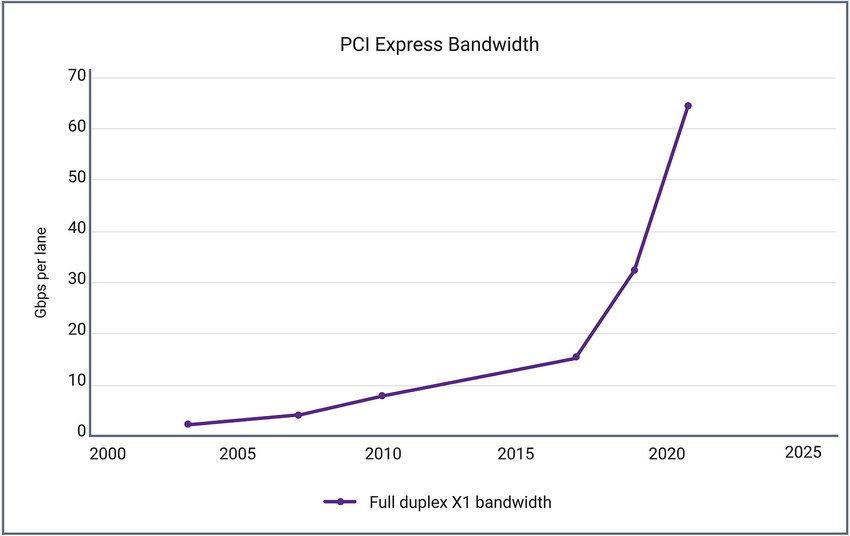

所有数据到达服务器后,就需要利用高速接口,在服务器内部的设备之间高效移动这些数据。例如,当数据以 100Gbps 的速度到达 NIC 时,必须将其快速移动到存储器、系统内存,也可能移动到图形或 AI 加速器,以进行处理。PCI Express (PCIe)、Computer Express Link (CXL) 和类似协议在这一方面具有优势。为了应对流量的快速增长,PCI-SIG 于 2019 年发布了 PCIe 5.0,带宽比上一代产品翻倍,并力争在 2021 年发布 PCIe 6.0,再次使 PCIe 数据速率翻倍,达到 64 GT/s(每个 x16 卡的速率高达 128GB/s)(图 3)。

图 3:PCI Express 每个通道的带宽升级过程。来源:PCWorld

近来,由计算系统生成和处理的数据量(尤其是非结构化数据)持续增长,已促使了新架构的产生,新架构通常采用加速器来加快数据处理。将数据从一个处理器域复制到另一个处理器域是一个资源密集型过程,这会显著增加数据处理的延迟。缓存相干解决方案让处理器和加速器共享内存,而无需将数据从一个内存空间复制到另一个内存空间,从而节省了复制数据所需的内存资源和时间。

CXL 是一种缓存相干协议,利用 PCIe 的数据速率和 PCIe 物理层,使 CPU 和加速器能够访问彼此的内存。在多个设备都需要访问同一个数据集时,集成 CXL 协议可有效减少必须具有非相干协议的数据副本数,从而减少系统内所需的传输次数。减少数据副本数,有助于降低系统中大量已预留的内存和 IO 接口的负载。

与其他外设互连相比,用于高性能计算工作负载的 CXL 可显著降低延迟。由于 cxl.cache 和 cxl.mem 事务的延迟仅为 50-80 纳秒,因而在 PCIe 延迟中,CXL 延迟仅占一小部分。此外,CXL 通过使用资源共享提高性能并降低复杂性,这也降低了总体系统成本。

SoC 内的 USR/XSR 数据移动

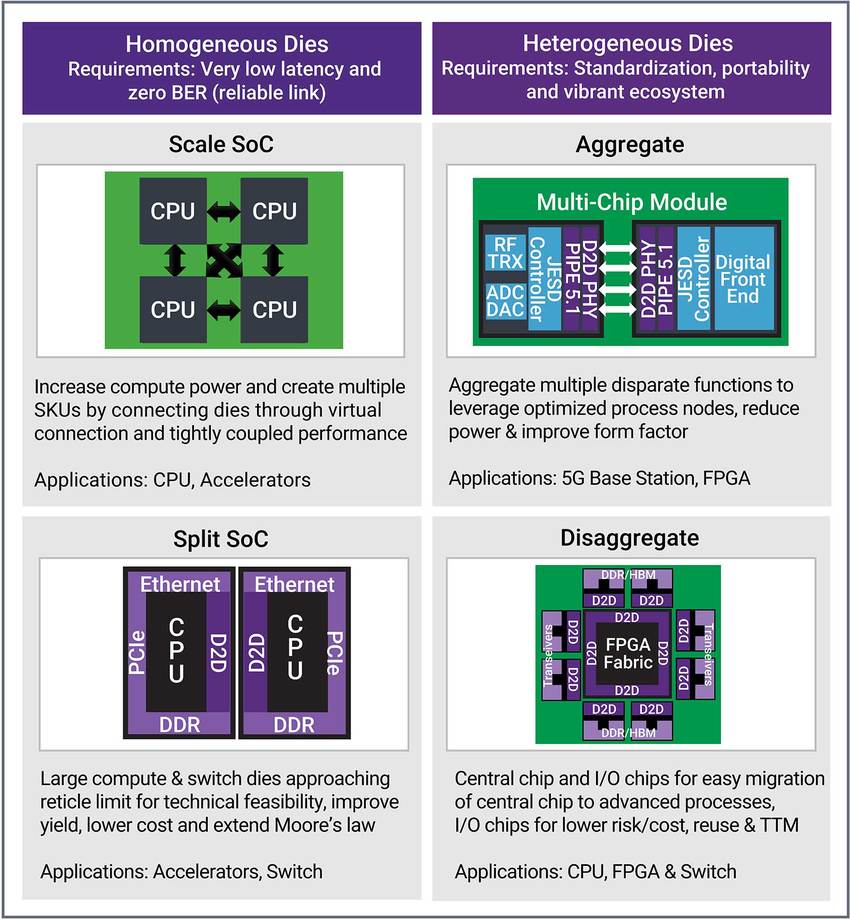

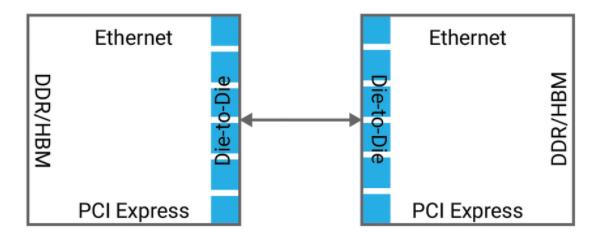

许多现代服务器 SoC 利用在单个 package 内放置多个 Die,在符合设计和制造约束的范围内提供所需的性能。因此,需要高速 die-to-die (D2D) 通信以在芯片内的 Die 之间传递大型数据集。超短距离/极短距离 (USR/XSR) SerDes 可实现这一传递,当前设计使用 112Gbps SerDes,并且在未来几年内可能会达到更高的速度。

使用 D2D 接口技术的多芯片模块可处理多种用例。所有 D2D 用例都缩短了开发时间,并降低了开发和制造成本。有些情况使用多个异构 Die(即“小芯片”),它们利用可重复使用的功能组件,每个组件都使用最适合其特定功能的制造技术构建。其他情况通过创建大型高性能 SoC 着重提高灵活性,此类 SoC 使用更小的同质构建模块来提高良率和可扩展性。

图 4:举例展示 Die 间互连用例

总结

云数据的快速增长推动了对于更快、更高效接口的需求,以将云基础架构内的数据从网络和系统向下传输到芯片级数据通信中。新推出和正在开发的接口技术(包括 400Gbps 和更快的以太网、PCIe 6.0 和 CXL 外设互连技术,以及用于 Die 间通信的新型高速 SerDes)可实现必要的基础架构改善,以支持不断提高的云数据需求。

新思科技的 DesignWare® 高速 SerDes 和以太网 IP 支持实现新一代数据中心网络解决方案。DesignWare PCIe IP 是一种稳定成熟的技术,在 90% 的领先的半导体公司得到应用,为实现 DesignWare CXL IP 奠定了基础。DesignWare 112G USR/XSR SerDes IP 为多 Die SoC 提供低成本、节能的 die-to-die 接口。新思科技提供经过硅验证且品类齐全的 DesignWare 接口 IP 产品组合,同时提供开发高速、低功耗、高度可靠的 SoC 所需的设计和验证工具,以支持当今和未来云基础架构不断提高的数据移动需求。

-

接口

+关注

关注

33文章

8496浏览量

150828 -

soc

+关注

关注

38文章

4118浏览量

217926

发布评论请先 登录

相关推荐

选择合适的 IP 实现 Die-to-Die 连接

为多Die SoC提供低成本低功耗的die-to-die接口

为多Die SoC提供低成本低功耗的die-to-die接口

评论