曾有人在STMCU社区网站咨询如下问题:

由于实验需要,要用到STM32F407的两个DMA并用定时器触发,在使用过程中发现DMA1无法把GPIO的IDR数据传输到内存,调试过程中出现DMA1的数据流传输错误标志,但是使用DMA2没有问题。另外当把访问GPIO的IDR改成访问APB1下的tim5的ARR时,DMA1也能正常工作。请问这是怎么回事?

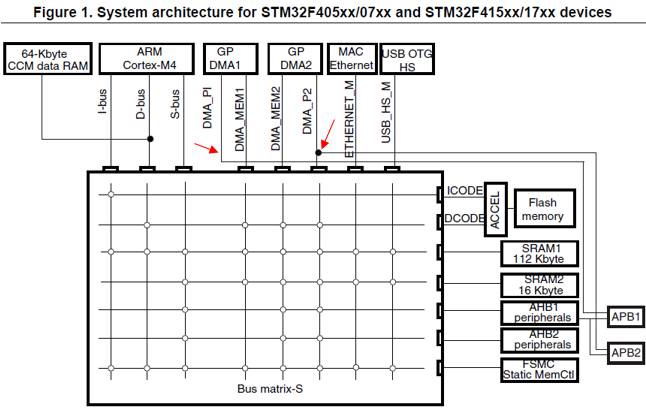

咨询者提到STM32F4系列中DMA1与DMA和另外两个外设GPIO和TIM5 。为了弄清这个问题,我们有必要先看看STM32F407的总线与存储框架图。 如下图所示:

整个系统架构由多层32位AHB总线矩阵及主从总线构成,并建立起各个主从模块间的互联访问。借助于总线矩阵,可以实现主控设备到从控设备的访问,可以实现多个高速外设的并发访问和高效运行。[需要注意的是,对于STM32F4系列,图中64K CCM并不经过总线矩阵,只能被CPU访问。自然DMA是不能访问它的.]

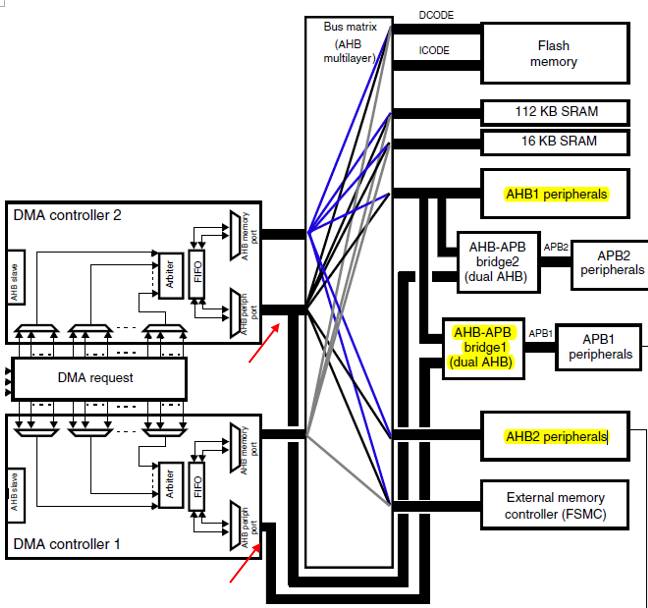

我们接着看看STM32F407 的DMA1和DMA2的访问框架图。这两个DMA都具有双AHB总线访问端口,一端用于存储器访问,另一端用于外设访问。

结合这幅DMA总线访问框图和上面的系统存储总线框架图可以看出,2个DMA的外设访问端口的总线连接有点不一样。

DMA2的外设访问端口既与总线矩阵相连,经过矩阵可以访问AHB外设,又与AHB-APB桥2相连,可以进一步访问APB2外设;而DMA1却没有与总线矩阵相连,只是跟AHB-APB桥1相连,从而访问APB1外设。[长方形方框代表总线矩阵]

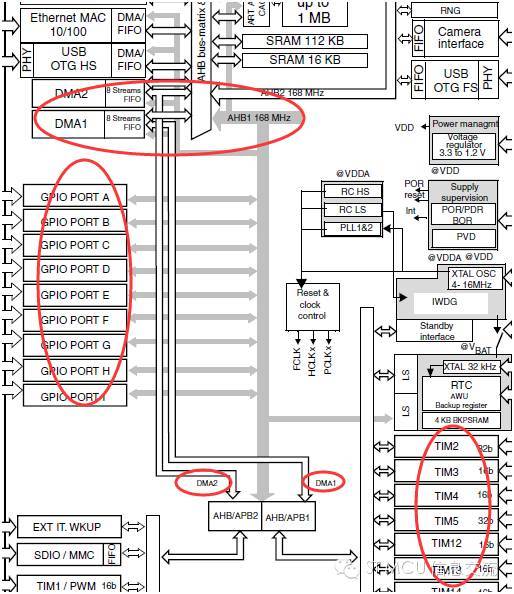

现在的问题是说DMA1访问不了GPIO,但如果换成TIM5就可以。我们可以去芯片数据手册的Device overview部分查看相关总线和外设联结图。截取STM32F40x block diagram的部分如下:

不难看出GPIO外设跟AHB1相连;TIM5跟APB1相连。我们再结合中间的DMA访问框图看得清楚,DMA1的外设端口根本没连接AHB1,自然没法访问相应外设,比如GPIO。而DMA2 可以,因为它可以经过总线矩阵后再去访问AHB1的外设。DMA1为什么能访问TIM5也不难解释了,因DMA1的AHB外设端口总线经过AHB/APB1桥后就可以访问APB1各类外设,而TIM5就是挂在APB1总线上的外设之一。

咨询者的问题基本上靠看上面几幅图可以得到答案。这些图很重要,很多信息用图描述也很直观明了。各技术手册里的插图往往大有乾坤,不要视而不见。上面提到的都是基于STM32F4系列的总线架构,你也可以去看看其它系列的系统总线框图,相信你一定会另有发现和收获。

-

存储器

+关注

关注

38文章

7484浏览量

163763 -

STM32

+关注

关注

2270文章

10895浏览量

355734 -

总线

+关注

关注

10文章

2878浏览量

88051

原文标题:一个跟STM32F4系统总线架构有关的问题

文章出处:【微信号:STM32_STM8_MCU,微信公众号:STM32单片机】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

STM32F4系统总线架构介绍

STM32F407 DCMI摄像头源码

STM32F407与STM32F105 CAN通讯失败的定位解决

STM32F407芯片介绍

【STM32F407开发板用户手册】第34章 STM32F407的SPI总线应用之驱动DAC8501(双路输出,16bit分辨率,0-5V)

STM32F407总线存储框架及应用设计

STM32F407总线存储框架及应用设计

评论