声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

microchip

+关注

关注

52文章

1527浏览量

117998 -

教程

+关注

关注

25文章

265浏览量

54280 -

Direct

+关注

关注

0文章

15浏览量

11202

发布评论请先 登录

相关推荐

请问VisonFive2开发板如何将主频设置为1GHz?

查阅相关资料只说明最大支持1.5GHz主频,新手入门请问如何将开发板主频设置为我想要的1GHz呢

该类开发板可以设置主频吗,请大佬解答

发表于 03-10 06:16

小安派BW21-CBV-Kit入门教程:中断控制LED

,可以扩展出无限可能。 BW21-CBV-Kit支持Arduino的开发方式,可以简单实现一些DIY想法,例如:人脸识别、手势识别、物品识别等。 这次小安给大家带来的是快速入门教程之中断控制 LED

Teledyne e2v发布LX2160-Space工程样片

Teledyne e2v近日正式宣布,推出基于Arm®Cortex®A72的16核片上系统(SoC)处理器LX2160-Space的工程样片。该样片旨在满足要求苛刻的宇航应用需求,助力早期项目

新手怎么学嵌入式?

。但面对这个复杂的领域,很多人可能会感到迷茫,不知从何处入手。别担心,本文将为你提供一些入门学习嵌入式技术的建议。 新手入门学习嵌入式技术的途径 1. 了解基础知识 首先,要对嵌入式系统有一个

发表于 12-12 10:51

FPGA编程语言的入门教程

FPGA(现场可编程逻辑门阵列)的编程涉及特定的硬件描述语言(HDL),其中Verilog和VHDL是最常用的两种。以下是一个FPGA编程语言(以Verilog为例)的入门教程: 一、Verilog

瑞芯微RK3566鸿蒙开发板OpenHarmony标准系统应用兼容性测试指导

本文OpenHarmony标准系统应用兼容性测试指导,适用鸿蒙系统软件开发测试的新手入门学习课程,设备为触觉智能的瑞芯微RK3566开发板,型号Purple Pi OH。是Laval官方社区主荐的一款鸿蒙开发主板。

第一篇:V1.5-STM32f103c8t6智能小车笔记 标准库开发 6612电机驱动新手入门项目

这是全网最详细、性价比最高的STM32实战项目入门教程,通过合理的硬件设计和详细的视频笔记介绍,硬件使用STM32F103主控资料多方便学习,通过3万字笔记、12多个小时视频、20多章节代码手把手教会你如何开发和调试。让你更快掌握嵌入式系统开发。

嵌入式入门心得:从新手到老鸟的蜕变

作为一名在嵌入式领域摸爬滚打多年的老鸟,我深知新手在入门时面临的困惑与挑战。嵌入式系统是一个复杂而迷人的领域,它涉及硬件、软件以及它们之间的交互。在这里,我想分享一些我的入门心得,希望能为正在嵌入式道路上探索的

新手入门如何选择Arduino与树莓派?

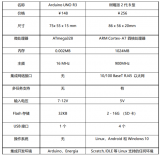

树莓派2的主频速度和内存量两个主要方面都远高于Arduino。树莓派可以被看作一台完全独立的计算机,可以直接运行Linux和Windows 10操作系统,支持WIFI链接和多任务运行。

发表于 04-28 14:56

•790次阅读

STM8用IAR编辑器调用串口2函数报错的原因?

新手入门STM8,资料是用众拳的,,新手求助,为什么STM8使用IAR编辑器,程序是网上众拳的教程,为什么修改不了库函数的c文件,文件在编辑器的上面有个锁呢?还是我用的是STM8S105,只有串口2

发表于 04-17 08:23

读《FPGA入门教程》

的后三章涉及一些实质性的开发设计内容,有兴趣的坛友可以使用手边的开发板,进一步深入研究。此次跟读就介绍到此,欢迎回帖交流。*附件:FPGA入门教程.pdf

发表于 03-29 16:42

新手学习单片机最常见的六大误区!

最近看到台私信要资料的同学比较多,想必大家都是对单片机有着浓厚的学习兴趣,但是很多新手开始入门单片机的时候都会遇到一些学习的误区,今天就来整理一下大家可能会遇到的六大误区。单片机作为嵌入式系统的核心

新手入门的简单小例子-05-03

基于FPGA使用verilog HDL设计一个数字时钟,时间24小时、60分钟、60秒钟的计数;首先默认我们的板载有源晶振为50MHz的时钟,然后我们已经设计了一个秒钟的计数模块,现在设计一个时钟的技术模块,基于秒钟和分钟计数满的flag信号为触发信号,对应的code设计如下:

module hour_clock(

input wire clk,

input wire rst_n,

input wire min_full_flag,

output reg [4:0] hour_data

);

//hour计数器

always @(posedge clk or negedge rst_n)

if( rst_n == 1\'b0 )

hour_data <= 5\'b0;

else if( (min_full_flag == 1\'b1)&&(hour_data == 5\'d23) )

hour_data <= 5\'b0;

else if( min_full_flag == 1\'b1 )

hour_data <=hour_data + 1\'b1;

else

hour_data <=hour_data;

endmodule

发表于 03-26 14:33

microchipDIRECT新手入门教程(二):样片

microchipDIRECT新手入门教程(二):样片

评论