摘引言

穿墙雷达是一种能够穿透非金属墙壁,并对墙壁后面人员或物体进行探测、追踪和定位的雷达系统,一般采用超带宽步进体制。本实验室搭建的穿墙雷达系统需要一个l~2 GHz频带的信号源。根据系统带宽以及杂散、相位噪声等系统参数要求,笔者采用DDS+PLL混合频率合成技术,并充分利用AD9858等高集成化芯片,设计了一种可满足系统信号源输出要求的频率合成器。

1 系统原理与结构

DDS+PLL频率合成器的基本原理是用一个低频、高分辨率的DDS频率来激励或者插入PLL,然后将两者的优势结合起来产生高品质的信号源。

本文采用DDS激励PLL的方案来满足系统要求。本系统采用高稳定的频率源作为系统参考时钟;并在单片机的控制下把频率控制字和相位控制字写到DDS内部寄存器,然后由DDS产生一个频率和相位都可以编程控制的模拟正弦波输出,并把DDS的输出作为PLL的参考信号,最后根据穿墙雷达系统要求的信号频率来设定分频器的分频比N,从而得到系统输出信号。此类方案实现的信号源具有较高的频率和较快的频率转换速度,而AD9858等集成芯片的高性能则使系统在杂散和噪声方面也能达到要求。

2 电路设计

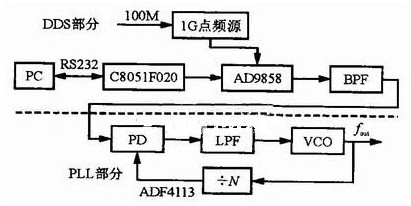

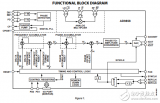

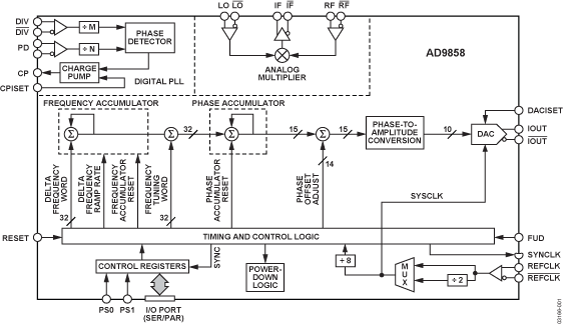

本系统的电路设计主要分为DDS模块和PLL模块两大部分,其系统框图如图l所示。

2.1 DDS模块电路设计

本系统由DDS来保障较高的频率分辨率和良好的参考源性能,而由PLL提高频率输出并滤除DDS输出杂散,跳频方式则通过对DDS和PLL的控制来实现。

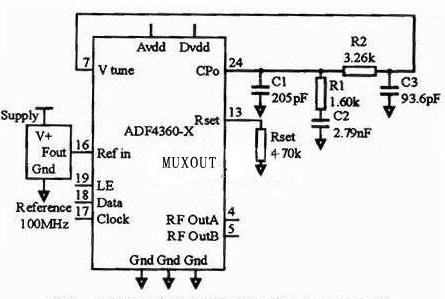

AD9858的外接1 GHz时钟点频源可使用ADF4360_2生成,并可使用ADIsimPLL仿真,其基本电路原理图如图2所示。ADF4360_2的参考时钟使用100MHz有源晶振,实际电路设计时需加入滤波后再接到Ref端口。输出频率为2 GHz,可以设置为2分频输出,也可以在AD9858芯片内部设置为2分频输入。

控制AD9858主要使用C8051F020的特殊功能寄存器SFR、FIASH和外部存储器接口EMIF。其中SFR提供对CIP-51的资源和外设的控制以及CIP -51与这些资源和外设之间的数据交换;FLASH是C8052F020的内部存储器,可通过JTAG接口对其编程;外部存储器接口EMIF则御用访问片外存储器。配置EMIF的流程如下:

(1)将EMIF选到低端口(P3,P2,Pl,P0)或高端口(P7,P6,P5,P4);

(2)选择复用或非复用方式;

(3)选择存储器模式(只用片内,只用片外;不带块选择分片、带块选择分片等);

(4)设置与片外存储器的时序;

(5)选择相关端口的输出方式(寄存器PnMDOUT和P740UT)。

2.2 AD9858的基本原理和性能

DDS是基于查找表的数字频率发生器。DDS器件工作时,其频率控制字K在每一个时钟周期内,其余相位累加器累加一次,而得到的相位值

(O~2π)在每一个时钟周期内则以二进制码的形式去寻址正弦查询表ROM,并将相位信息转变成相应的数字化正弦幅度值,ROM输出的数字化波形经数模转换器(DAC)后,用于实现数字化信号到模拟信号的转变,最后,DAC输出的阶梯序列波再通过低通滤波器(LPF)平滑后,就可得到一个纯净的正弦信号。

AD9858的10位数模转换器可以工作到lGsps,并能够产生高达450MHz的频率阶变模拟输出正弦波,同时具有快速调频和细微的频率分辨率(32位频率分辨率)。AD9858内部有集成的电荷泵(CP)和相位检测器(PFD),可以将高速DDS和锁相环(PLL结合使用)在片内模拟混频,也可以使DDS、PLL和混频器结合使用。

AD9858有单音和扫频两种工作模式。在单音模式下。AD9858可产生由内部寄存器FTW控制的单频输出信号。输出频率与系统时钟的关系可由如下公式确定:

对于AD9858,N=32。可见其频率可以通过改变FTW任意改变,也可以通过外部引脚来选择提前设定在4个存储在寄存器上的频率值来实现快速跳频。

而在扫频模式下,用户需要通过频率控制字(FTW)、频率转换控制字(DFTW)、频率斜率控制字(DFRRW)来设定频率的扫频初始值、频率步进值和频率步进时间,从而实现扫频。

在设计DDS时需要仔细考虑输入和输出的频段:当输出频率靠近fc/n(其中n=3,4,5,6,7;fc为DDS的时钟频率)时,差频信号产生的杂散离输出频率很近,以至于无法使用滤波器器滤除,这种窄带杂散经过倍频还会继续恶化,严重恶化杂散性能,所以,设计时不能使用DDS输出频段靠近和跨越fc/n的频点(其中n=3,4,5,6,7)。本系统中DDS的输入频率为1GHz。因此输出频段为50~100 MHz。这样,输出频道附近就不会出现大的杂散。

2.3 PLL模块设计

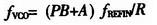

PLL模块包括ADF4113和输出带宽为1~2 GHz压控振荡器。ADF4113的内部结构如图3所示,它由低噪声数字鉴相器、高精度电荷泵、可编程参考分频器(R分频器)、可编程A,B计数器以及双模分频器P/P+1组成。其中6位A计数器、13位B计数器与双模分频器共同组成了N分频器,分频比为N=BP+A。数字鉴相器用来对R计数器和N计数器的输出相位进行比较,然后输出一个与二者相位误差成正比的误差电压。该电压经外部滤波器滤波后可控制外接VCO,从而构成一个完整的频率合成器。其输出频率为:

其中,fREFIN为参考频率。

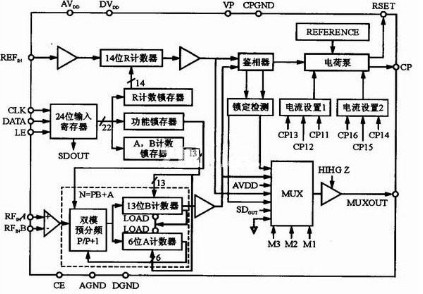

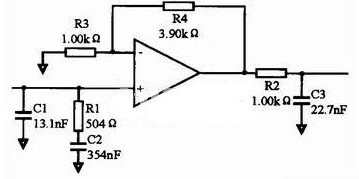

环路滤波器是锁相环电路中很重要的一个部分,它的性能好坏直接关系到锁相输出的相位噪声和杂散指标。设计时仍然可使用AD公司提供的PLL仿真软件ADLsimPLL来生成。其各项参数设置为:输出频率为1~2 GHz。鉴相频率为5 MHz,使用有源滤波,放大器输出电压范围为-15~+15V。该设置可以满足后级电路VCO的控制要求。其环路滤波器仿真电路如图4所示。

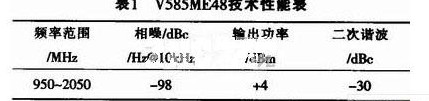

压控振荡器芯片可根据系统带宽等要求选用Z-com公司的V585MFA8,该器件的主要技术指标如表1所列。

注意到VCO的工作电压为10 V。由于本实验电路使用了实验室的直流稳压源OFl722M-2。该电源可以提供0~36V的连续电压。如果使用芯片供电,整个电路需提供3.3 V、5 V、10 V、12 V等4个电压值,故可使用线性电压元件来实现,但要注意电源布局及走线。

2.4 带通滤波器设计

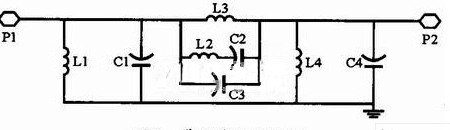

带通滤波器的设计方案直接影响到输出信号的质量。DDS输出信号中含有丰富的高频成份,考虑到电路规模和系统要求,本文采用常用的椭圆滤波方案,并使用三阶滤波器滤除杂散。同时使用ADS滤波器辅助设计,其具体电路如图5所示。其中,L1和L4为41 nH;Cl和C4为137 pF;L2选52 nH;L3选54 nH;C2选108 pF;C3选103 pF。

3 印刷版设计

本设计的印制板可分为两个电路板设计,即把DDS部分与锁相环部分做成一块,而把电源和参考时钟做成另一块。两块电路板采用绝缘子穿孔相连。这样可以有效降低电源部分对DDS与锁相部分的干扰。印刷板都需要大面积铺地,所有的旁路电路均应尽量靠近器件,所有的信号线尽可能的短,而且不能有90度转角。

4 结束语

本文采用AD9858和AD4360_2等高性能芯片来实现1~2GHz符合穿墙雷达系统的信号源系统设计,同时在电路布局等方面都进行了良好的设计,因而使输出信号在杂波抑制和相位噪声方面都有良好的特性。完全可以满足穿墙雷达实验系统信号源部分的设计要求。

-

寄存器

+关注

关注

31文章

5394浏览量

122179 -

频率合成器

+关注

关注

5文章

224浏览量

32554 -

雷达

+关注

关注

50文章

3007浏览量

118671

发布评论请先 登录

相关推荐

AD9858实现雷达宽带调频源设计

用DDS器件AD9858实现复杂雷达信号源 (图)

AD9858 无信号输出

请问怎么计算与AD9858片内PLL结合使用的环路滤波器参数?

AD9910与AD9858的选择

DDS工作原理是?用DDS芯片AD9858宽带雷达信号源要设计最佳?

AD9858,pdf datasheet (1 GSPS D

基于AD9858宽带雷达信号源的设计及应用

DDS器件AD9858实现复杂雷达信号源

1GSPS的直接数字频率合成器AD9858数据表

AD9858 1 GSPS直接数字频率合成器

采用AD9858和AD4360_2实现UHF波段频率合成系统的设计

采用AD9858和AD4360_2实现UHF波段频率合成系统的设计

评论