1 引言

在时分制数字通信系统中,为了扩大传输容量和提高传输效率,常常利用复接技术将 若干个低速数字信号合并成一个高速数字信号流,以便在高速宽带信道中传输。数字复接 器是把两个或两个以上的支路,按时分复用方式合并成一个单一的高次群数字信号设备, 其中包含码速调整结构。

码速调整就是把速率不同的各支路信号,调整成与复接设备定时 完全同步的数字信号,以便由复接单元把各个支路信号复接成一个数字流。 码速调整可以分为正码速调整、正/负码速调整和正/零/负码速调整三种。本文通过 改进了异步FIFO 设计,基于FPGA 提出了一种正码速调整的设计方案, 通过正码速调整, 使输入码率为1200bps,输出码率为1350bps。

2 正码速调整的基本原理

2.1 正码速调整的帧结构

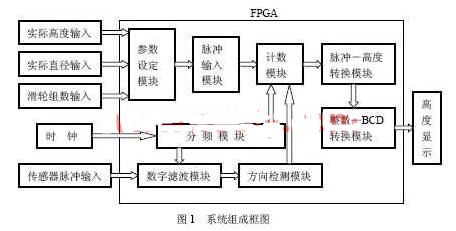

根据设计方案,采用正码速调整的帧结构有32bit,分为四组,每组8bit。正码速调 整的帧结构如图1 所示。

图1 正码速调整的帧结构

第一组8bit 信息,第二、三、四组中的第一个比特C1、C2、C3 为码速调整标志比特。 第四组中第26 bit V 为码速调整插入比特,其作用是调整基群码速,使其瞬时码率保持一 致并和复接器主时钟相适应。具体调整方法是:在第一组结束时刻进行是否需要调整判决, 若需要进行调整,则在V 位置插入调整比特;若不需要调整,则V 位置传输信息比特。为了区分V 位置是插入调整比特还是传输信息比特,用码速调整标志比特C1、C2、C3 来标 志。若V 位置插入调整比特,则在C1、C2、C3 位置插入3 个“1”;若V 位置传输信息比 特,则在C1、C2、C3 位置插入3 个“0”。

2.2 正码速调整系统的构成

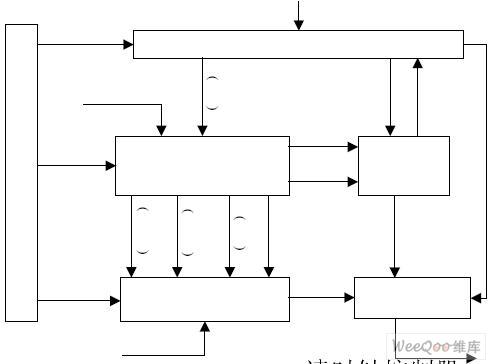

在本方案设计中,采用格雷码对地址编码的异步FIFO 设计,使其满足正码速调整需 要,同时给出了适合格雷码的帧结构。正码速调整系统的构成如图2 所示。

图2 正码速调整系统的构成框图

正码速调整单元主要分为3 个模块:“读时钟、调整、辅助信号发生器”、“异步FIFO 模块”和“调整信号插入”。其中异步FIFO 模块部分包含“地址发生器”、“相位比较器” 和“双口RAM”。

首先将写时钟以及“整体信号控制器”产生的写时钟控制信号送入到“地址发生器”, “地址发生器”通过写时钟上升沿产生的写地址(格雷码)和写时钟一同送入到“双口 RAM”,将写地址(自然码)送入到“相位比较器”。同时未经调整的数据流以及“整体信 号控制器”产生的写使能信号也送入到“双口RAM”。为了准确的将数据写入到双口RAM 中,以写时钟的下降沿将数据写入到RAM 中。

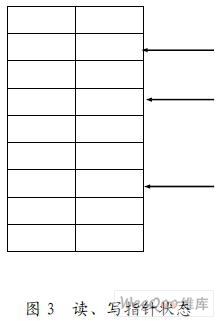

然后当写时钟写到地址“101”时,“整体信号控制器”才将读时钟控制信号送入到“读 时钟、调整、辅助信号发生器”,其结合送入的均匀时钟(1350HZ)产生扣除调整标志位 的非均匀读时钟送入到“地址发生器”,同时将控制状态位的辅助信号送入到“相位比较 器”,将调整信号送入到“调整信号插入”。扣除的读时钟通过“地址发生器”将读地址(自 然码)送入到“相位比较器”,将读地址(格雷码)和扣除读时钟送入到“双口RAM”。 此时RAM 通过读时钟上升沿依次从地址“000”开始读取数据。原理图如图3 所示。

随着时间的推移,读指针与写指针之间的距离逐渐变小,当相位比较器计算出读、写 地址差值小于门限值“100”时,则在图3 中第8 个比特位置给出高电平的存储状态位告 知系统缓存器即将取空,然后在第32 个比特位置将存储状态位再次置“0”,等待下一次 的状态判断。

最后,“调整信号插入”根据存储状态位的电平决定数据流中的调整位是插入3 个“1”还是3 个“0”。

3 正码速调整的FPGA设计

3.1 读时钟、调整、辅助信号发生器模块

该模块的主要作用在于根据存储状态来生成扣除调整位的缺口读时钟,同时产生调整 信号以及相关辅助信号。

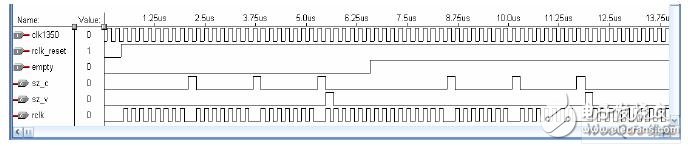

扣除前读时钟首先通过32 位计数器,当读时钟控制开启时,计数器开始计数。在第9, 17,25 个比特位时置调整标志位高电平;在第26 个比特位置调整位高电平;在第8 个比 特和第32 个比特位上辅助信号分别显示“00111”和“11111”计数值。

当存储状态位为“1”时表示存储器即将取空,第26 比特处的读时钟脉冲扣除,不传 信码,其逻辑门的关系如下: r_clk<=(rclk_reset and(clk1350 and (not sz_c))and ((not empty)or(not sz_v))); 其中,r_clk 为扣除后读时钟,rclk_reset 为读时钟控制,clk1350 为读时钟1350HZ,sz_c 为调整标志位,sz_v 为调整位,empty 为存储状态位。 具体仿真波形见图4 所示。

图4 读时钟、调整、辅助信号发生器仿真图

3.2 异步FIFO 设计

此部分为本文的关键部分,FIFO 设计的好坏直接影响系统性能。

(1)地址发生器模块

该模块主要功能在于根据读、写时钟以及时钟控制信号生成相应的读、写地址的自然 码和格雷码。由于读地址要在写地址写到“101”时才开始从地址“000”读取数据,因此读时钟控制信号是由写时钟控制信号延迟5 个写时钟周期产生的。

(2)相位比较器模块

根据由“读时钟、调整、辅助信号发生器模块”中产生的辅助信号在每帧的第8 比特 位置上判断存储状态是否为“空”,若为“空”则在第8 比特位上置存储状态位高电平, 然后再次根据辅助信号在第32 比特位置上将状态辅助位置回初始状态―低电平。

判决器主要是在辅助信号值为“00111”时,判断差值是否小于设置的门限“100”,若 小于“100”则存储状态置“1”,然后在辅助信号为“11111”时将存储状态置“0”;若大 于“100”,存储状态维持初始状态“0”。

(3)双口RAM 模块

RAM需要大量的存储空间,若直接用数组的形式来描述RAM 时,资源利用率相当低。 因此本文选取IP 核来定制RAM,直接生成宽度为1,深度为8 的带写使能的双口RAM, 写时钟为下降沿有效,读时钟为上升沿有效,写使能为高电平有效。

3.3 调整信号插入模块

该模块主要作用就是将扣除调整位后的数据流根据存储状态位在调整标志位插入 “000”或“111”。若插入的是“000”,则在第26 比特传信码,若插入的是“111”,则在 第26 比特传“1”。其逻辑关系为:

if empty= '1' then

dout<=(din or (sv or sc));

elsif empty= '0' then

dout<=((not sc) and din);

end if;

其中,din 为扣除调整位后的数据,dout 为正码速调整后的数据,由于插入后存在毛刺,于是在其后端加了个D 触发器去除了毛刺。

4 整体仿真结果

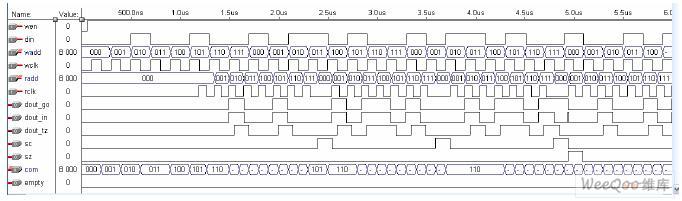

最后在MAXPLUS II 开发平台上采用原理图输入方式,根据同步单元各个功能模块的划 分,将各个功能模块连接起来,编译成功,其整体仿真如图5 所示。

图5 整体仿真图

其中 dout_go 表示扣除调整位置后的数据流,dout_in 表插入调整信号后的数据流, dout_tz 表示加了D 触发器的调整数据流。由图可知,当wen 为高电平时,开始写入数据 “00100100”到写地址wadd,当写到地址“101”时,读时钟开始工作,依次从地址“000” 开始从RAM 中读取数据。当到第8 比特位置时,由于地址差值为“101”未到达门限,因 此存储状态位empty 仍旧为“0”表示不需要调整,则在帧的调整标志位置上插入3 个“0”, 调整位继续传信码。在dout_go 上最后一个调整标志位由于插入了“0”,可以清晰的看到由此带来的毛刺,但加了D 触发器后的dout_tz 已成功的消除了这个毛刺。

5 结论

系统仿真波形良好,能准确实现正码速调整,本系统采用芯片EP1K100Q208 实现。通 过正码速调整,可以把调整后的数字信号进行复接,扩大了传输容量,提高了传输效率。

-

FPGA

+关注

关注

1630文章

21762浏览量

604464 -

芯片

+关注

关注

456文章

50968浏览量

424996 -

宽带

+关注

关注

4文章

991浏览量

60384

发布评论请先 登录

相关推荐

基于EP1C6Q240C8的FPGA芯片实现电子测试系统的设计

EP2C8Q208C JTAG下载的奇怪现象,大家讨论下

EP2C5T144C8、EP2C8T144C8、EP2C8Q208C8这三种芯片的区别

EP2C5T144C8、EP2C8T144C8、EP2C8Q208C8这三种芯片的区别

想要EP2C5Q208C8芯片的中文资料,特别是引脚的对应表!十分...

发现EP1K100QI208-2 IC的VCC和GND引脚之间频繁短路

回收EP2C8Q208C8N,收购EP2C8Q208C8N

EP2C8Q208C8芯片时钟主频由50MHz生成400Hz有何作用

EP2C6Q208+AMD29LV160+HY57V6416

基于FPGA的手持式数字存储示波器显示驱动设计

STEVAL-MKI208V1K STMicroelectronics STEVALMKI208V1Ki Nemo惯性模块套件

基于FPGA和EP1K100Q208芯片的正码速调整的设计

基于FPGA和EP1K100Q208芯片的正码速调整的设计

评论