传统的频率特性测试仪不仅价格昂贵,且得不到相频特性,更不能保存频率特性图和打印频率特性图,也不能与计算机接口,给使用者带来了诸多不便。而本文采用DDS技术作为扫频信号源;同时采用了集成模拟芯片AD8302对幅度和相位进行检测,用DSP芯片TMS320VC5409和CPLD芯片EPM7128进行测量控制和数据处理,人杌接口部分是利用单片机AT89C51实现,并配有打印机接口和串行通信接口。

1 系统总体方案设计

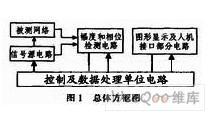

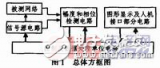

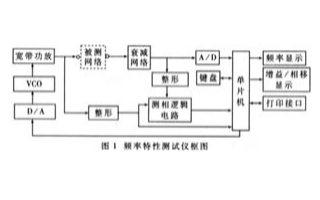

频率特性测试系统一般包含测试信号源、被测网络、检波及显示3个部分。本系统根据所要完成的测试功能及技术指标,该系统应由扫频源、幅度相位测量电路、控制及运算部分、人机接口单元几部分组成。系统总体方框图如图1所示。

信号源电路由信号发生电路和信号调理电路两部分组成。在本系统中信号发生电路采用DDS技术(即直接数字频率合成技术)实现,用于产生频率、持续时间等均可控的扫频信号,并能够满足一般用户对频率范围的要求;信号调理电路主要是对信号中的噪声进行抑制并对输出信号的功率起到控制作用。

增益相位检测电路是为了检测被测网络两端的幅度差和相位差。先对被测网络两端的信号进行预处理后对其进行模拟鉴幅和鉴相,然后把幅度差和相位差的模拟量由ADC转化为数字量,送给控制及数据处理电路进行分析处理。

控制及数据处理电路要完成逻辑控制、数据处理和与人机接口部分通信3个主要功能,由DSP和CPLD组成。主要用于控制整个系统的协调工作,并对测量及人机接口部分来的数据进行分析处理。

图形显示及接口电路负责接收各种指令和显示测量结果,测量时扫频信号所需要的起始频率、终止频率、频率问隔、单频点持续时间、信号功率等参数,以及测量完成后显示特性曲线时显示方式的设置,如:刻度大小选择、文字标注方式、坐标选择等。

2 系统硬件设计

系统由扫频源、幅度相位测量电路、控制及运算部分、人机接口单元几部分组成。

2.1 扫频信号源设计

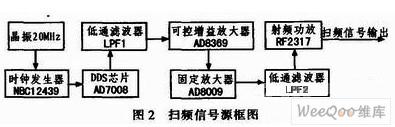

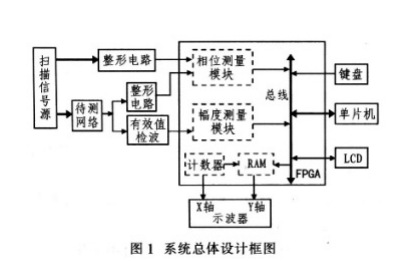

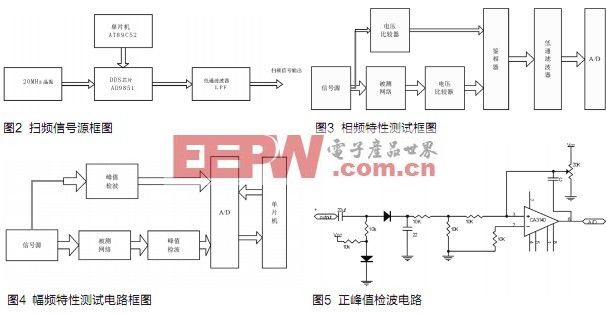

直接选用DDS技术设计扫频信号源。从设计要求低频和成本考虑,这里选择AD7008系列中20 MHz芯片。扫频信号源框图如图2所示。由于AD7008内部没有时钟发生电路,所以需要外部时钟源提供时钟信号,本系统采用NBC12439为AD7008提供时钟信号。

由于AD7008输出信号的幅度不能达到系统所要求的-55~+18 dBm的范围,故需要对信号进行放大,放大电路的设计较为简单,为了便于对输出信号的功率控制使用了可控增益放大器,易于数字控制增益的大小;又因为输出信号的最大功率要达到+18 dBm且信号频率最高达5 MHz,普通的运放难以达到要求,故使用射频放大器来提升信号的输出功率。AD7008所产生的信号直接由器件内部的DAC输出,内部不含低通滤波器,故要对其输出信号进行滤波处理。

2.2 幅度相位检测电路的设计

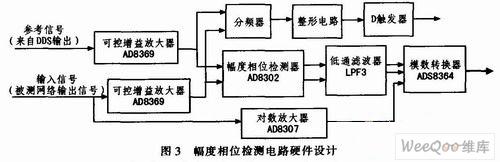

介绍用幅度相位检测芯片AD8302来检测被测网络的幅度和相位,及其信号调理电路,以及模拟/数字转换电路和相位的极性判断电路。由于增益相位检测器AD8302要求被检测的两路信号功率在-60~0dBm范围内,为防止损坏器件,需对两路信号进行功率调整,本系统使用了易于数字控制增益的可控增益放大器AD8369和对数放大器AD8307构成一个反馈系统进行自动调整。对数放大器AD8307可以对信号的幅度进行检测,通过被检测到的幅度范围,系统调整可控增益放大器AD8369的放大倍数,使增益相位检测器AD8302能够有效地对被测网络的增益和相位进行检测。将模拟增益和相位检测结果转化为数字量的方法是采用ADC,由于检测结果是个慢变信号,因此对ADC的速度要求较低,本系统中具有3路模拟量要转化为数字量,因此选用了多通道模数转换器件——ADS8364。幅度相位检测电路的硬件设计方案如图3所示。

由于AD8302检测的相位是0~180°之间,不能给出相位是超前还是滞后,所以需要相位极性判断电路对相位进行判断,其电路主要由分频器电路、施密特触发器、D触发器等组成。

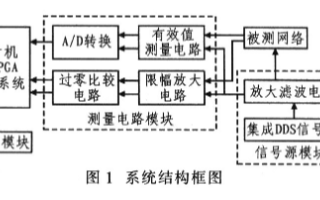

2.3 数据处理及控制电路设计

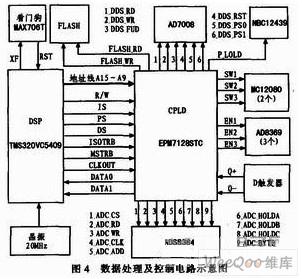

数据处理及控制单元主要完成通信、数据处理、功能控制等工作。主要由TMS320VC5409、晶体振荡器、电源控制、WATCHDOG和CPLD等器件组成。

2.3.1 电路设计

这一部分电路是数字电路,所用器件均为数字器件,核心芯片是TI公司的数据处理芯片TMS320VC5409和ALTEM公司的CPLD芯片EPM7128。电路结构图如图4所示。

系统是对电网络进行实时测量,在测量过程中要采集大量的数据,对这些数据还需要进行数字滤波等方法来提高准确度,系统必然需要大数据量的运算,而单片机的运算能力弱不能达到实时处理的要求,故采用DSP作为数据处理电路的核心,考虑到系统成本因素采用TI公司的54系列DSP。

在选择可编程逻辑器件时,容量大小是需要考虑的最基本问题。故在器件选择前,先确定完成设计功能所需逻辑资源的多少,本系统对CPLD所要完成的功能经仿真、综合后,约需占用1 500门左右的逻辑资源。综合考虑之后选择了Altera公司Max7000系列的EPM7128。

在图4中TMS320VC5409通过主机接口(HPI)接受单片机系统来的各种控制命令,并通过EPM7128STC控制扫频信号源中的时钟发生器NBCl24 39、DDS芯片AD7008和可控增益放大器AD8369产生信号功率可控的扫频信号;控制增益相位检测电路中的2个可控增益放大器AD8369和A/D转换器ADS8364进行信号检测;据输入信号频率对两个MC12080的分频比进行控制;选通D触发器读入相位极性。

2.3.2 看门狗电路设计

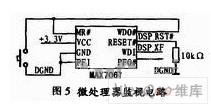

由于本系统是一个独立的系统,且DSP系统的工作时钟频率较高,在运行时极有可能发生干扰和被干扰,严重时系统可能会出现死机现象,为了克服这个毛病,除了在软件上做一些保护措施外,在硬件上也必须做相应的处理。硬件上最有效的保护措施通常采用具有监视功能(WATCHDOG)的自动复位电路。

其基本原理是电路提供一个用于监视系统运行的信号,当系统运行正常时,应在规定的时间范围内给监视线一个高低电平发生变化的信号,如果在规定的时间内这个信号不发生变化,自动复位系统就认为系统运行不正常并重新对系统进行复位。本系统采用MAXIM公司的微处理监视电路MAX706-T实现对系统的监视,电路如图5所示。

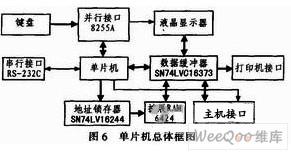

2.4 单片机系统设计

本系统主要功能是完成人机接口功能和通信功能,包括键盘、液晶显示器、标准串行接口、微型打印机接口和与DSP通信的HPI接口等。单片机系统总体框图如图6所示。

单片机是用AT89C51,通过1片8255A来扩展其并口,8255A的C口用于键盘接口,A口接到打印机数据线,打印机的控制线接于单片机的P1口(占3位),8255A的B口对液晶显示器进行控制,液晶显示器的数据线通过缓冲器接于单片机的P0口。HPI接口完成与DSP的通信。

3 系统软件设计

系统电路的软件设计包括DSP软件设计和CPLD的软件设计。

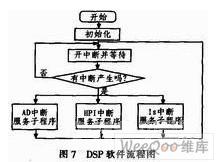

3.1 DSP软件设计

DSP软件的设计使用了TI公司的CCS开发工具,通过DSP仿真器进行调试,使用C语言和汇编语言混合编程。

DSP软件程序主要功能是通过中断方式从单片机系统中得到各种设置参数和命令,并根据这些参数和命令进行相应设置和相应操作,并将采集的数据处理后送单片机系统显示。另外还要照看看门狗。其程序流程图如图7所示。

3.1.1 主程序设计

系统上电后,TMS320VC5409内部固化的加载程序检测到外部8为并行加载方式有效,则将存储在AT29C010A中的源程序取出存入内部SRAM中。源程序占据FLASH的低32 K地址空间0000H~7FFFH,同时映射在DSP外部数据存储空间8000H~FFFFH。加载过程中DSP软件上自动设置7个等待周期,可保证数据存取正确。加载完毕程序开始顺序执行,首先设置定时器,开定时器中断,使其在每低于0.8 s的时间内产生一次中断,在定时器中断子程序中设置专用输出管脚XF,使看门狗的输入端定时产生变化,否则其将产生DSP的RESET信号。然后,对系统进行初始化,初始化结束后。为了降低系统功耗可使DSP进入空转状态(IDLE),直到中断发生。程序流程如图8所示。

初始化包含DSP初始化、AD7008初始化以及AD8369的初始化。DSP的初始化主要是对中断向量的定义,内部时钟的设置,外部等待时间的设置以及内部空间SRAM/DRAM的映射等,这些都是通过对DSP内部专用寄存器的设置来完成的。AD7008的初始化可通过设置控制寄存器来完成。AD8369的初始化是把AD8369的放大倍数降为最小-10 dB,可以减少信号源电路的射频功放的功率,也可以保护增益与相位检测电路中增益鉴相器AD8302,使AD8302的输入信号功率保持为最低,防止输入信号功率过大损坏器件。

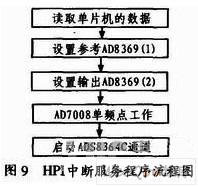

3.1.2 HPI中断服务程序设计

HPI口是连接单片机与DSP的接口,通过HPI口,主机也就是单片机可以向DSP写数据,也可以从DSP的RAM单元读取数据;同时通过HPI口控制寄存器提供的中断位,以及HPI的中断信号中断单片机,主机和单片机可以实现很好的对话。并且,根据单片机来的数据,进行相应操作。其流程图如图9所示。

AD7008单频工作的目的是为了检测输入信号的幅度范围,从而设置输入AD8369的增益倍数。AD7008以起始频率为频率点进行单频工作,输入信号的幅度检测由AD8307来完成,检测结果由ADS8364的C通道进行数据转换,供DSP采集。当采集到的数据个数达到系统设置值后,DSP对数据进行处理,判断出输入信号的幅度,以设置检测电路中AD8369(2、3)的增益。

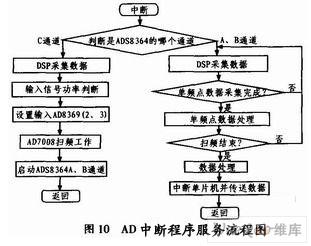

3.1.3 AD中断服务程序设计

在AD中断服务子程序中,主要是对采样数据的读取,如果是ADS8364的C通道的数据则是对输入信号进行幅度判断:如果是ADS8364的A,B通道的数据则是进行幅度相位的测量。测量结束后,将处理好的数据送单片机显示。其流程图如图10所示。

通过C通道判断以后,就设置好了检测电路中的AD8369(2、3),完成了扫频测试前的准备工作,AD7008可以开始扫频工作了。按照起始频率、频率步长、单频点持续时间等对AD7008相应寄存器进行设置,使AD7008输出满足要求的扫频信号;紧接着启动ADS8364的A、B两通道进行数据的转换,其转换的是AD8302的增益和相位检测电压:DSP在中断服务子程序中对ADS8364进行数据采集。并做以下工作:接收采集数据,判断单频点采集到的数据量,进行单频点数据的数字滤波和简单计算处理,判断扫描频率点数是否达到要求,决定扫频是否结束,将数据转换成图形显示格式送单片机显示。

3.1.4 1s中断服务程序设计

1s中断服务程序较为简单,就是照看看门狗,看门狗是系统稳定运行的重要部件,由于系统的高速运行,外界的干扰以及程序内部的有关问题,都有可能导致系统的运行不稳定,甚至出现死机的情况。设置看门狗就是在系统出现意外而导致运行紊乱、死机时,自动恢复运行的保证。在系统出现上述情况时,当时间超过1 s时,看门狗将自动重新启动系统。相关内容在系统硬件设计部分有涉及。

3.2 CPLD软件设计

CPLD的软件设计使用MAXIM公司的MAX+PLUSII开发工具,使用VHDL语言进行编程。这部分程序主要是对来自DSP的信号进行译码后,对各个器件进行控制,使整个系统协调工作,完成测量任务。其设计流程图如图11所示。

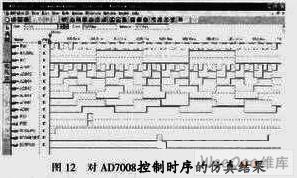

图12是CPLD对AD7008控制时序的仿真结果。从图中可以看到,当IOS和IOSTRB信号为低电平(这时DSP选中IO空间)时,CPLD芯片对DSP的高位地址(ADD15~ADD9)进行译码,当高位地址为00H时,选中AD7008芯片,并在DSP读写信号RW为低时,DDSWRB变为低电平,即对AD7008进行写入操作;当高位地址为78H时,CPLD使DDSRESET信号变为低电平,即对AD7008进行复位操作;当高位地址为01H时,CPLD使DDSFUD信号变为高电平,否则变为低电平,此信号在上升沿对AD7008内部存贮器进行更新操作。可以看出,仿真结果符合要求。

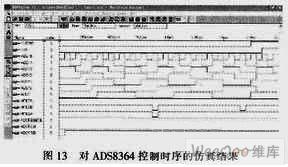

图13是CPLD对模数转换芯片ADS8364的仿真结果,同样,当IOS和IOSTRB信号为低电平(这时DSP选中10空间)时,CPLD芯片对DSP的高位地址(ADD15~ADD9)进行译码,当高位地址为20H时,ADCRESETB信号输出低电平,对AD8364进行复位操作;当高位地址为30H时,ADCCSB信号输出低电平,对ADS8364进行片选;当最高四位地址(ADD15~ADD12)为0CH时,由ADD11、ADD10、ADD9三位译码决定HOLDC、HOLDB、HOLDA的输出电平;这3个信号分别控制ADS8364的3个采样通道的转换。由图可以看出,其仿真结果符合要求。

4 测量结果

扫频范围0.004 7 Hz~5 MHz,可以在全频段内任意设置扫频宽度,分辨率为0.004 7 Hz,输出电平范围-55~+18 dBm,扫频步长可以在0.004 7 Hz~0.5 MHz范围内自行调整;输出阻抗50 Ω,相位测量精度小于0.1°,幅度测量精度小于0.5 dB,不平坦度+/-0.25 dB,电控衰减并数字显示衰减量,能在全频范围内自动步进测量,可预置测量范围及步进频率值。能显示幅频特性和相频特性曲线,并能根据选择,放大局部曲线,可以用对数坐标和线性坐标显示,并配有文字标注。

5 小结

本系统设计适用于科研、教学以及生产领域等方面,与传统的频率测试仪相比,用直接数字频率合成(DDS)技术为频率特性测试仪实现数字化开辟了道路,利用液晶显示器技术使频率特性测试仪小型化成为可能。此测试仪有很强的应用价值,可取代传统的频率测试仪。

-

dsp

+关注

关注

552文章

7962浏览量

348236 -

芯片

+关注

关注

453文章

50384浏览量

421724 -

单片机

+关注

关注

6032文章

44513浏览量

632850 -

DDS

+关注

关注

21文章

631浏览量

152536

发布评论请先 登录

相关推荐

基于单片机和FPGA的频率特性测试仪

基于DSP的低频频率特性测试仪

低频频率特性测试仪设计方案解析

MSP430单片机和DDS技术的频率特性测试仪的设计详析

低频段数字式频率特性测试仪的特性功能和实现设计

如何使用单片机和FPGA为核心实现频率特性测试仪的设计

采用DDS技术与AD8302芯片实现了数字化频率特性测试仪的设计

采用DDS技术与AD8302芯片实现了数字化频率特性测试仪的设计

评论