液晶显示器是 Liquid Crystal Display 的简称,LCD 的构造是在两片平行的玻璃当中放置液态的晶体,两片玻璃中间有许多垂直和水平的细小电线,透过通电与否来控制杆状水晶分子改变方向,将光线折射出来产生画面。比CRT要好的多,但是价钱较其贵。生命周期设计(Life Cycle Design)又称生态设计(Eco-Design)。它是从产品性能、环境保护、经济可行性的角度,考虑产品开发全生命周期(包括产品设计、原材料的提取、产品的制造、包装、销售和使用、用后的回收与处置全过程)的污染预防要求,多级使用资源与能源,以降低产品生产和消费过程对环境的影响,使其与地球的承载能力相一致。

LCD投影机按内部液晶板的片数可分为单片式和三片式两种,现代液晶投影机大都采用3片式LCD板。三片式LCD投影机是用红、绿、蓝三块液晶板分别作为红、绿、蓝三色光的控制层。光源发射出来的白色光经过镜头组后会聚到分色镜组,红色光首先被分离出来,投射到红色液晶板上,液晶板“记录”下的以透明度表示的图像信息被投射生成了图像中的红色光信息。绿色光被投射到绿色液晶板上,形成图像中的绿色光信息,同样蓝色光经蓝色液晶板后生成图像中的蓝色光信息,LCD投影机体积较小、重量较轻,制造工艺较简单,亮度和对比度较高,分辨率适中,现在LCD投影机占有的市场份额约占总体市场份额的70%以上,是目前市场上占有率最高、应用最广泛的投影机。

1 模块结构

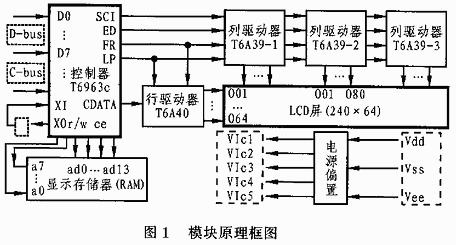

DMF5005N模块的整体结构原理图如图1所示。它主要由以下几个单元电路组成:

●控制电路

主要由控制器T6963C组成,可提供与外部CPU的数据接口及对显示存储器的读写操作;并可控制行、列驱动电路的时序电路、数据格式和显示格式等。

●行驱动电路

由行驱动器T6A40组成,用于把控制器的串行数据转换成LCD屏所需要的并行的行数据。

●列驱动电路

由三片列驱动器T6A39组成,可接受控制器的串行数据并将其转换成LCD屏所需要的并行列数据。

●电源偏置电路

主要为行、列驱动器电路提供LCD屏所需的各种偏置电压。

●显示存储器

由一块8k的随机存储器(RAM)组成,可为模块提供显示数据的存储空间。

●液晶显示屏(LCD)

液晶显示器按照控制方式不同可分为被动矩阵式LCD及主动矩阵式LCD两种

用于提供64行、240列的点阵显示屏幕。

工作原理:我们很早就知道物质有固态、液态、气态三种型态。液体分子质心的排列虽然不具有任何规律性,但是如果这些分子是长形的(或扁形的),它们的分子指向就可能有规律性。于是我们就可将液态又细分为许多型态。分子方向没有规律性的液体我们直接称为液体,而分子具有方向性的液体则称之为“液态晶体”,又简称“液晶”。液晶产品其实对我们来说并不陌生,我们常见到的手机、计算器都是属于液晶产品。液晶是在1888年,由奥地利植物学家Reinitzer发现的,是一种介于固体与液体之间,具有规则性分子排列的有机化合物。一般最常用的液晶型态为向列型液晶,分子形状为细长棒形,长宽约1nm~10nm,在不同电流电场作用下,液晶分子会做规则旋转90度排列,产生透光度的差别,如此在电源ON/OFF下产生明暗的区别,依此原理控制每个像素,便可构成所需图像。

2 控制器T6963C的原理及功能

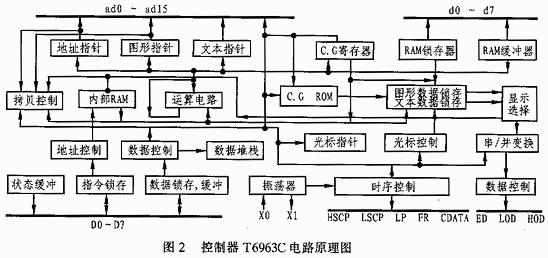

图2所示为控制器T6963C的原理框图,它是DMF5005N的控制中心。

2.1 时序电路

T6963C的时序电路用于为芯片自身以及LCD行、列驱动器产生各种所需时序。首先由芯片内置振荡器与外加晶振构成的振荡电路产生主频信号,此信号经时序控制器多次分频后再产生各种时序信号。CDATA为行同步信号;LP为行驱动器的移位时钟脉冲,同时又是列驱动器的数据锁存脉冲信号,HSCP及LSCP分别是双屏模式时的上屏和下屏的移位时钟脉冲信号。T6963C的主时钟频率为2.0~5.5MHz,显示占空比的调节可由引脚编程解决:并可在1/16到1/128之间进行调节。在DMF5005N中选用5.0MHz的晶振并接于XI与X0端可将其占空比定为1/64。

2.2 指令处理功能

T6963C有十条基本指令,主要有:数据的读/写、显示存贮器的寄存器指针设置、控制字设置、工作模式设置、显示模式、光标形状选择、位设置、屏幕拷贝以及屏幕搜索等功能。这些指令通常通过CPU由8位数据总线(D0~D7)输入[1]。

2.3 显示存贮器RAM的控制和管理

T6963C通过ad0~ad15共16根地址线可导址64k字节的存贮空间,在DMF5005N模块中内置了一片8k的低功耗静态存储器,所以仅用了13根地址线。数据由d0~d7共8位并行口与显示存贮器RAM进行传递。片内设置有文本指针、图形指针、用户字符发生器指针及地址指针等寄存器。可通过软件指令对这些寄存器进行设置,并可将显示存贮器划分成文本显示区、图形显示区、以及由用户自定义的字符存贮区,用户所要显示的文本、图形或自定义图符的数据将被存放到相应的存贮区内。内置的RAM数据锁存器及RAM缓冲器可为与外接RAM之间数据的传递提供保障。

2.4 显示内容及模式控制电路

在显示时,显示数据分别经图形数据锁存器以及文本数据锁存器锁存,再由显示根据显示模式设置控制选择所要显示的是文本还是图形,或者是二者的组合模式。当选定后,即可对选定数据区进行扫描,对应的显示数据经串行变换后转化成LCD串行数据并串行输出到列驱动器。ED、HOD和LON引脚为数据输出端子。可根据采用单屏驱动还是双屏驱动来选定这三个引脚中的其中一个或两个引脚。DMF5005N模块采用单屏驱动,因此选定ED引脚。

3 T6A40芯片的工作原理及功能

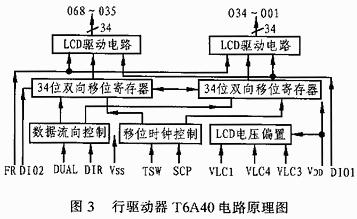

行驱动器T6A40驱动器芯片具有68个通道输出(01~068),并有两个可用来传递数据的双向数据输入端子,通过此两端与其它引脚的编程组合,可以改变输出数据的流向。T6A40芯片的内部电路原理框图如图3所示。

将控制器的FR接T6A40的FR端,并将VLC1、VLC4、VLC5接到电源偏置电路的对应端子,即可保证驱动器输出的是LCD屏的行驱动电平。

T6A40片内有两个34位双向移位寄存器,串行数据可从DI01与/或DI02两个端子输入。由移位寄存器产生的并行输出数据澈同可分三种:第一种为01~068;第二种是068~01;第三种流向是01~034和068~035,具体输出哪一种取决于来自数据流向控制和移位时钟极性控制电路的信号,数据流向控制电路根据单/双屏选择端子DUAL和流向选择端子DIR的逻辑电平产生流向控制信号。移位时钟的极性控制信号由控制器的移位时钟脉冲SCP(控制器的LP信号)和触发方式选择端子TSW的逻辑电平来产生。两个34位双向移位寄存器产生的两个34位并行数据将输出到两个LCD驱动电路中,并在CLD电源偏置电压作用下产生68位并行LCD行输出信号,最后加到LCD屏的行输入端。

在DMF5005N模块中,由于DUAL=DIP=L;因此选择DI02为同步数据信号的输入端(控制器的CDATA信号),而将DI01悬空。这样,产生的数据流向为068~01。因此模块是240×64点阵液晶显示屏,且只用到64行输出,所以将065~068四个输出悬空。

4 列驱动电路T6A39的原理功能

利用列驱动电路可把控制器提供的串行数据转换成LCD屏所需的并行数据。一般列驱动芯片都是80个输出端子,模块为240列输出,DMF5005N模块采用三片T6A39芯片相联,正好能构成240列输出,T6A39芯片的内部电路原理框图如图4所示。

T6A39可以接收一位串行或两位及四位并行数据,可由DF1及DF2引脚输入数据位选择器确定并控制输入数据具体格式以及串/并数据变换的管理控制。该电路内含两个40位输出的双向移位寄存器,它们将根据数据流向控制器及驱动时序控制器把接收到的串行数据变换成符合要求的并行数据,并传递给两组LCD驱动电路。驱动电路的作用是在LCD电压偏置电路供给的偏置电压下,将得到的80位并行数据数据转换成LCD所需的并行输出(001~080)数据信号(电平)。

5 电源偏置电路

DMF5005N模块电源采用双电源方式:一个是VDD(+5伏);另一个是VEE(-12伏)。为了得到LCD驱动电压信号,该模块在采用电阻分压加上射极跟随稳压时可得到VLC1~VLC5五个输出电压。为了得到LCD显示的清晰度,负电源VEE应该经过可调电位器调节后施加到模块上。其可调范围为:-6~-12伏。对应的LCD各驱动电压为:

VLC1=VDD-(VDD-VEE)/9(V);

VLC2=VDD-2(VDD-VEE)/9(V);

VLC3=VDD-7(VDD-VEE)/9(V);

VLC4=VDD-8(VDD-VEE)/9(V);

VLC5=VEE(V)。

电源偏置电路由四运算放大电路组成的射极跟随器构成。此外,其它的辅助电路如存储器RAM、振荡电路等都比较简单,而控制器、行和列驱动器之间的连接可参考DMF5005N模块的整机电路原理图来进行。

6 结束语

根据上述原理,选用日本东芝公司的上述芯片,并在DMF5005N的基础上设计制作了两块显示模块。经测试表明:制作的显示模块的各种电气性能和输入输出信号波形都达到了同类进口产品的技术要求。经与8031单片机联机运行演示,各种显示功能与DMF5005N完全一致。

:

-

lcd

+关注

关注

34文章

4474浏览量

169540 -

存储器

+关注

关注

38文章

7579浏览量

165389 -

液晶显示器

+关注

关注

11文章

580浏览量

43936

发布评论请先 登录

相关推荐

12864点阵图形液晶显示屏,128X64 COB全新原装黄绿膜无背光

480X64分辨率液晶显示屏 LCD LCM 48064 480*64 点阵图形液晶显示模块

LCD 240128 LCM 240X128 COG点阵图形液晶显示屏 240*128 TM240128KCFWUGRC1

5.7寸320240带8835控制器全新液晶显示屏 240128全新点阵图形液晶显示模块 LCD LCM

12864中文LCD液晶显示模块原理与设计资料推荐

FYD12864-0402B液晶显示模块使用手册

带中文字库图形点阵液晶显示模块LCMxxZK使用说明书

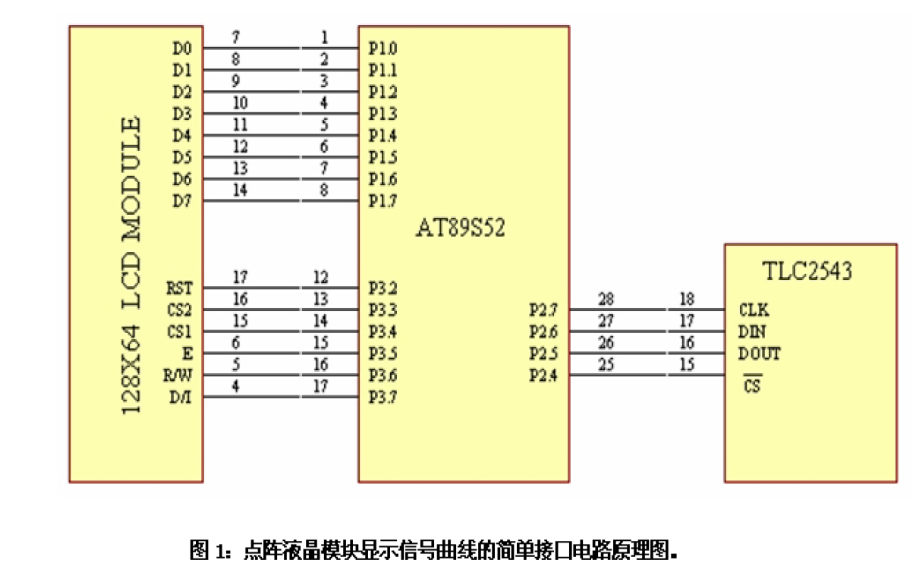

MGLS12032A点阵图形式液晶显示模块与8031单片机的接口设计

LCD12864使用点阵图形液晶模块显示信号曲线的资料说明

DMF5005N点阵图形液晶显示模块电路的结构、工作原理和功能分析

DMF5005N点阵图形液晶显示模块电路的结构、工作原理和功能分析

评论