引言

256级灰度LED点阵屏在很多领域越来越显示出其广阔的应用前景,本文提出一种新的控制方式,即逐位分时控制方式。随着大规模可编程逻辑器件的出现,由纯硬件完成的高速、复杂控制成为可能。

逐位分时点亮工作原理

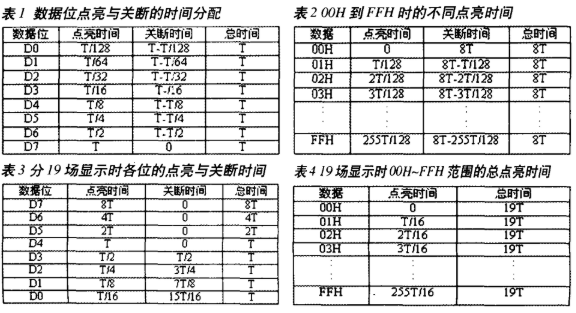

所谓逐位分时点亮,即从一个字节数据中依次提取出一位数据,分8次点亮对应的像素,每一位对应的每一次点亮时间与关断时间的占空比不同。如果点亮时间从低位到高位依次递增,则合成的点亮时间将会有256种组合。定义点亮时间加上关断时间为一个时间单位,设为T 。表1列出了每一位的点亮与关断的时间分配。

如果定义数据位“1”有效(点亮),“0”无效(熄灭),则表2列出了数据从00H到FFH时的不同点亮时间。由表2可知:数据每增1,点亮时间增加T/128。根据点亮时间与亮度基本为线性关系的原理,从0~255T/128的点亮时间则对应256级亮度。当然,这个亮度是时间上的累加效果。如果把一个LED点阵屏所有像素对应的同一数据位点亮一遍称为一场的话,那么8位数据共需8场显示完,称为“8场原理”。

理论上讲,8场即可显示出256级灰度,然而通过表2可看出,即使数据为FFH时,在8T时间内也只是点亮了255T/128时间。关断时间可接近6T,点亮时间仅为总时间的约25%,因此,8场原理虽也能实现256级灰度显示,但亮度损失太大。为了提高亮度,可采用“19场原理”,即8位数据分19场显示完,其中D7位数据连续显示8场,D6位连续显示4场,依次递减。表3列出了各位的点亮与关断时间。

由表3可推导出数据从00H~FFH范围的总点亮时间,如表4所示。在19T时间内,最大点亮时间可达近16T, 占总时间的84.21%,远大于“8场原理”的25%。数据每增1,点亮时间增加了T/16 ,该值大于“8场原理”的T/128。所以 ,“19场原理”较“8场原理”的对比度更明显,图像层次分明、表现力强。

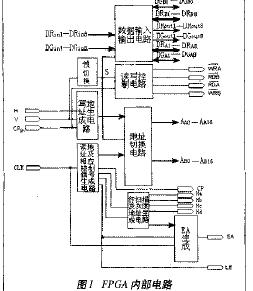

256级灰度LED点阵屏通常要具有能远程同步实时显示计算机视频信号的功能,涉及到的电路包括:数字视频信号的采集、数字信号的格式转换及非线性校正、远程传输及接收、灰度显示控制电路、LED点阵显示电路等。 本文重点讨论“灰度显示控制电路”的设计,控制对象以红、绿双基色LED点阵屏、1/16扫描显示电路为例。FPGA内部电路如图1所示。

因为被控对象为1/16扫描显示电路,所以显示屏每16行只需要一路数据信号即可。DRout1、 DGout1即为第一个16行的红、绿基色输出信号;DRout2、DGout2为第2个16行的红、绿基色输出信号。以此类推。

Ha、Hb、Hc、Hd的二进制编码,定义当前的数据输出应是16行中的哪一行。CP信号为数据串行输出的同步移位脉冲。LE信号为一行串行数据输出结束后的锁存脉冲, LE每有效一次,Ha、Hb、Hc、Hd二进制编码状态增1。EA为灰度控制信号,其宽度为在一个时间单位T内LED的点亮时间。当然, 不同的数据位其宽度不同, 具体由表3决定。一个时间单位T即一行串行数据的传输时间,也即LE信号的周期,其大小取决于屏宽的像素点数量和CP信号的频率。

DRin1~8和DGin1~8为红、绿数据输入信号,分别对应第1个16行点阵区到第8个16行点阵区。Cpin为同步脉冲,一个脉冲对应一位数据,8个脉冲对应一个像素点的8位数据输入。H信号为行同步脉冲,一行数据输入结束,H信号有效一次。V为帧同步脉冲,一帧(16行)数据输入结束,V信号有效一次。上述信号均为前级系统提供的信号。

FPGA外部接有两组高速静态RAM(图中未画出),DRA1~8、DGA1~8为A组RAM的红、绿数据线,DRB1~8、DGB1~8为B组RAM的红、绿数据线;/WRA、/RDA为A组的读、写控制信号,/WRB、/RDB为B组的读、写控制信号;AA0~16为A组的地址线,AB0~16为B组的地址线。使用两组RAM的目的是保证对RAM的读写操作能同时进行。当写RAM(A)时,读RAM(B);当写RAM(B)时,读RAM(A)。二者的写/读切换由帧信号V控制。V每有效一次,就进行一次切换。

Cpin为前级系统提供的写脉冲,同时亦作为写地址生成电路的计数脉冲,计数地址范围为A0~A16, 共128K字节, 其中A0~A2为灰度位数据地址(决定访问8位的哪一位)。A3~A12为X方向的像素地址,A13~A16为Y方向的像素地址,即行地址。H信号到来时,清零A0~A12,同时A13~A16地址加1。V信号到来时,A0~A12及A13~A16全部清零。上述地址作为RAM的写地址。

CLK为读地址生成电路计数脉冲(外电路提供),计数地址范围亦为A0~A16, 共128K字节, 其中A0~A9为X方向的像素地址,A10~A13为Y方向的像素地址,即行地址。A14~A16为灰度位数据地址。上述地址 作为RAM的读地址,这些地址的变化规律应符合“19场原理”对地址要求的变化规律,即:A0~A9计满后清零,产生一个行信号即LE信号。LE信号作为A10~A13的计数脉冲,A10~A13计满后清零,产生一个场信号。场信号作为A14~A16的计数脉冲。不过,A14~A16并不是一简单的二进制计数,其规律如表5所示。为了能正确地读取写到RAM中的数据,生成的读地址应按表6所示的方法与RAM连接。

读写控制电路的作用是向两组RAM提供读写控制信号,逻辑关系如表7所示。数据输入/输出电路的作用是切换数据的传输方向,如表8所示。

帧切换电路的作用是产生上述电路所需要的切换信号S。实现的方法是,帧同步脉冲V每有效一次,S的逻辑状态翻转一次。帧切换电路保证了两组RAM随V信号不断进行读写转换。

灰度信号生成电路产生被控对象需要的EA信号,它随读地址A14、A15、A16的状态而变化。逻辑关系如表9所示。

依据帧周期Tp=20ms,一帧=19场原理,可得如下计算结果: 场周期Tv=Tp/19=1.05ms; 行周期T=Tv/16=66ms; 输出移位脉冲周期Tcp=T/1024=64ns;输出移位脉冲频率fcp=1/Tcp=15.6MHz。CLK信号频率fclk=fcp=15.6MHz; 实际应用时,选取CLK时钟信号频率为16MHz。

在MAX PLUSII10.0环境下,使用图形和硬件描述语言完成了以上电路的设计。

FPGA选型及仿真结果

由图1可知,FPGA必须提供113个I/O引脚,内部资源、工作频率须满足电路设计要求。采用Altera公司的ACEX1K系列EP1K10QC208-3芯片,该FPGA芯片速度高、价位低、有114个I/O引脚,576个逻辑宏单元,可兼容输入输出电路的TTL电平。仿真结果报告: 引脚利用率达99%,内部逻辑单元利用率达到85 %,达到了充分利用资源、提高性价比的目的。

-

FPGA

+关注

关注

1629文章

21729浏览量

602986 -

led

+关注

关注

242文章

23252浏览量

660565 -

控制系统

+关注

关注

41文章

6604浏览量

110576

发布评论请先 登录

相关推荐

基于FPGA EP1K10QC208-3芯片实现256级灰度LED点阵屏控制系统的设计

基于FPGA EP1K10QC208-3芯片实现256级灰度LED点阵屏控制系统的设计

评论