对于相位调制信号,相干解调为平均误码率最小的信号接收方式。相干解调需要在本地产生与接收载波信号同频同相的载波副本,锁相环是相干解调系统中获取本地载波副本时常用的方法。对于锁相环,噪声水平和跟踪速度是两个非常重要的性能参数,二者均取决于环路带宽但是不能同时达到最优。传统锁相环往往根据估算预先确定一个带宽值,因而当噪声环境发生变化时,该值可能不是最优值,甚至不适

合当前环境。在传统锁相环的基础上引入了自适应调整模块,根据当前环境自适应调整带宽值,确保无论锁相环处于固定或变化的噪声环境中均能工作在比较合适的带宽下,获取较好的跟踪效果。

1 同相正交环结构

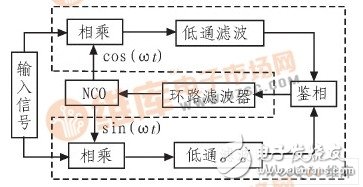

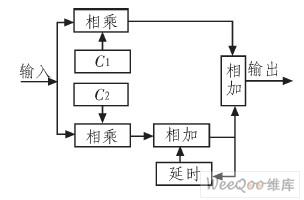

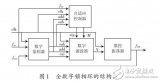

平方环和同相正交环都是解调系统中常用的跟踪环路,平方环的工作频率较高,对器件的性能要求较高,且平方环可能存在“理想平方器”的问题。如果同相正交环中的环路滤波器与平方环中的环路滤波器相同,则二者是等效的,同相正交环的环路中信号频率较低,对器件的性能要求较低,因此设计中选用同相正交环。同相正交环主要由误差提取模块、数控振荡器(NCO)和环路滤波器组成,如图l所示。图中虚线框为误差提取模块,用来鉴别本地振荡信号与接收信号的载波分量之间的相位差。环路根据提取出的相位差信号,不断调整本地NCO,最终使本地NCO和输入信号的载波分量同频同相,并在此基础上对接收信号进行有效地相干解调。

图1 锁相环基本结构图

2 NCO实现及性能分析

NCO常用在直接数字合成器(DDS)中作为其数字实现部分。由此方法设计的DDS具有转换时间短、分辨率高、低相噪和输出相位连续等特点。在锁相环中,NCO用于产生本地振荡信号,由NCO同时产生本地的正弦及余弦信号。该模块由频率控制加法器、频率控制累加寄存器和波形存储器组成。输入的频率控制字在时钟信号的驱动下进行累加,利用累加结果作为地址在波形存储器中读取预先存储的正弦波数据。模拟锁相环中,由模拟压控振荡器产生的本地正弦信号和余弦信号往往不能严格正交,利用数字方法实现的NCO时可以较好地解决这一问题,只需正确设置正弦信号和余弦信号对应的初始地址即可。频率控制字f_con与输出f_out的关系为,其中fs表示采样频率,系统中为80MHz,2N为波形存储器的容量,N对应着该存储器的输入地址线的位数。

对于NCO,其性能主要体现在最小相位误差和最小频率分辨率上。波形存储器中通常存储一个周期的正弦波,因而最小相位误差为:通过该式可以看出,N值取得越大,最小相位误差越小。然而N越大,对应的存储器容量越大,必然占用更多的逻辑资源,因而不能无限制地增加N值。设计中N取12,对应最小相位误差为0.0015 rad。NCO的最小频率分辨率为,其大小取决于频率控制字的位数,为了有效增加频率分辨率,取NCO的频率控制字位数M稍大于N,设计中取M为16。

3 鉴相方法及性能分析

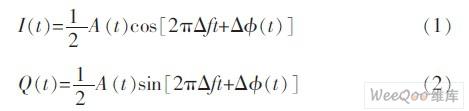

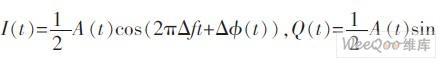

如图l所示,鉴相模块是锁相环的核心模块之一,其精度和鉴别范围直接影响锁相环的性能。系统接收信号为双相移相键控(BPSK)信号,设输入信号为s(t)=A(t)cos(2πfct+φc(t)),本地载波信号为cos(2πf0t+φ0)及sin(2πf0t+φ0)。将输入的BPSK调制信号与NCO产生的2路本地载波信号分别进行相乘处理,对产生的乘积信号分别进行低通滤波,去除高频信号。为保持信号的线性相位及系统的稳定性,可采用有限冲激响应(FIR)滤波器完成低通滤波处理。通过低通滤波处理去除高频分量后,得到

式中,Q(t)、I(t)分别为锁相环环路的同相信号和正交相信号,其中

鉴相处理即是对上述信号进行相应处理以得到对应的相差信号。常用的鉴相方法有正弦鉴相法,2倍角正弦鉴相法,正切鉴相法和反正切鉴相法。其数学表达式分别对应为:sign(I(t))·Q(t),I(t)·Q(t),Q(t)/I(t)和arctan[Q(t)/I(t)]。鉴相法的线性度越好、鉴相范围越广,则相应的锁相环可跟踪的频率范围越大。利用仿真软件MATLAB对上述4种鉴相法对应的锁相环进行仿真。仿真参数对应实际系统中设置的参数,即采样速率为80 MHz,接收信号中载波分量的频率为lO MHz。多次实验结果显示:随着起始频差的不断增加,2倍角正弦鉴相法对应的锁相环最先出现跟踪不上的情况,随后是正弦鉴相法对应的锁相环,最后是正切鉴相法和反正切鉴相法对应的锁相环。

用FPGA实现上述4种鉴相器时,正弦鉴相法使用少量的逻辑语句即可实现,占用的逻辑资源较少;2倍角鉴相法需要使用一个乘法器模块,在逻辑资源的占用上比正弦鉴相法稍多一些;正切鉴相法可选用查表法或者坐标旋转数字计算机CORDIC方法,占用的逻辑资源较多;反正切鉴相法可使用CORDIC方法实现,占用的逻辑资源也比较多。设计中可根据系统的资源情况和性能要求在上述4种鉴相方法中进行选择。本文中设计的模块应用在基于FPGA的直序扩频接收机中,对资源占用具有比较严格的限制,考虑到正弦鉴相法已经能够满足当前系统的性能要求,因此选用正弦鉴相法。

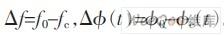

4 自适应锁相环

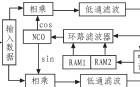

噪声水平和跟踪性能是锁相环的两个重要性能参数,但是二者是相互对立的,锁相环处于噪声环境中时,环路带宽越大,跟踪速度越快,同时引入的噪声越多;环路带宽越小,引入的噪声越少,同时跟踪速度越慢。通过对锁相环的传递函数进行分析得出,锁相环的环路带宽取决于锁相环中环路滤波器的带宽,对环路滤波器的带宽进行调整即是对锁相环的带宽进行调整。实际应用中,锁相环处于噪声水平较低的环境中时,其参数跟踪速度更为重要,此时应尽可能增加环路带宽,相反,噪声水平较高时,获取较小的相位抖动更重要,此时应尽可能减小环路带宽,抑制噪声信号。设计中按照这一思路,引入噪声*估模块,根据当前环境中噪声的大小对环路滤波器的带宽进行自适应调整。自适应锁相环结构如图2所示,自适应锁相环在传统锁相环的基础上引入了噪声*估模块和系数调整模块。

图2 自适应锁相环结构

4.1 环路滤波器

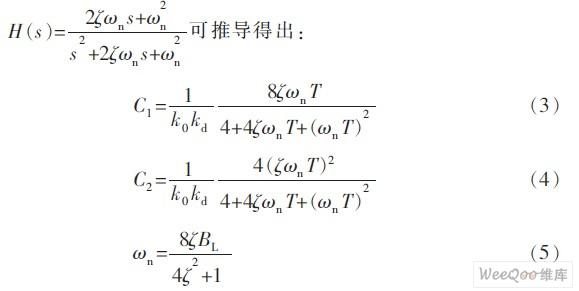

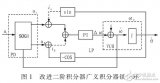

锁相环中的环路滤波器是一个线性低通滤波器,它主要有2个功能:1)滤除误差信号中的高频分量;2)为锁相环路提供一个短期的记忆,对环路的校正速度起到调节作用。模拟锁相环中的环路滤波器由电阻、电容和运算放大器等线性元件组成,如RC积分滤波器、无源比例积分滤波器、有源比例积分滤波器等等,数字环路中的环路滤波器可利用双线性变换和它们一一对应。设计中以有源比例积分滤波器为原型,通过双线性变换得到。锁相环的阶数比环路滤波器的阶数大1。环路滤波器的阶数越高,对应锁相环的跟踪性能越强大,二阶环路滤波器对应的三阶锁相环具有跟踪加速度频率输入的特性,对于本系统,二阶锁相环已经满足要求,因此采用一阶环路滤波器,与之对应的环路滤波器的数字化结构如图3所示。

图3 一阶环路滤波器

图3中C1、C2为环路滤波器的系数,将此滤波器的传递函数引入锁相环,得出锁相环的传递函数,对照标准形式

式中,ωn、T分别对应锁相环的自然角频率和环路调整时间间隔,可根据系统要求进行取值,设计中取T为采样时间间隔,即每个点调整一次,ζ取常用值 0.707,ko、kd分别对应鉴相增益和相位控制灵敏度,BL表示环路噪声等效带宽。由式(3)~式(5)可知,噪声等效噪声带宽BL和环路滤波器系数 C1、C2一一对应,因此改变噪声带宽即可通过调整系数C1、C2实现。传统锁相环中,取固定值,一般选取满足条件BL≤ O.1Rb的值,其中Rb为信息数据速率。

4.2 系数调整

相干解调系统中,同步系统的相位误差直接影响着系统的误码性能,其对应关系为:其中ψ为相位误差。因此噪声水平较高时,应该尽可能减小噪声带宽,近而减小ψ值,噪声水平较低时,适当增加噪声带宽,加快跟踪速度。

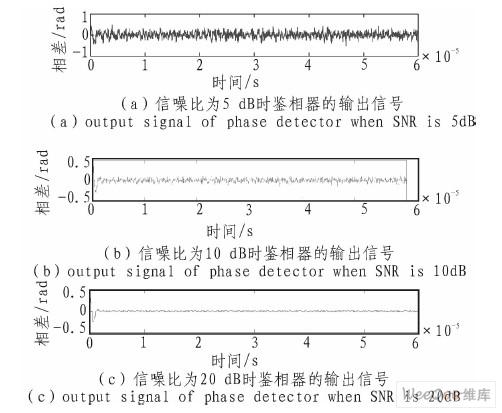

利用仿真软件MATLAB对3种噪声水平下的输入信号进行相位跟踪仿真,3种情况下,锁相环参数相同,输入的调制信号相同,不同的是对信号叠加3种功率不同的噪声。结果显示,锁相环中引入的噪声越大,则鉴相器模块输出信号的抖动越大。输入信号的信噪比为5、10和20 dB时,鉴相器模块的输出信号如图4所示。

图4 不同信噪音比下鉴相器和输出信号

由图4可以看出,噪声水平越高,则鉴相器的输出信号抖动越厉害,于是设计中利用鉴相器输出信号的抖动状况来判断锁相环中的噪声水平,并根据噪声水平来调整 C1、C2值。MATLAB仿真结果显示,鉴相器的输出值是在0值上下浮动,因此利用FPGA实现此功能时,可利用鉴相器输出值的绝对值或平方值判断噪声大小,浮动越大则噪声水平越高。利用单个点的抖动来判断时,具有一定的偶然性,结果不准确,容易产生误判,因此,在FPGA硬件板上利用VHDL编程实现时,对鉴相器的输出数据取绝对值或进行平方处理,并对连续15个点的绝对值或平方值进行累加运算,利用累加的结果来判断相位抖动的大小。对15个点取和时,利用树形加法结构,引入流水线设计方法,使各个加法器并行工作,确保输出结果的速率和输入数据的速率相等。计算过程中使用绝对值代替平方值,能获取与平方值相似的结果,有效降低运算量。进行带宽调整时,可以利用当前应该设置的BL值计算出与之对应的环路滤波器系数C1、C2由式(3)~式(5)可以看出,通过BL计算C1、C2时比较复杂,涉及多次除法运算、乘法运算以及加法运算,在FPGA中,实现除法器、乘法器都是比较占用逻辑资源的,因此设计中不采用直接计算的方法,而是利用查找表法来实现,首先订制2个容量为256的ROM,将可取的带宽值平均划分为256等分,对每个带宽值对应的C1、C2 值预先进行计算,计算结果经量化处理后,以MIF文件的形式分别加载到ROM1、ROM2。ROM1、ROM2的地址线均为8位设计中连接到同一信号,对应地址范围为0x00到OxFF,由图2中的噪声*估模块产生。噪声*估模块输出的初始值设置为0x7F,即初始带宽值设置为可取范围段的中间值,之后根据噪声*估模块的结果,与提前设定的上限值、下限值进行比较,并根据比较结果调整带宽值,其中上限值、下限值通过仿真得出,这两个域值与FPGA实现时采用的位宽、位截短处理、滤波处理等有关。为防止过于频繁地进行调整,程序中设定,如果连续3次的抖动高于上限值且当前地址值大于Ox00,则减小带宽值 (即地址减1),相反,若连续3次的抖动低于下限值且当前地址值小于0xFF,则增加带宽值(即地址加1)。

锁相环启动工作时,不论噪声水平高低,鉴相器输出信号的抖动都比较大,连续3次抖动高于上限值是比较正常的,这时若将带宽值减小,会降低跟踪速度。因此设计中限定,只有本振信号的相位和接收载波信号的相位大致相符后,才允许减小带宽值。因此环路设计中需要判断相位是否大致相符。

参看结构图l,经低通滤波后的同相和正交支路的信号分别为:

相位大致相符时,取值较小,I(t)2应大于Q(t)2。设计中利用条件判断是否已满足相位大致相符的条件。二者之差的下限值c同样与系统中的输入数据位数、滤波器等模块有关系,可在Modelsim或Quartus下通过测试获得。为了增加判断的准确性,设计中同样做出限定,连续3次满足条件时,才判定相位已大致相符。

5 实验结果及分析

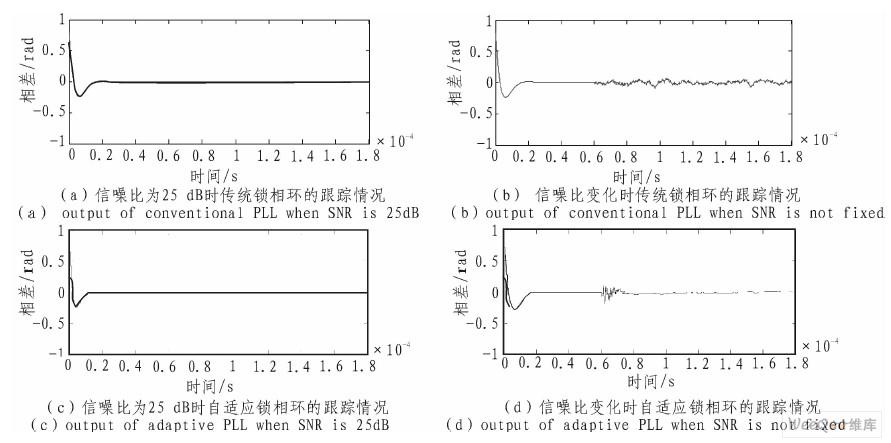

设置中频载波信号为10 MHz,采样频率为80 MHz,本地初始中心频率为9.9 MHz。在信噪比固定为25 dB和信噪比变化的情况下,分别利用传统的锁相环和图2所示的自适应锁相环进行相位跟踪,得到的相差结果如图5所示。

图5 传统的锁相环和自适应锁相环的跟踪情况对比

通过仿真结果(图5)可以看出,与传统锁相环相比,自适应锁相环能够根据当前环境自适应对环路带宽作出调整,对环境的适应性更强。噪声水平较低时,跟踪速度是关键性能参数。在噪声水平较低的情况下(对应25 dB),自适应跟踪具有更快的跟踪速度。噪声水平较高时,相位抖动是关键参数,结果显示,在噪声水平较高的情况下,自适应锁相环具有较小的抖动。

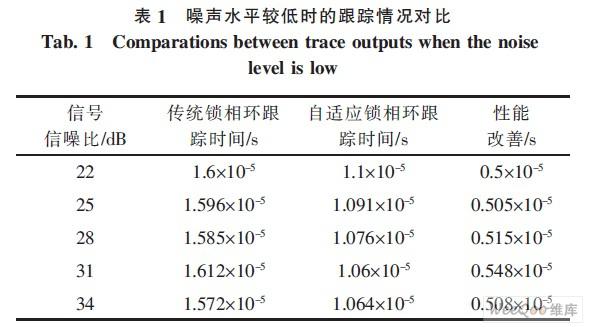

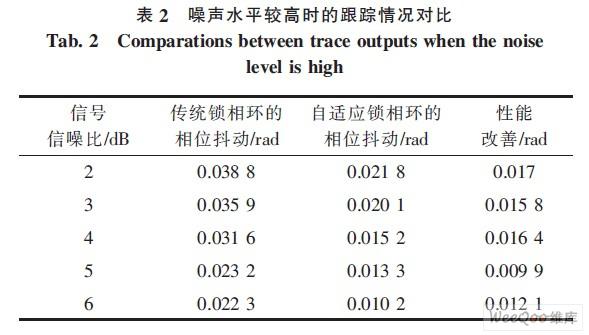

在此基础上,在多种信噪比环境下进行实验。信噪比较大即噪声水平较低时,传统锁相环的自适应跟踪的跟踪速度结果如表1所示。信噪比较小即噪声水平较高时,传统锁相环的自适应跟踪的跟踪速度结果如表2所示。

上述结果显示,与传统锁相环相比,自适应锁相环在噪声水平较高时,具有更快的跟踪速度,在噪声水平较低时,最有更小的相位抖动,起到了根据环境作出自适应调整的作用。

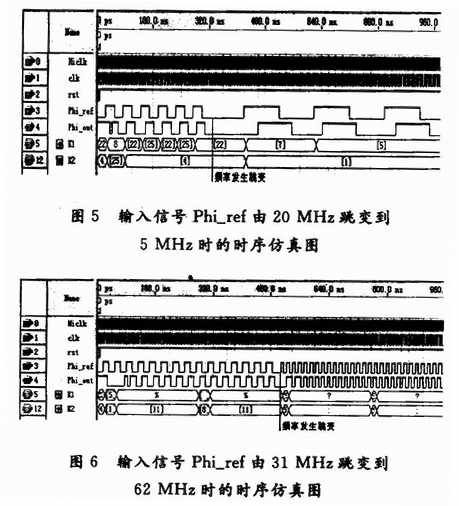

系统设计中使用的FPGA是EP3CIOF256C8。将调试好的程序下载到FPGA硬件板,通过QUARTUSⅡ软件中自带的SIGNALTAP工具对输入和输出信号进行实时观察,结果显示,设计的自适应锁相环能够进行正确稳定的跟踪,正确解调出数据信号。该模块目前已应用在基于数字中频方案的扩频接收机中。

6 结论

在传统锁相环的基础上,引入自适应参数调整模块,能够根据锁相环所处环境的噪声情况,自适应地对环路带宽进行调整,由于调整过程中步长取值较小,具有一定的连续性,因此,调整过程中仍能正常进行数据解调,不会引起突变,能够有效地在噪声性能和跟踪速度间进行平衡。

-

FPGA

+关注

关注

1629文章

21729浏览量

602986 -

存储器

+关注

关注

38文章

7484浏览量

163762 -

加法器

+关注

关注

6文章

183浏览量

30114

发布评论请先 登录

相关推荐

基于DSP Builder系统模型的数字锁相环设计

一种新型带宽自适应全数字锁相环的设计方案

快速建立时间的自适应锁相环

基于FPGA的自适应锁相环设计

锁相环的研究和频率合成

自适应锁相环的分次谐波检测优化算法

采用EP3CIOF256C8实现自适应锁相环设计

采用EP3CIOF256C8实现自适应锁相环设计

评论