简介

ADG9xx CMOS宽带开关主要设计用来满足工业、科研和医用(ISM)频段 (≥900 MHz) 信号发射器件的要求。这些器件具有低插入损耗、高端口间隔离度、低失真和低功耗等特性,因而是要求低功耗且能够处理发射功率 (最高达16 dBm) 的许多高频应用的理想解决方案。典型应用包括高速滤波和数据路由。

关于各器件 (ADG901,ADG902,ADG904,ADG904R,ADG918,ADG919,ADG936和ADG936R) 的完整特性,可以在数据手册中找到,同时请参考本应用笔记。本应用笔记对有关这些器件的一些常见问题进行了释疑。ADG9xx器件的完整列表见表1。

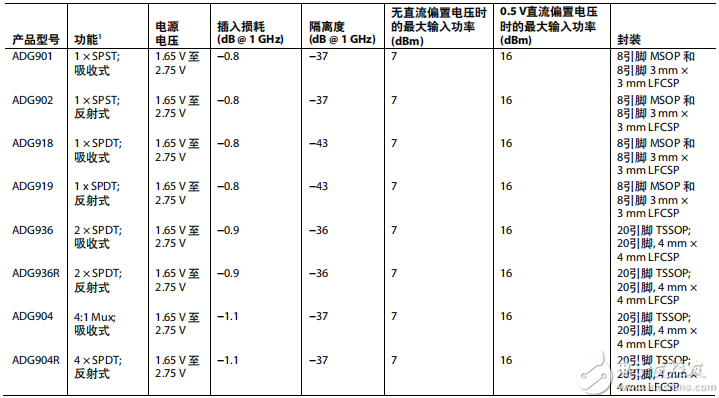

表1.ADG 9xx系列的主要规格特性

吸收式(匹配):具有对地50Ω端接电阻的开关;反射式:具有对地0Ω端接电阻的开关。

常见问题

电源电压

ADG9xx产品的电源电压范围是多少?

AD G9xx是采用CMOS工艺制造的宽带开关,在最高至1 GHz范围内提供高隔离度和低插入损耗特性。这些器件采用1.65 V至2.75 V供电,且在该电压范围具有完整特性。VDD电源应对地完全去祸。ADG9XX评估板的VDD线路上,使用了2个10μF表贴封装去祸担电容,其中一个靠近DUT放置,另外还将一个100 pF陶瓷电容。

为发挥最佳性能,这些器件应当采用何种电源电压供电?

一般而言,VDD上的电源电压越高,则性能越佳。从各数据手册的特性图可以看出,电源电压越高,插入损耗性能也越强。另外,电源电压越高,IP3和P1dB也略有改善。但无论VDD是1.65 V还是2.75 V ,隔离度性能的变化则不明显。泄漏性能和IDD性能在VDD较低时略有改善。

数据手册的“绝对最大额定值”部分显示VDD对GND为-0.5 V至+4 V,那么这些器件能采用3VVDD电源供电吗?

这是绝对最大额定值条件,长时间在绝对最大额定值条件下工作会影响器件的可靠性。在使用寿命期间,AD G9xx系列的保证工作电压范围为1.65 V至2.75 V,而且其完整特性是针对该电源电压范围而提供的。

因此,这些器件可以采用2.75 V以上电源供电,但使用寿命无法得到保证。如上所述,电源电压越高,器件的性能越佳,但泄漏和IDD这两种主要特性则会略微变差。

直流性能

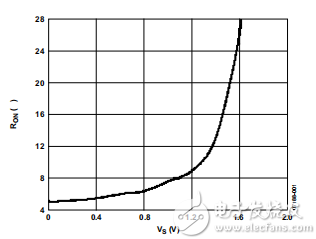

信号损耗本质上是由导通条件下的开关电阻RON所引入的衰减决定;与源加负载电阻串联的开关电阻RON,是在较低的工作频率时测得的。

ADG9xx系列采用N-沟道MOSFET结构,这种结构与标准开关的NMOS和PMOS FET并联结构相比,具有显著的带宽优势。带宽改善的原因在于开关尺寸更小,以及不使用P-沟道MOSFET可以大幅减小寄生电容。ADG9xx的导通电阻变化图与N-沟道MOSFET结构的预期导通电阻曲线一致。图1显示了在这些器件上测得的典型导通电阻RON与输入信号关系图。

高关断隔离度是如何实现的?

对宽带应用的开关设计人员而言,当信号频率提高至数百MHz以上时,寄生电容往往会占据主导地位,因此要实现开关关断状态下的高隔离度和导通状态下的低插入损耗并非易事。

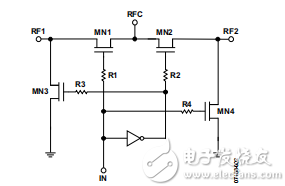

ADG 9xx系列跳脱了常见开关拓扑结构的案臼,为关断(及其相关的杂散信号)添加了对地分流路径,使得开关在高频时具有更高的关断隔离度。图2显示,FET具有联锁指形布局,减小了输入(RFx)与输出(RFC)之间的寄生电容,从而提高了高频时的隔离度并增强了串扰抑制能力。例如,当MN1导通形成RF1的传导路径时,MN2关断且MN4导通,从而消除了RF2上的寄生电容。

为什么关断隔离性能在较低频率时(< 1 MHz)会下降?

在较低频率时,有两种机制会产生重要影响:一种是寄生二极管可能呈正偏,另一种是分流NMOS器件在应当关断时可能发生部分导通现象。

这会影响频率接近DC时的关断隔离性能。这些机制将在“功率处理”部分的第二个问题中予以详细说明,因为它们对低频时的功率处理能力也有影响。

功率处理

什么是dBm?

dBm是指功率相对于50Ω负载上1mW功率的dB数。因此对于正弦波信号,0 dBm功率水平为: 224 mV均方根值 = 316 mV峰值 = 633 mV峰峰值。对于其它功率水平,dBm计算公式为:

dBm=10 x log(P/1 mW)=10 x log[(V rms2)/(R x 1 mW)]

其中:

Log为以10为底的对数。

R为50Ω.

那么什么是7 dBm (5 mW)输入信号呢?对于50Ω负载,7 dBm信号对应于0.5 V均方根信号,或1.4 V峰峰值(正弦波)。类似地,16 dBm对应于1.4 V均方根或4V峰峰值。

【VP-P=Vrmsx2x√2】

这些器件如何能在无直流偏置电压的情况下处理7 d8m输入功率、在0.5 V直流偏置电压的情况下处理16 d8m输入功率(如数据手册所示)?

对于7 dBm以上的输入信号,应用0.5 V直流偏置电压可以提高正弦波的最低电平,防止信号负的部分被削波或衰减。较小直流偏置电压可以抵消较低频率时(<100 MHz)导致功率处理能力降低的两种效应。

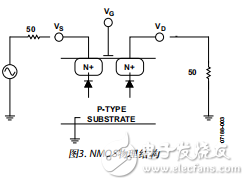

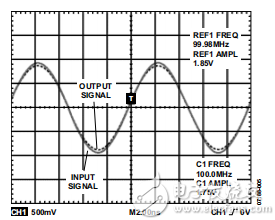

NMOS的内部结构如图3所示,由位于P型基板中的两个N型材料区组成。因此,N区与P区之间形成寄生二极管。当偏置OVDC的交流信号作用于晶体管的源极,并且Vcs大到足以接通晶体管((Vcs>Vr)时,对于输入波形的负半周的某一部分,寄生二极管可能呈正偏。如果输入正弦波形低于约一0.6 V,便会发生上述情况,并且二极管开始接通,导致输入信号被削波(压缩),如图4所示。该图显示了一个100 MHz, 10 dBm输入信号及相应的100 MHz输出信号。请注意,输出信号已被削去顶端了。

在低频时,输入信号长时间低于-0.6 V电平,这对1 dB压缩点(P1dB)有较大影响。这就解释了导致较低频率时功率处理能力降低的第一种机制。

在较低频率时,如果分流NMOS器件在应当关断时却部分接通,则器件能处理的功率也会较低。这与上文所述寄生二极管部分接通的机制相似。这种情况下,当Vcs

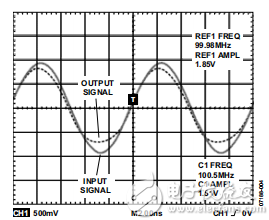

在输入信号大于7 dBm (或5 mW , 50 Ω电阻上存在1.4 V峰峰值) 的情况下使用开关时,对RF输入信号施加一个较小直流偏置电压(约0.5 V)便可克服上述两种机制的影响。其原理是通过提高正弦波输入信号的最低电平,确保寄生二极管持续呈反偏,并且在输入信号的整个周期内,分流晶体管的Vcs永远不会大于Vr,因而保持关断状态。图5显示了0.5V直流偏置电压时100 MHz, 10 dBm输入功率(50 Ω电阻上存在约2V峰峰值)的输入与输出信号图。图中清楚显示出在100 MHz时不再发生削波或压缩。

如何对RF输入施加直流偏置电压?

为将通过输入端上的端接电阻泄漏的电流降至最低,最好将偏置电压施加在输出(RFC)端上。这是最佳做法,尤其是针对低功耗便携式应用,但如果下游电路不能处理这种直流偏置电压,则可能需要在RF输出端上应用隔直电容。

可以使用高于0.5V的直流偏置电压吗?

图1显示导通电阻随着输入信号增大而呈指数式增大。它还显示高于0.5 V的直流信号会增加开关上的损耗,而且用户希望导通电阻尽可能小。与标准CMOS开关一样,作用于开关输入的信号绝不能超过VDD电源电压。

-

CMOS

+关注

关注

58文章

5790浏览量

236603 -

NMOS

+关注

关注

3文章

301浏览量

34796 -

ADG663

+关注

关注

0文章

4浏览量

6983

发布评论请先 登录

相关推荐

为什么关断隔离性能在较低频率时会下降?

为什么关断隔离性能在较低频率时会下降?

评论