1. 什么是SSI芯片?

SSI是Stacked Silicon Interconnect的缩写。SSI芯片其实就是我们通常所说的多die芯片。其基本结构如下图所示。可以看到SSI芯片的基本单元是SLR(Super Logic Region),也就是我们所说的die。SLR之间通过Interposer“粘合”在一起。每个SLR可看做一片小规模FPGA。

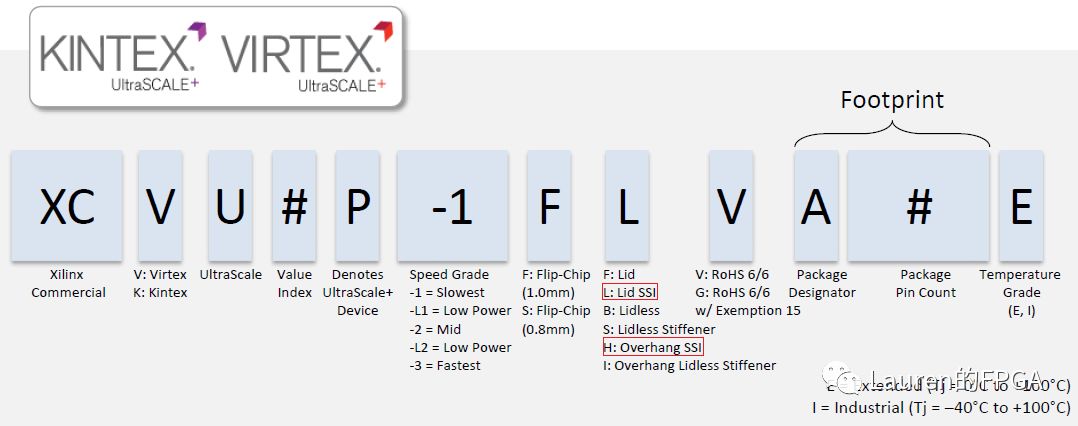

2. 如何从芯片型号上判断FPGA是否是多die芯片?

在芯片选型手册上,有如下图所示说明,根据图中红色方框标记可判断该芯片是否是SSI芯片。

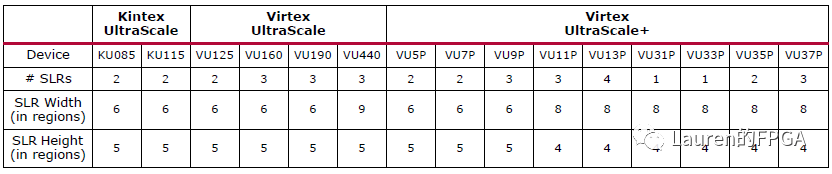

3. UltraScale和UltraScale+系列有哪些芯片是SSI芯片?

总的来说,UltraScale+大部分都是多die芯片,如下图所示。图中还可以看到每个芯片所包含的SLR的个数以及每个SLR的大小。SLR的大小以时钟区域(Clock Region)衡量,例如,VU5P有两个SLR,每个SLR的宽度为6,高度为5,所以共有6x5也就是30个Clock Region。同时,还可以看到每个SLR的大小是一致的。

图片来源:Table 19,ds890

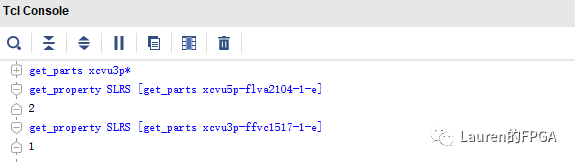

4. 在Vivado下如何判断芯片是多die芯片?

只要获知芯片的具体型号,在Vivado Tcl Console中执行如下图所示命令即可获得该芯片所包含的SLR的个数。例如,对于XCVU5P,属性SLRS的返回值为2,说明该芯片有两个SLR,故其是多die芯片;而对于XCVU3P,返回值为1,说明该芯片只有一个SLR,故其是单die芯片。

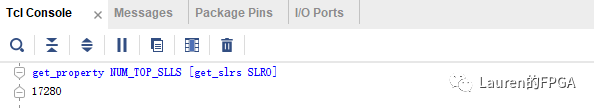

5. 多die芯片的每个SLR地位一样吗?

多die芯片的每个SLR其结构基本是一致的,都包含CLB、Block RAM、DSP和GT等。但这些SLR的地位是不一样的。这其中只有一个SLR是Master SLR。通过如下图所示的命令可获取Master SLR(需要在打开的工程中或DCP中执行该命令)。通常SLR0为Master SLR。用于配置FPGA的电路、DNA_PORT和EFUSE_USER只存在于Master SLR中。

6. SLR之间是如何互连的?

这是多die芯片设计中的一个重要问题。SLR之间通过专用布线资源SLL(Super Long Line)互连。SLL的个数是有限的。以XCVU5P为例,可通过如下命令获取SLL的个数。这在设计初期是非常重要的。需要根据此数值评估跨die网线个数是否合理。跨die网线过多很可能造成布线拥塞,进而影响时序收敛。

7. 跨die时钟需要特殊处理吗?

对于SSI器件,Interposer上分布了专用的全局时钟走线,因此,对于跨die时钟并不需要特殊处理,同时该时钟也不会占用SLL。

8. Block RAM和DSP48能否跨die级联?

以DSP48为例,其有专门的级联端口,例如PCOUT/PCIN。因此,相邻的两个DSP48级联时,会使用专用的级联布线资源。但是,这种布线资源仅限于die内。类似地,Block RAM、Carry Chain等在die内可使用固有的级联布线资源。

9. 对于多die芯片,如何评估资源利用率?

器件选型阶段需要根据设计规模选择合适的芯片。这个阶段,需要根据整个设计的资源利用率确定芯片规模。一旦选定SSI器件,就要及早考虑模块划分,也就是如何将设计分配到每个die内,使每个die的资源利用率尽可能平衡,此时就要考虑每个die的资源利用率,避免出现某个die某一资源利用率过高以至于出现拥塞,而另一个die该资源利用率偏低的情形。这一工作要在设计初期完成,本质上就是要设计好合理的数据流,从而达到两个目的:每个die的资源利用率比较均衡;跨die网线个数合理。

-

FPGA

+关注

关注

1631文章

21806浏览量

606681 -

芯片

+关注

关注

457文章

51345浏览量

428237 -

SSI

+关注

关注

0文章

38浏览量

19331

原文标题:9个关于SSI芯片的必知问题

文章出处:【微信号:Lauren_FPGA,微信公众号:FPGA技术驿站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

利用Multi-Die设计的AI数据中心芯片对40G UCIe IP的需求

一文解析多芯片封装技术

边缘芯片详解

DDR4的单、双DIE兼容,不做仿真行不行?

新思科技面向英特尔代工推出可量产的多裸晶芯片设计参考流程,加速芯片创新

用玻璃,造芯片!

为什么要进行芯片测试?芯片测试在什么环节进行?

在Vivado下如何判断芯片是多die芯片

在Vivado下如何判断芯片是多die芯片

评论