简介

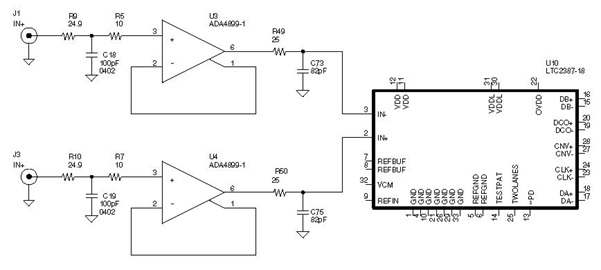

LTC2387-18是一款低噪声,高速,18位15Msps逐次逼近型寄存器(SAR)ADC。良好的线性度和宽动态范围的结合使LTC2387-18成为高速成像和仪器仪表应用的理想选择。无延迟操作为高速控制环路应用提供了独特的解决方案。高输入频率下的低失真使通信应用成为需要宽动态范围和显着信号带宽的应用。 LTC2387-18支持高速运行,同时最大限度地减少数据线数量,具有串行LVDS数字接口,可轻松连接到FPGA。 LVDS接口具有单通道和双通道输出模式,允许用户优化每个应用的接口数据速率。

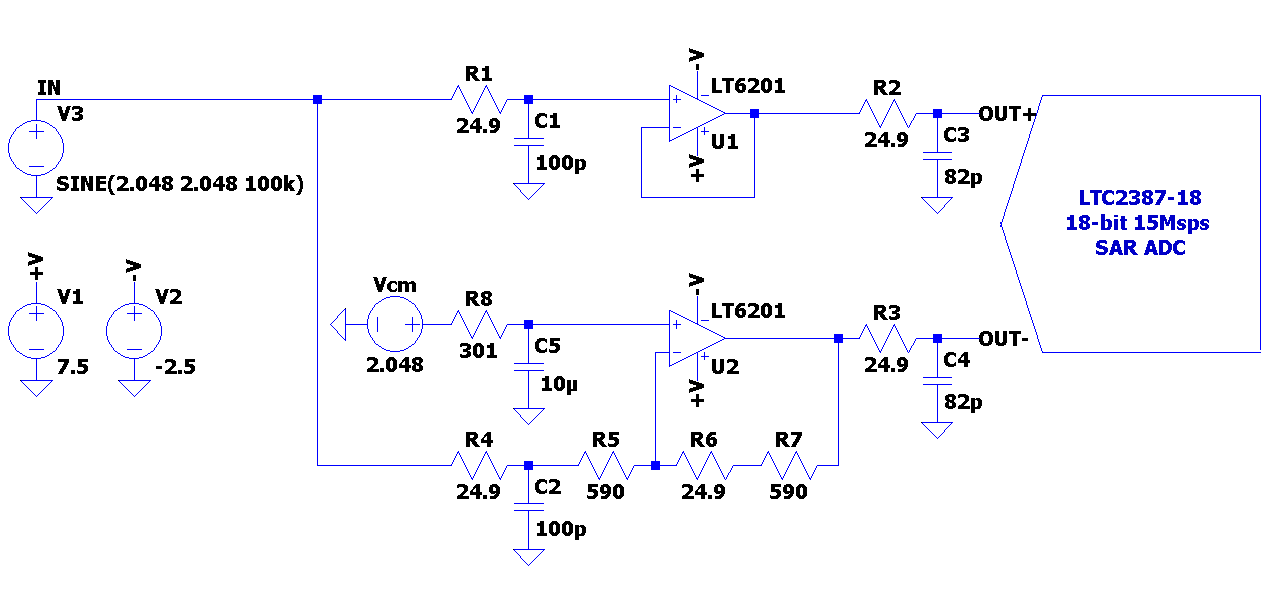

DC2290A-A是LTC2387-18的演示电路。该电路板的采样率(Fs)为15Msps,数字化数据以串行方式退出ADC。以下是LTC2387-18,但适用于LTC2387系列的所有成员(LTC2386和LTC2385)以及DC2290A演示电路的其他变化,唯一的区别是采样率和位数。

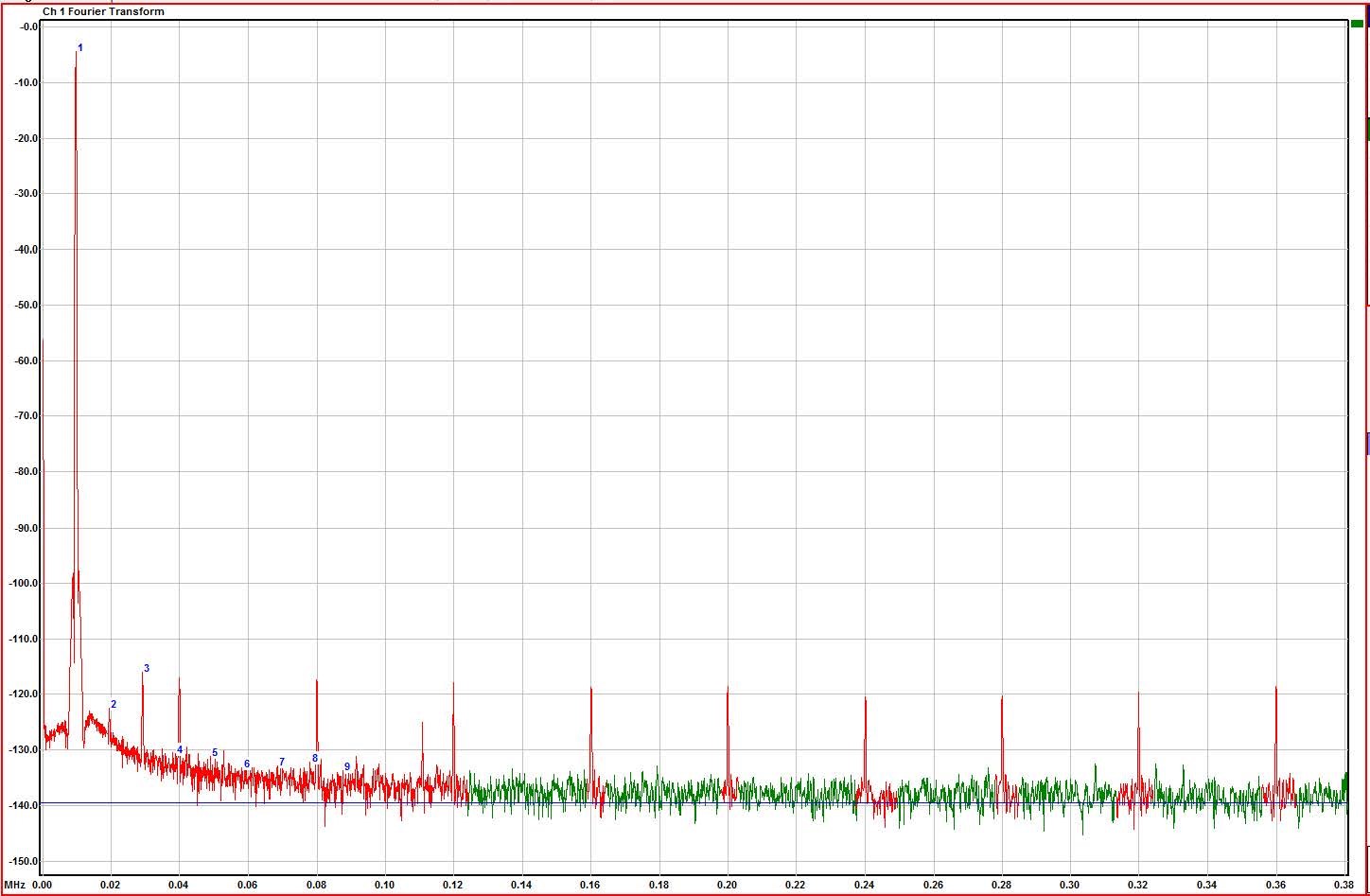

DC2290A演示电路包括一个Altera Cyclone III FPGA,它采用Verilog编程,用于对ADC输出数据流进行反串行化,并将其传送到DC890B USB数据采集卡的18位并行总线上。 DC890B对这些数据进行调节,以便将其传递到PC并显示在PSCOPE中。 PScope软件在时域和频域中收集和分析来自ADC的数据,并显示被评估设备的相关参数。 PSCOPE的最大FFT大小为131K,在这种情况下,每个箱的光谱分辨率约为114Hz。下面是在这些条件下9.76KHz音调的典型65K点FFT的一部分,每箱的噪声为-139.4dBFS。

通过下采样提高频率分辨率&低通滤波器

如果我们想要更高的频率分辨率或想要观察非常接近零频率的噪声水平和信号怎么办?降低采样率是一种选择。这应该具有缩小箱尺寸并因此降低每箱的噪音水平的效果。这种方法的问题是混叠。别名是采样过程的正常结果。这意味着模拟输入光谱被切成Fs / 2宽的块,它们彼此重叠以构成最终输出光谱。通常,选择采样率使得模拟输入信号内容的大部分低于Fs / 2。通过对模拟输入信号和噪声进行低通滤波,信号内容限于该频谱区域。这就是简单地降低采样率的问题 - 这意味着用户必须降低模拟输入信号或ADC之前的低通滤波器的带宽。这些措施都不实用。

更好的选择是单独保留采样率并对ADC的数字化输出进行下采样。注意,为了避免信号和噪声的混叠(如上所述),我们必须在下采样之前对输出进行低通滤波。这是使用数字滤波器而不是模拟滤波器完成的。因为这可以在FPGA中完成,所以很容易实现和修改。例如,如果我们有一个通过15Msps采样获得的频谱,我们可能希望将频率分辨率提高128倍。为了有效地做到这一点,输出样本必须限制在介于0Hz和7.5之间的频谱。 / 128MHz,或58.593KHz。然后可以将样本下采样128倍,很少或没有混叠。分辨率将增加128倍,每个bin的噪声应比原始频谱低21dB。

这个处理可以通过在现有的Verilog代码上添加一个模块来完成。 18位数据字在传递到数据收集系统之前。然后编译新版本的代码,可用于在JTAG或主动串行编程模式下对DC2290A演示板进行编程。

梳状积分器级联滤波器

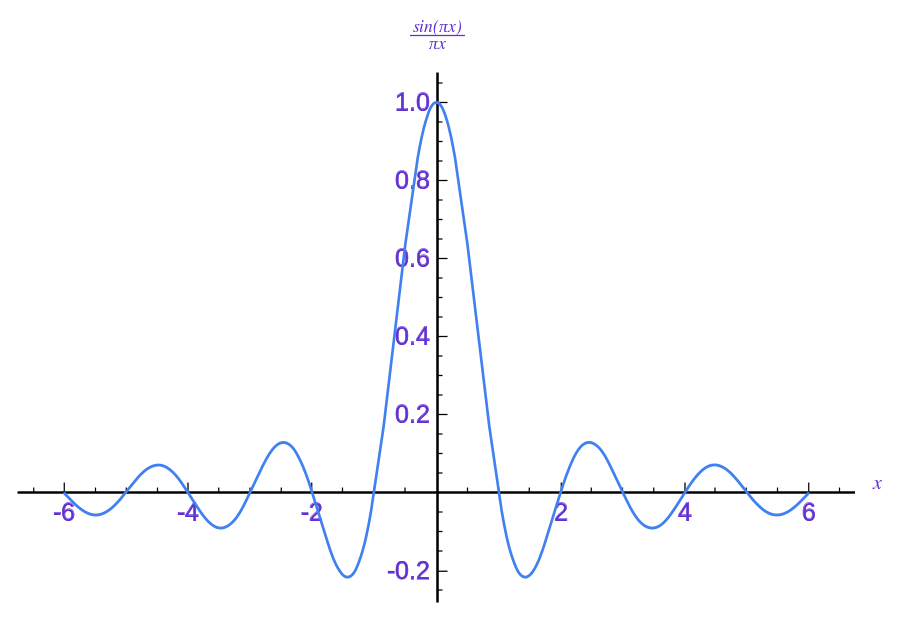

《 p》低通滤波器和下采样的一种简单方法是使用梳状积分器级联(CIC)滤波器。该过滤器的独特之处在于它不需要乘法。 CIC过滤器实际上只是移动平均(或boxcar)过滤器的另一个名称,后面跟着一个下采样器。注意,该滤波器的脉冲响应仅仅是一系列N个单位幅度样本。由于滤波器的时间响应是矩形脉冲,因此频率响应是Dirichlet函数。

sin(πfN)/(Nsin(πf))

此函数的第一个空值为Fs / N,在本例中为117.187KHz。下面是此过滤器的低频响应示例。

在Verilog中实现CIC过滤器

有几种方法可以实现此目的在Verilog过滤。一种方法是建立一个移位寄存器,该寄存器保存N个数据字,在加载每个新字时对寄存器的N个位置求和。然后对求和的输出进行下采样以形成最终输出。以下是N = 128的示例。

首先,FPGA对18位数据字进行反序列化。

该字以及运行频率为15MHz的时钟传递给模块cic_128

wire [17:0] dout,dout_f;

cic_128 fir(

.clk(fir_clk),

.din (DOUT),结果,.dout(dout_f),点击);

第一个变量是时钟;在转换的反序列化数据可用之后,此时钟的上升沿出现。接下来的两个变量是18位数据字 - 第一个是滤波器输入,第二个是输出。以下是模块本身的代码。

clk,

din,

dout

);

输入clk;

输入[17:0] din; //未过滤的样本

输出[17:0] dout; //过滤样本

reg [2303:0] shift_reg;

reg [24:0] regout;

reg [17:0] dout;

initial

shift_reg = 0;

wire [24:0] regout_a [63:0];

wire [24:0] regout_b [31:0];

wire [24:0] regout_c [15:0] ;

wire [24:0] regout_d [7:0];

wire [24:0] regout_e [3:0];

wire [24:0] regout_f [1:0]; 《 br》 wire [24:0] regout_g;

始终@(posedge clk)//在‘clk’的每个上升沿将最新的位加载到串行位数组中《 br》开始

:7];

end

genvar j;

生成

for(j = 0; j 《64; j = j + 1)

begin:echelon_a

assign regout_a [j] = {{7 {shift_reg [j * 18 + 17]}},shift_reg [j * 18 + 17:j * 18]} + {{7 {shift_reg [(j 64)* 18 + 17]}},shift_reg [第(j + 64)* 18 + 17:(J + 64)* 18]};结果,端

《跨度》 for(j = 0; j 《32; j = j + 1)开始:echelon_b

分配regout_b [j] = regout_a [j] + regout_a [j + 32];

结束

for(j = 0; j 《16; j = j + 1)开始:echelon_c

assign regout_c [j] = regout_b [j] + regout_b [ J + 16];结果,端

for(j = 0; j 《8; j = j + 1)开始:echelon_d

分配regout_d [j] = regout_c [j] + regout_c [j + 8]; 《 br》结束

for(j = 0; j 《4; j = j + 1)开始:echelon_e

assign regout_e [j] = regout_d [ j] + regout_d [j + 4];

end

for(j = 0; j 《2; j = j + 1)开始:echelon_f

分配regout_f [j] = regout_e [j] + regout_e [j + 2];

end

endgenerate

分配regout_g = regout_f [0] + regout_f [1];

endmodule

模块的核心是 shift_reg ;这是一个移位寄存器,可容纳128 x 18位字。这些字是一个接一个地加载到移位寄存器中的数据输入 din 。在每个时钟上升沿,最新的数据字被加载到寄存器中,最旧的数据字被丢弃。寄存器中128个位置的总和是滤波器的输出。然后将该输出按比例缩小7位以适合18位字,并作为 dout 传递回主模块。此时,这些样本的频谱只是ADC输出的低通滤波副本。

下一步是下采样,通过传递每128个滤波器样本来完成到数据采集板

第1部分的结果

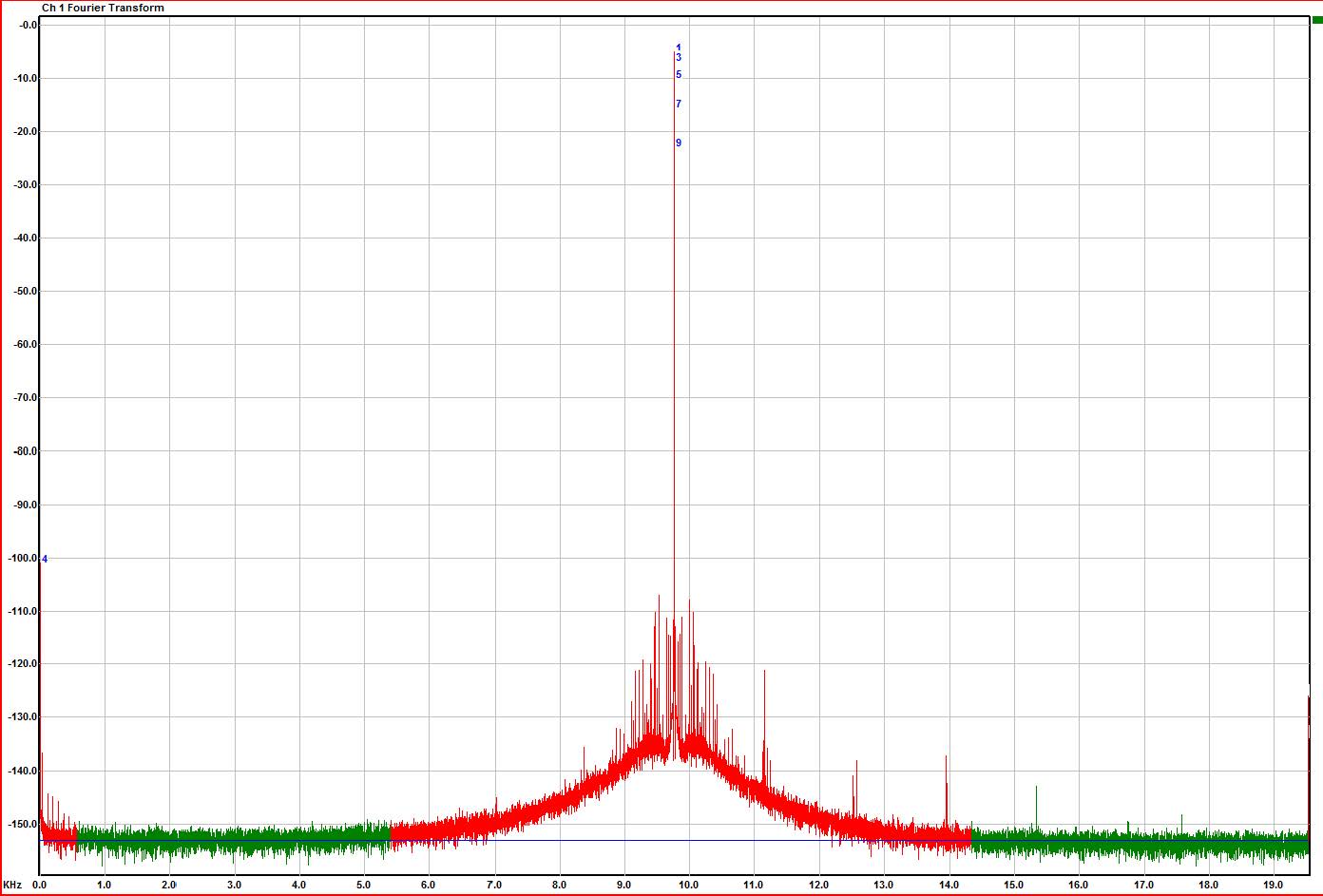

结果是一个覆盖从DC到58.593KHz的奈奎斯特区域的光谱。使用65K点的FFT,箱宽为1.78Hz。这是滤波和下采样信号的FFT,每个区间的噪声为-151.3dBFS。

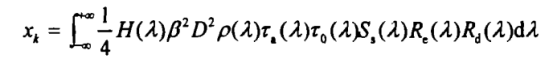

每个区间的噪声水平每箱减少了近12dB。由于两个原因,这低于预测的21dB减少。首先,因为滤波器不理想,所以在通带外存在非零响应。下采样过程会将这些非零波瓣中的噪声混叠回通带。这些旁瓣的总功率大约是主瓣功率的十分之一。其次,更重要的是,最终频谱中的量化噪声。对于正弦波,量化噪声使用以下公式计算,其中N是位数。

SNR = 1.76 + 6.02 * N

最终样本量化为18位,量化噪声约等于110.1dB,或每箱为155.3dBFS。通过滤波和下采样获得的结果接近这一水平,揭示了更多的光谱细节和分辨率。

使用Altera Cyclone III FPGA对这些数据进行反序列化和过滤是资源密集型的。 Verilog代码的编译报告显示该实现使用了74%的可用逻辑元素。原因是所需的寄存器和加法器的数量。在每个采样时刻,所有128个寄存器以二进制方式加在一起,梯队后梯队。尝试构建具有更高下采样率的滤波器将失败,因为该设计将不适合该FPGA。还有其他更简化的方法来构建这种类型的过滤器,我们将在下一部分中介绍它。右侧面板上提供了Verilog和本文所述代码的编程文件。

-

寄存器

+关注

关注

31文章

5336浏览量

120230 -

usb

+关注

关注

60文章

7936浏览量

264478 -

adc

+关注

关注

98文章

6495浏览量

544466

发布评论请先 登录

相关推荐

贸泽开售Analog Devices LTC6228和LTC6229运算放大器

[转帖]仪器仪表应用领域

【AD新闻】中国深圳先进院在高分辨率超声成像领域取得重要进展

LTC2386CUH-18PBF模数转换器

RF成像分辨率怎么提高

LTC2387-18正弦信号驱动器的设计要求

LT6201/LTC6655 Demo Circuit - Single-Ended to Differential Amplifier for LTC2387-18

成像光谱仪是一款具有高光谱分辨率方式获取图像信息的仪器

用于LTC2387-18 SAR ADC的单端至差分驱动器电路

提高LTC2387-18在高速成像和仪器仪表应用中的光谱分辨率

提高LTC2387-18在高速成像和仪器仪表应用中的光谱分辨率

评论