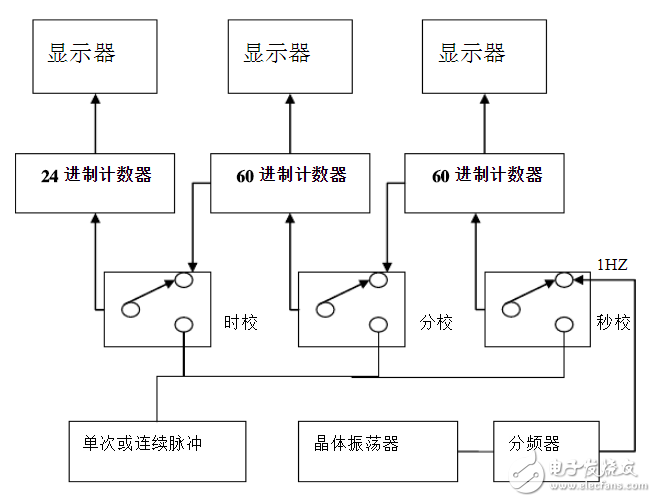

用单片机实现电子时钟设计方案时钟电路在计算机系统中起着非常重要的作用,是保证系统正常工作的基础。在一个单片机应用系统中,时钟有两方面的含义:一是指为保障系统正常工作的基准振荡定时信号,主要由晶振

2009-12-17 11:20:48

基于51单片机的电子时钟

2022-06-29 14:25:22 50

50 该压缩文件包含电子时钟源码及word文档

2022-06-13 14:18:23 1

1 电子时钟设计

2022-03-21 14:09:27 26

26 小信号放大电路设计方案汇总

2021-09-14 15:01:12 121

121 AC380V EMC标准电路设计方案

2021-07-12 10:54:06 48

48 AV接口EMC标准电路设计方案

2021-07-12 10:52:08 28

28 CAN总线接口EMC标准电路设计方案

2021-07-12 10:45:28 188

188 基于电流传输器的检测电路设计方案

2021-06-15 10:52:22 41

41 SSS1530电路设计方案免费下载。

2021-06-10 16:22:57 26

26 带NFC管理的移动通信终端电路设计方案

2021-06-07 10:17:16 30

30 卡拉OK人声增效电路设计方案

2021-03-25 11:06:33 7

7 电子发烧友网站提供(温度传感器电路设计方案)资料免费下载。

2020-11-11 12:00:26 104

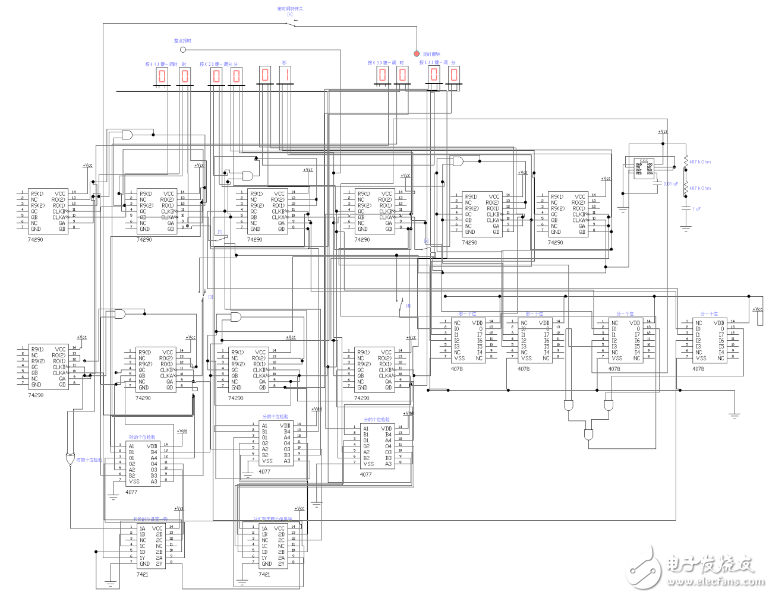

104 本文档的主要内容详细介绍的是使用Protel 99SE实现电子时钟的电路图免费下载。

2020-11-02 08:00:00 22

22 使用verilog语言,实现电子时钟,包含功能时,分的调整,整点音乐和led花样显示

2020-07-01 08:00:00 5

5 本文档的主要内容详细介绍的是Arduino实现电子时钟的库文件资料合集免费下载。

2020-06-02 08:00:00 4

4 本文档的主要内容详细介绍的是使用51单片机实现的电子时钟源代码和电路图及仿真资料合集免费下载。

2020-03-06 08:00:00 13

13 485接口EMC电路设计方案!

2020-02-05 12:53:27 3778

3778 本文档的主要内容详细介绍的是电子时钟应用程序免费下载。

2019-04-30 08:00:00 1

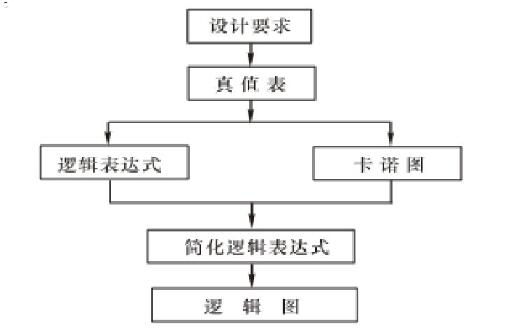

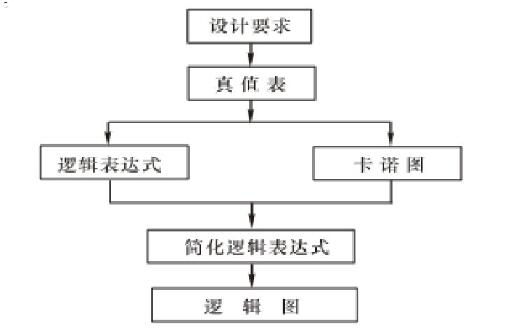

1 完成电子电路设计方案的过程大致分几个步骤?需要注意什么?

2019-04-12 17:45:52 13438

13438 电子时钟系统设计的详细资料和详细源代码函数资料免费下载

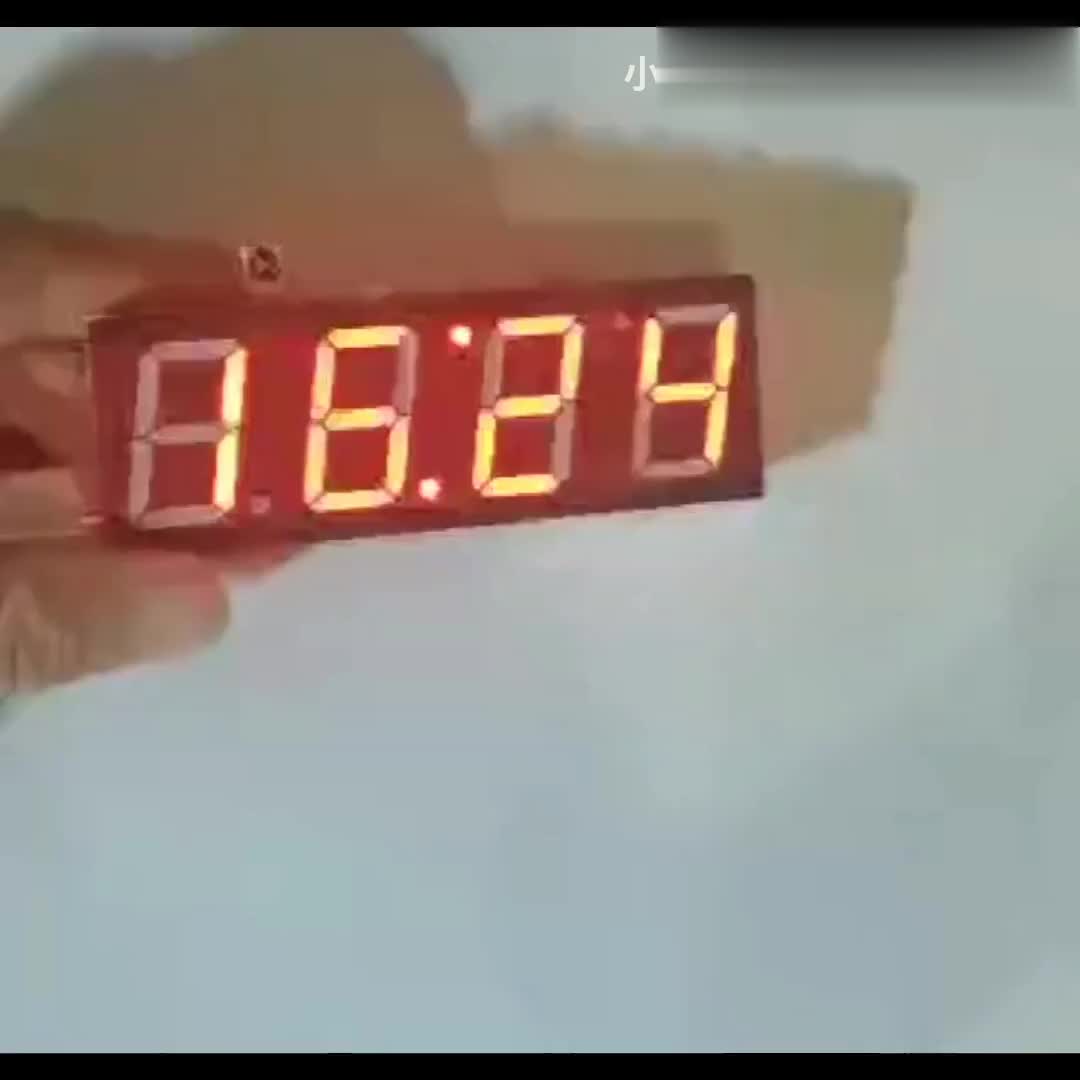

1、软件编程实现数字电子钟的显示,显示格式“时-分-秒” 2、时间可以通过键盘预制 3、采用74HC138实现共阴极数码管的位控; 4、矩阵键盘读键方法 5、时间设置方法不限

2018-08-30 08:00:00 21

21 在当前的数字集成电路设计中,同步电路占了绝大部分。所谓同步电路,即电路中的所有寄存器由为数不多的几个全局时钟驱动,被相同时钟信号驱动的寄存器共同组成一个时钟域,并可认为同时时钟域内所有寄存器的时钟沿同时到达。

2018-07-12 09:02:00 5289

5289

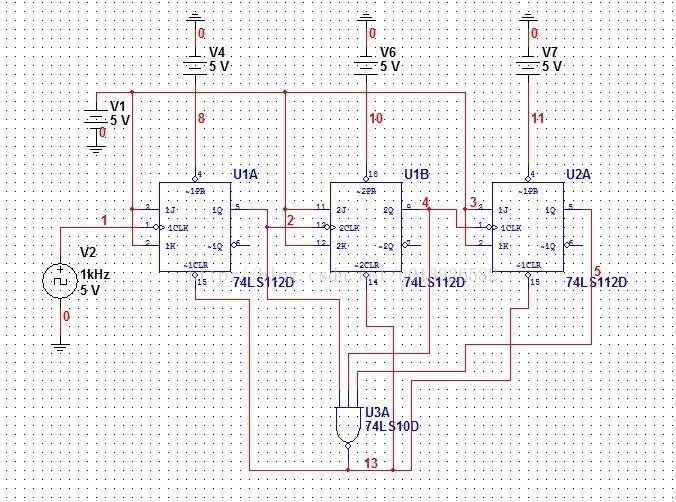

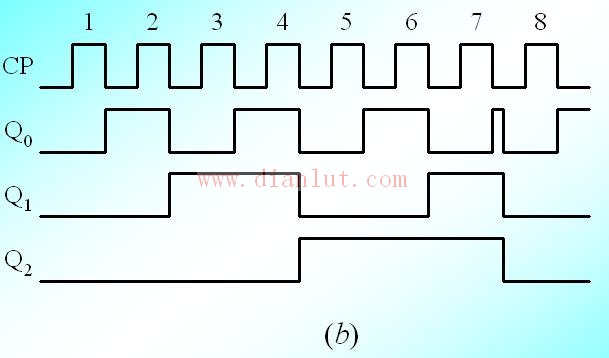

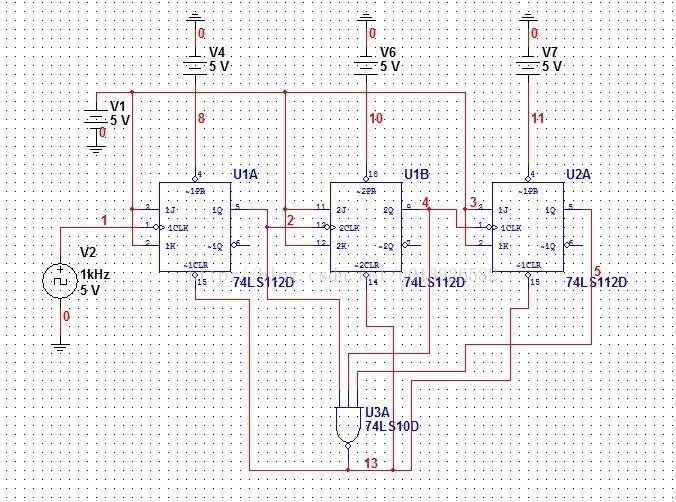

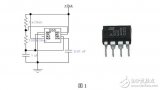

本文主要详解两款74ls112应用电路图,分别是模七计数器/抢答器的电路设计,具体的跟随小编一起来了解一下。

2018-05-29 18:50:19 57412

57412

本文主要详解数值比较器74ls85的中文资料,首先介绍了74ls85引脚图及功能,其次阐述了74ls85真值表,最后介绍了74ls85应用电路图,具体的跟随小编一起来了解一下。

2018-05-29 16:03:43 182367

182367

本文主要介绍了五款74ls192计数器应用电路图。其中包括了74ls192电子骰子电路、74ls192计时电路、74ls192定时电路、74ls19230进制计数器电路及两位十进制计数器。

2018-05-28 10:20:01 116393

116393

基于FPGA的调焦电路设计方案资料下载

2018-05-07 15:53:08 9

9 本文主要介绍了五款74ls138的应用电路图。其中包括了74ls138全加器电路、74ls138抢答器电路、74ls138实现逻辑函数、74ls138全减器电路以及与74LS20组合的三人表决器电路。

2018-05-04 10:31:55 87718

87718

DSP中2812的电子时钟参考程序

2018-04-12 08:45:07 12

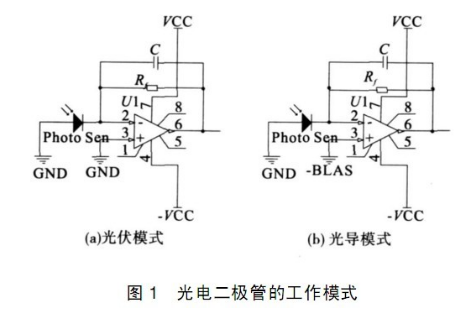

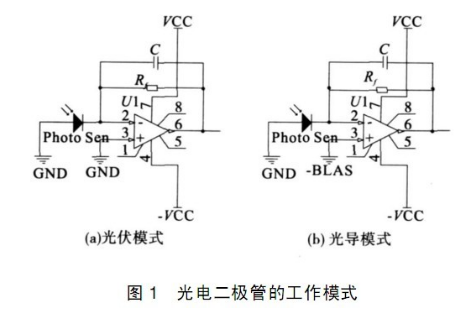

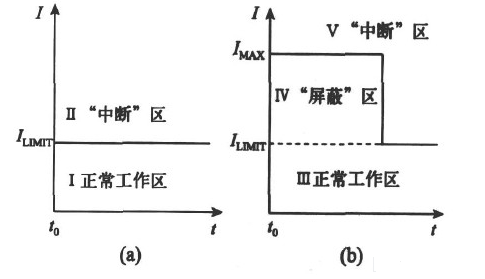

12 本文主要介绍了光电转换电路设计方案汇总(三款模拟电路设计原理图详解),光电转换电源是一种基于光供能的、采用光纤传输的、输出电压值不受电网波动影响的稳压源。它是光传能技术中的关键部件,具有良好

2018-02-06 11:53:02 65896

65896

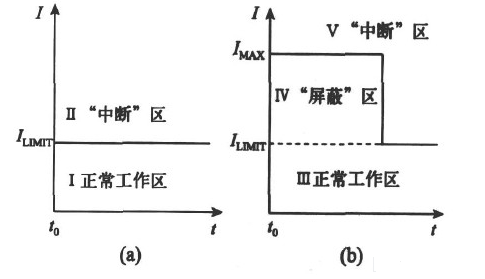

本文主要介绍了电流检测电路设计方案汇总(六款模拟电路设计原理图详解),采用差分运放进行高端电流检测的电路更便于使用,因为近期推出了许多种集成电路解决方案。专用高端检流电路内部包含了完成高端电流检测

2018-02-06 11:31:39 320822

320822

本文主要介绍了简单过流保护电路设计方案汇总(七款模拟电路设计原理图详解)。过流保护用PTC热敏电阻通过其阻值突变限制整个线路中的消耗来减少残余电流值。可取代传统的保险丝,广泛用于马达、变压器

2018-02-01 14:29:59 133646

133646

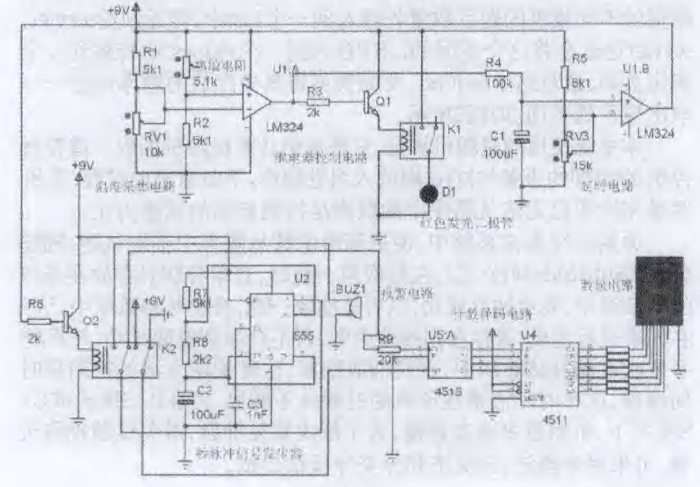

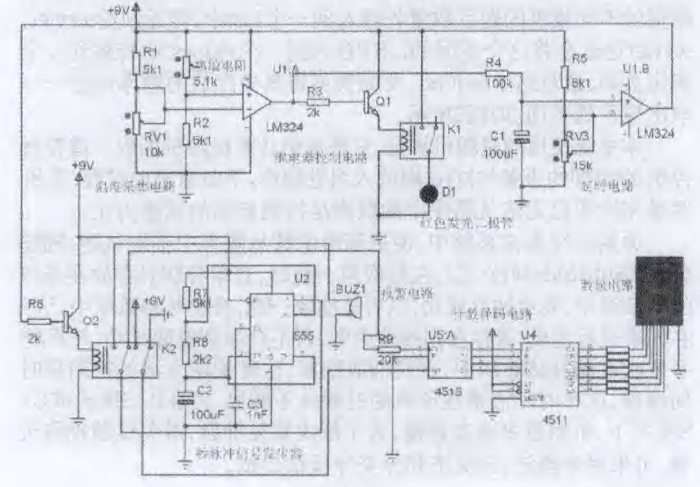

本文主要介绍了计数报警器电路设计方案汇总(多款模拟电路设计原理图详解),方案二主要由直流电源电路(整流、滤波、稳压电路)和计数报警电路(计数电路、译码电路、显示电路、声光报警电路)组成,:声光报警功能用蜂鸣器和LED灯实现,控制LED报警十秒,蜂鸣器报警10秒。

2018-01-29 10:30:07 22300

22300

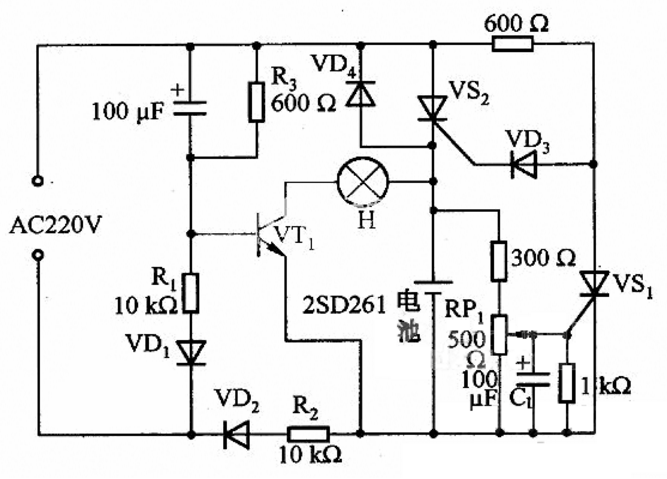

本文主要介绍了超温报警器电路设计方案汇总(六款模拟电路设计原理图详解),方案一中超温报警电路由温度采集电路、继电器控制电路、延时电路、秒脉冲信号发生器、计数译码电路、数显电路、报警电路共同构成。当

2018-01-29 10:10:27 27863

27863

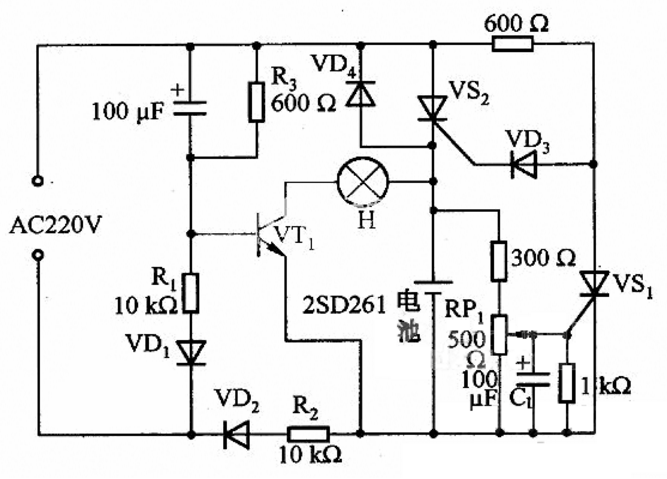

本文主要介绍了停电报警器电路设计方案汇总(五款模拟电路设计原理图详解),方案三分析了大部分电冰箱没有延时断电保护器,市电偶尔断电,瞬间又恢复供电,会对电冰箱造成不利影响,而白天又不易发现停电,有了光

2018-01-28 10:20:09 33048

33048

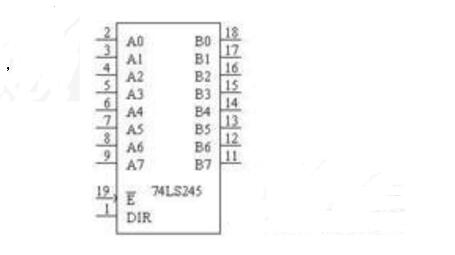

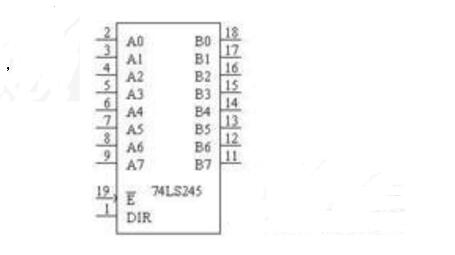

本文开始介绍了74HC245的作用与74hc245引脚及功能,其次介绍了 74LS245工作原理,最后介绍了74LS245N使用及仿真详解。

2018-01-27 09:40:16 52450

52450

本文介绍了4种方式实现三人表决电路。其中包括用74LS00,74LS20实现三人表决电路、用译码器138和与非门74LS20设计实现三人表决电路、用8选1数据选择器74LS151实现三人表决电路以及用4选1数据选择器74LS153实现三人表决电路方法。

2018-01-26 17:26:20 311881

311881

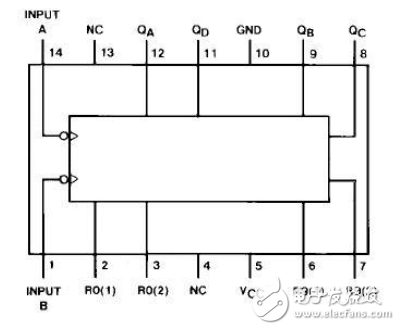

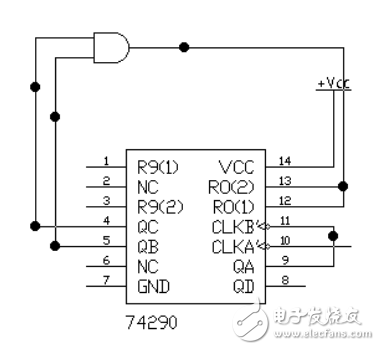

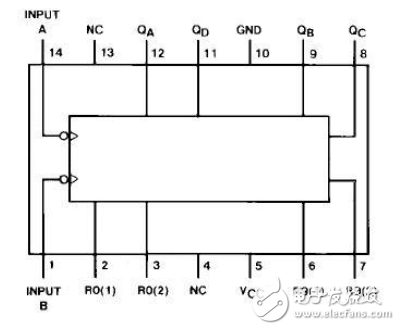

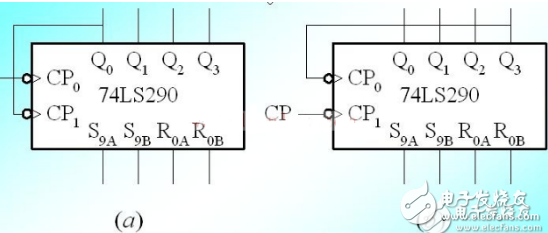

74LS290和74LS90都是二分频,五分频十进制计数器,功能相同,74LS290改变了引线排列。引线脚排列不同.

2018-01-26 10:09:24 22390

22390

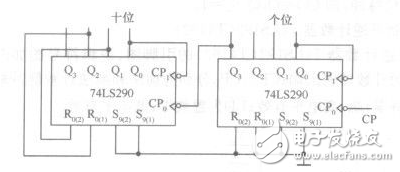

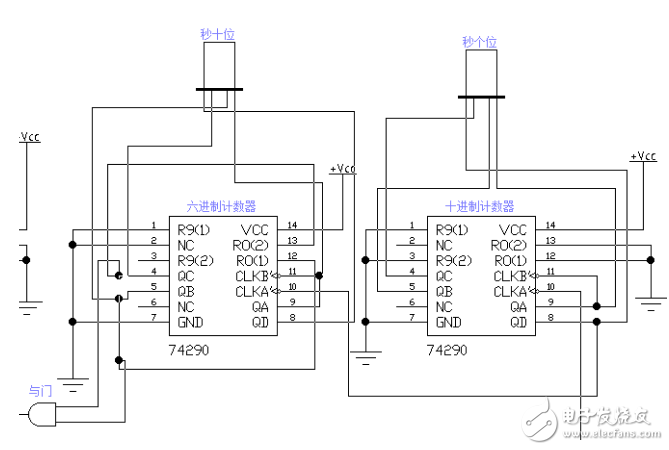

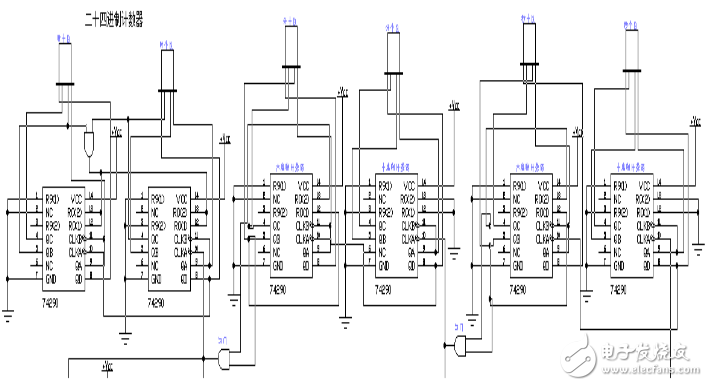

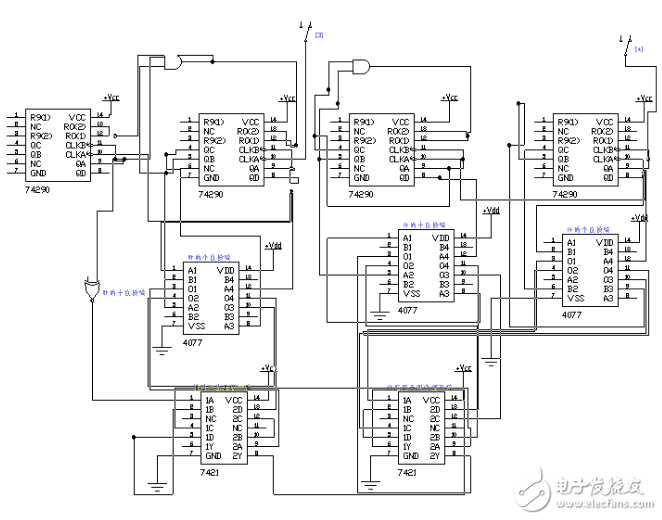

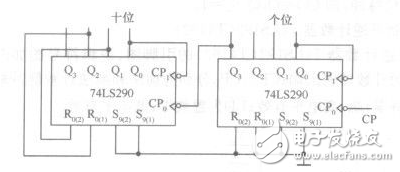

六十进制由二片74LS290组成,分别连成六进制和十进制。个位为十进制,十位为六进制。当十位计到6时,个位、十位同时清零,

2018-01-26 09:33:53 23224

23224

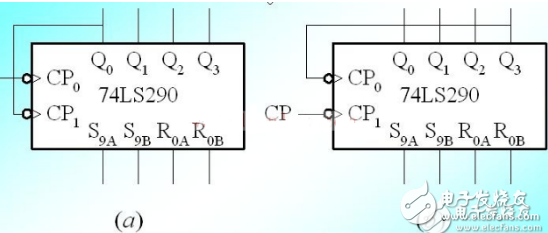

74ls290是一个二,五,十进制计数器,本文为大家介绍由74ls290构成的各种进制计数器的电路。

2018-01-26 09:26:11 106188

106188

本文为大家带来四种74ls290典型应用电路图分享。

2018-01-25 15:50:23 21435

21435

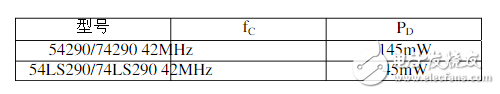

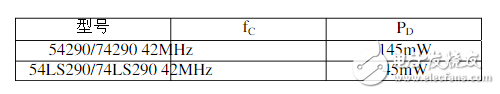

74LS290为二,五,十进制计数器,共有54/74290和54/74LS290两种线路结构型式。

2018-01-25 15:31:26 137973

137973

计数器在数字系统中应用广泛,如在电子计算机的控制器中对指令地址进行计数,以便顺序取出下一条指令,在运算器中作乘法、除法运算时记下加法、减法次数,又如在数字仪器中对脉冲的计数等等。本文为大家介绍74LS290组成的十进制计数器。

2018-01-25 14:52:47 25181

25181

74LS290为异步二-五-十进制加法计数器。本文为大家介绍74ls290构成31进制计数器电路。

2018-01-25 14:36:39 16924

16924

本文为大家带来五种三人表决器电路设计方案,包括两款仿真电路及程序分析,三款逻辑电路设计的原理详解。

2018-01-17 18:49:21 280403

280403

本文为大家带来九款不同的除法运算电路设计方案,包括这九款模拟电路设计的原理及设计过程。

2018-01-17 18:24:49 46006

46006

本文为大家带来五种减法器电路设计方案介绍。

2018-01-17 11:29:44 83406

83406

74LS194作为四位双向移存器,目前已经得到广泛的运用。本文主要介绍了74LS194的引脚图、74LS194结构框图已经74LS194移位寄存器的应用电路。

2017-12-22 17:03:14 36342

36342

本文介绍了555定时器与74ls194进行了详细的说明。然后采用两者的结合详解的介绍了一个74ls194控制8个流水灯的设计方案详情。

2017-12-22 09:39:18 123615

123615

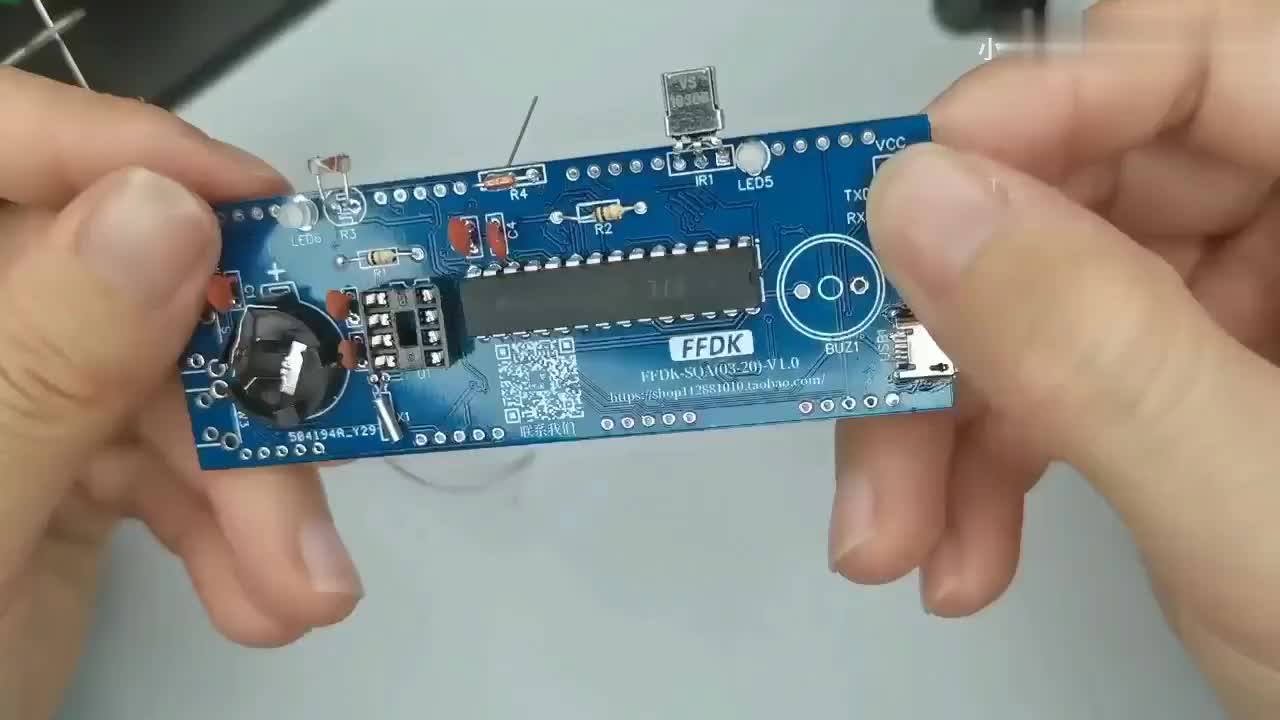

DS1302 电子时钟设计 主要硬件组成 单片机 STC89C52,DS1302,纽扣电池,LCD1602,四个对地按键 S1-S4,蜂鸣器,DS18B20 字符显示位置设定

2017-11-27 14:45:06 28

28 电子发烧友网站提供《电子时钟设计电子时钟程序相关资料下载.zip》资料免费下载

2017-05-26 08:00:00 104

104 可调闹钟电子时钟

2017-03-05 14:21:04 66

66 DS1302电子时钟电路方案

2017-02-15 22:31:23 26

26 精密光电检测电路设计方案

2016-12-15 18:25:41 63

63 关于74LS290的芯片介绍以及常用的几种接法。

2016-07-13 15:11:08 38

38 整个电子时钟系统电路可分为五大部分:中央处理单元(CPU)、电源电路部分、显示部分、键盘输入部分、温度采集部分

2016-06-17 16:16:12 5

5 关于ATMEGA16的电子时钟设计,比较详细。

2016-05-10 16:31:07 4

4 电子时钟。

2016-04-19 15:45:00 205

205 电子时钟设计。

2016-04-19 15:17:10 91

91 用单片机设计电子时钟方案集合。用单片机设计电子时钟方案集合

2015-12-28 12:00:46 29

29 这是个电子时钟,可以设置时和分,需要的可以看一下

2015-12-14 15:22:23 3

3 简易电子时钟程序,拥有详细的控制程序编码,工读者使用

2015-12-08 17:12:58 27

27 多功能电子时钟程序,感兴趣的可以下载看看!

2015-12-02 10:23:55 47

47 实用电子电路设计制作详解,电子基础实用电子电路设计制作详解

2015-11-17 11:44:00 52

52 DS12C887高精度电子时钟设单片机设计课程。DS12C887高精度电子时钟设

2015-10-29 16:18:38 14

14 计数器是常用的时序逻辑电路器件,文中介绍了以四位同步二进制集成计数器74LS161和异步二-五-十模值计数器74LS290为主要芯片,设计实现了任意模值计数器电路,并用Multisim软件进行了

2013-07-26 11:38:41 133

133 The SN54290/SN74290, SN54LS290/SN74LS290, SN54293/SN74293, and SN54LS293/SN74LS293 counters

2010-08-10 16:10:06 27

27 摘要:论述了选择时钟芯片DSl302制作电子时钟日历系统的难点问题;分析了一款选择AT89C51作为主控芯片的电子时钟硬件电路的工作原理,以及设计硬件电路时的注意事项;给出了主

2010-07-21 22:20:53 112

112 百进制计数器电路

将两块74LS290进行级联,组成的百进制计数器如图12.8所示。

2009-09-16 15:47:50 5541

5541

74LS290组成七进制计数器?

解 首先,将74LS290的CP1端与Q0端相接,使

2009-09-16 15:46:35 8926

8926

74LS688/74LS682/74LS684/74LS685/74LS687 pdf datasheet

2008-08-06 12:41:13 41

41 54/74290二,五,十进制计数器简要说明:290为二,五,十进制计数器,共有 54/74290 和 54/74LS290 两种线路结构型式,其主要电器特性的典型值如下(不同厂家具体值有差别):

2008-03-15 13:08:47 214

214

正在加载...

电子发烧友App

电子发烧友App

评论