Lattice公司的ispPAC-POWR1220AT8集成了在系统可编程逻辑和在系统可编程模拟功能,是通用的电源监视器,顺序和余量控制器,它提供12个单独的模拟输入通道,用来监视多达12个电源测试点. POWR1220AT8提供和IPMC标准的命令接口,能把板上的DC/DC转换器转换成精密的数控电源.本文介绍了ispPAC-POWR1220AT8主要特性,方框图,以及应用方框图, 评估板外形图,采用ispPAC-POWR1220AT8的12V热插拔控制器参考设计电路图.

The Lattice Power Manager II ispPAC-POWR1220AT8 is a general-purpose power-supply monitor, sequence and margin controller, incorporating both in-system pro-grammable logic and in-system programmable analog functions implemented in non-volatile E2CMOS® tech-nology. The ispPAC-POWR1220AT8 device provides 12 independent analog input channels to monitor up to 12 power supply test points. Each of these input channels offers a differential input to support remote ground sensing, and has two independently programmable comparators to support both high/low and in-bounds/ out-of-bounds (window-compare) monitor functions. Six general-purpose digital inputs are also provided for mis-cellaneous control functions. The ispPAC-POWR1220AT8 provides 20 open-drain digital outputs that can be used for controlling DC-DC converters, low-drop-out regulators (LDOs) and opto-couplers, as well as for supervisory and general-pur-pose logic interface functions. Four of these outputs(HVOUT1-HVOUT4) may be configured as high-voltage MOSFET drivers. In high-voltage mode these outputs can provide up to 12V for driving the gates of n-channel MOSFETs so that they can be used as high-side power switches controlling the supplies with a programmable ramp rate for both ramp up and ramp down. The ispPAC-POWR1220AT8 incorporates a 48-macrocell CPLD that can be used to implement complex state machine sequencing for the control of multiple power supplies as well as combinatorial logic functions. The status of all of the comparators on the analog input channels as well as the general purpose digital inputs are used as inputs by the CPLD array, and all digital outputs may be controlled by the CPLD. Four independently programmable timers can create delays and time-outs ranging from 32μs to 2 seconds. The CPLD is programmed using Logi- Builder™, an easy-to-learn language integrated into the PAC-Designer® software. Control sequences are written to monitor the status of any of the analog input channel comparators or the digital inputs. In addition to the sequence control functions, the ispPAC-POWR1220AT8 incorporates eight DACs for generating trimming voltage to control the output voltage of a DC-DC converter. The trimming voltage can be set to four hard-ware selectable preset values (voltage profiles) or can be dynamically loaded in to the DAC through the I2C bus. Additionally, each power supply output voltage can be maintained typically within 0.5% tolerance across various load conditions using the Digital Closed Loop Control mode. The operating voltage profile can either be selected using external hardware pins or through the PLD outputs. The on-chip 10-bit A/D converter can both be used to monitor the VMON voltage through the I2C bus as well as for implementing digital closed loop mode for maintaining the output voltage of all power supplies controlled by the monitoring and trimming section of the ispPAC-POWR1220AT8 device. The I2C bus/SMBus interface allows an external microcontroller to measure the voltages connected to the VMON inputs, read back the status of each of the VMON comparator and PLD outputs, control logic signals IN2 to IN5, con-trol the output pins, and load the DACs for the generation of the trimming voltage of the external DC-DC converter.

ispPAC-POWR1220AT8 主要特性:

Monitor, Control, and Margin Multiple Power Supplies

• Simultaneously monitors up to 12 power supplies

• Provides up to 20 output control signals

• Provides up to eight analog outputs for margining/trimming power supply voltages

•Programmable digital and analog circuitry

Power Supply Margin and Trim Functions

• Trim and margin up to eight power supplies

• Dynamic voltage control through I2C

• Four hardware selectable voltage profiles

•Independent Digital Closed-Loop Trim function for each output

Embedded PLD for Sequence Control

•48-macrocell CPLD implements both state machines and combinatorial logic functions

Embedded Programmable Timers

• Four independent timers

•32μs to 2 second intervals for timing sequences

Analog Input Monitoring

• 12 independent analog monitor inputs

• Differential inputs for remote ground sense

• Two programmable threshold comparators per analog input

• Hardware window comparison

•10-bit ADC for I2C monitoring

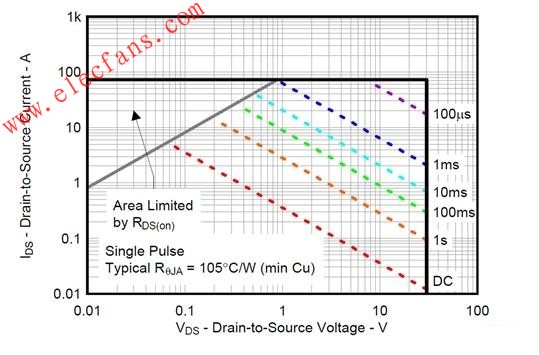

High-Voltage FET Drivers

• Power supply ramp up/down control

• Programmable current and voltage output

•Independently configurable for FET control or digital output

2-Wire (I2C/SMBus™ Compatible) Interface

• Comparator status monitor

• ADC readout

• Direct control of inputs and outputs

• Power sequence control

•Dynamic trimming/margining control

3.3V Operation, Wide Supply Range 2.8V to 3.96V

• In-system programmable through JTAG

• Industrial temperature range: -40℃ to +85℃

•100-pin TQFP package, lead-free option

ispPAC-POWR1220AT8典型应用:

The Power Manager II POWR1220AT8 provides a standard command interface to the IPMC while performing FRU specific payload power management functions using the on-chip CPLD. The POWR1220AT8 also converts all on board DC-DC converters into accurate digitally controlled supplies.

图1.ispPAC-POWR1220AT8方框图

图2.ispPAC-POWR1220AT8应用方框图

图3.ispPAC-POWR1220AT8提高DC/DC转换器精度的应用方框图

The PAC-POWR1220AT8 evaluation board allows the designer to quickly configure and evaluate the ispPAC-POWR1220AT8 device on a fully assembled printed-circuit board. The four-layer board supports a 100-pin TQFP package, pads for user I/O, a JTAG programming cable connector, and a connector for the device’s I2C interface. JTAG programming signals can be generated by using an ispDOWNLOAD® programming cable connected between the evaluation board and a PC. Both analog and digital features of the ispPACPOWR1220AT8 device can be easily configured using PAC-Designer® software.

The PAC-POWR1220AT8 evaluation board is available in a Development Kit that includes:

PAC-POWR1220AT8 Evaluation Board

ispDOWNLOAD Cable

AC Adapter (International plugs)

User Documentation

图4.ispPAC-POWR1220AT8评估板外形图

采用ispPAC-POWR1220AT8的12V热插拔控制器参考设计

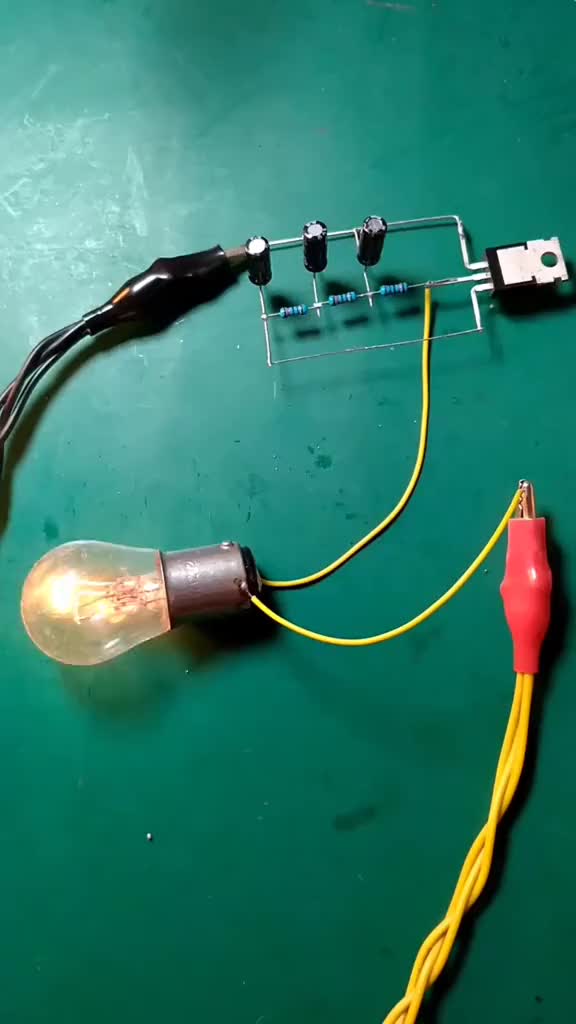

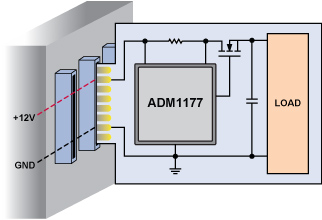

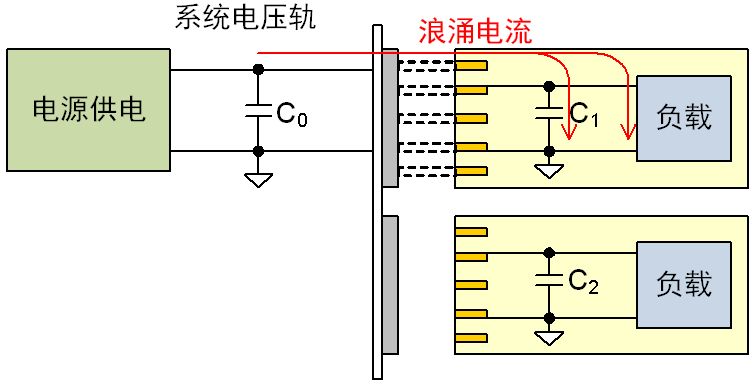

A hot swap controller is used to limit the inrush current when a circuit board is plugged into a powered backplane.

In addition, a hot swap controller may offer some or all of the following features: over-current protection (electronic circuit breaker), over-voltage protection, and under-voltage protection. Hot swap controllers are also required to isolate the board from the backplane which is useful in troubleshooting, maintenance, and upgrade activities. The power-down request may come from the backplane (remote) or an on-board switch (manual).

This document describes how a Lattice Power Manager II ispPAC®-POWR1220AT8 can be used to implement the functions required for 12V hot swap applications. This reference design is targeted to operate on the Power Manager Hercules Development Kit (PAC-POWR1220AT8-HS-EVN – Standard or PAC-POWR1220AT8-HA-EVN –Advanced).

12V热插拔控制器主要特性:

• Programmable inrush current limit (default 2 amps)

• Programmable de-bounce delay (default 30ms)

• Programmable over-current limit (default 15 amps)

• Over and under-voltage limits both at source and load

• Short circuit protection

• Programmable SOA drive of N-channel MOSFET

• Power supply OR’ing

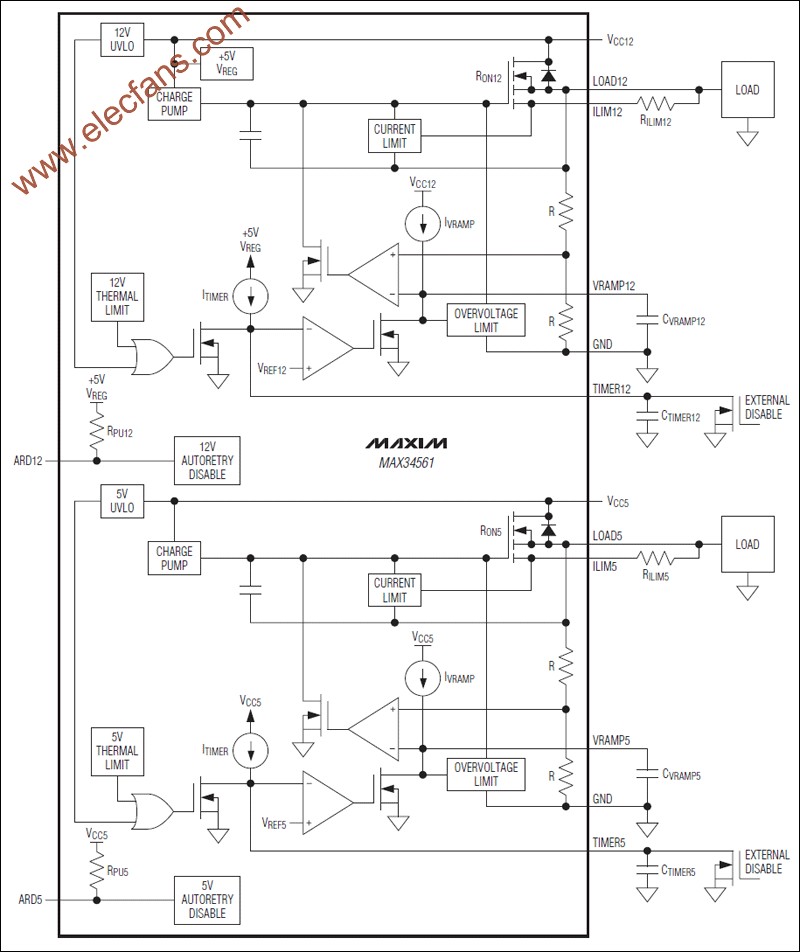

图5. 12V热插拔控制器框图

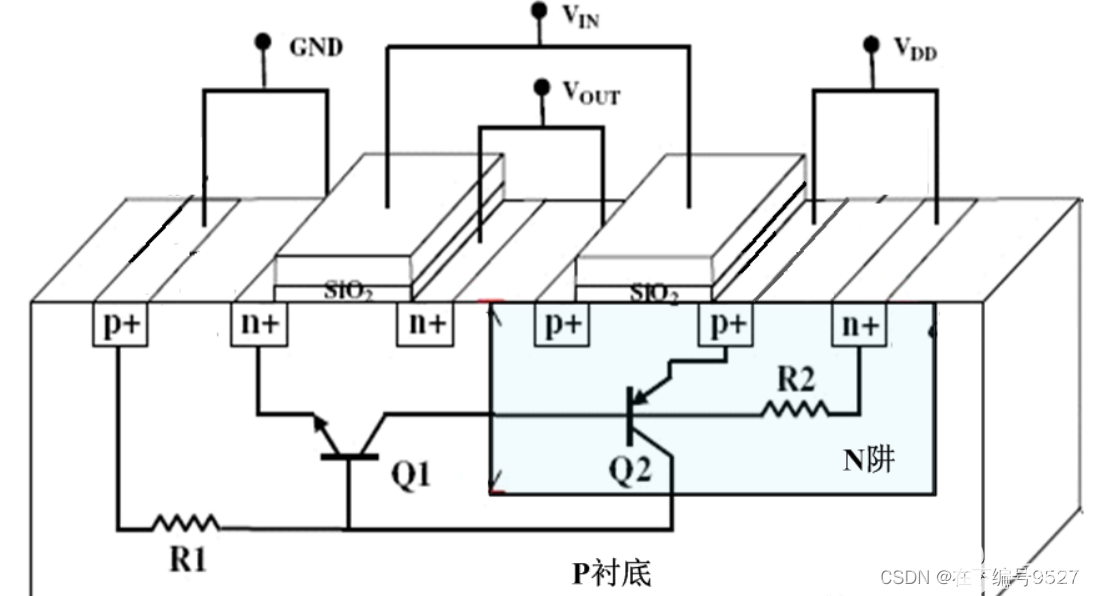

图6. ispPAC-POWR1220AT8电源管理电路图

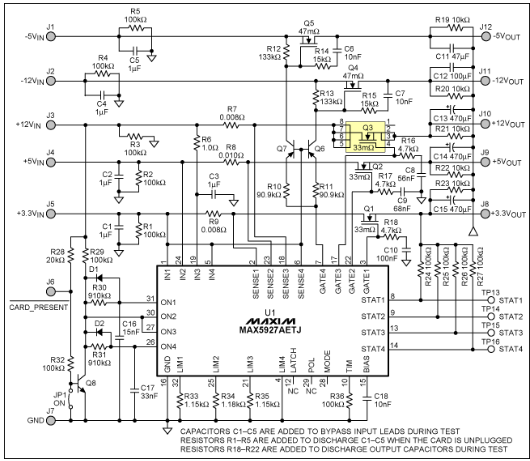

图7. 12V热插拔控制器电路图

The Lattice Power Manager II ispPAC-POWR1220AT8 is a general-purpose power-supply monitor, sequence and margin controller, incorporating both in-system pro-grammable logic and in-system programmable analog functions implemented in non-volatile E2CMOS® tech-nology. The ispPAC-POWR1220AT8 device provides 12 independent analog input channels to monitor up to 12 power supply test points. Each of these input channels offers a differential input to support remote ground sensing, and has two independently programmable comparators to support both high/low and in-bounds/ out-of-bounds (window-compare) monitor functions. Six general-purpose digital inputs are also provided for mis-cellaneous control functions. The ispPAC-POWR1220AT8 provides 20 open-drain digital outputs that can be used for controlling DC-DC converters, low-drop-out regulators (LDOs) and opto-couplers, as well as for supervisory and general-pur-pose logic interface functions. Four of these outputs(HVOUT1-HVOUT4) may be configured as high-voltage MOSFET drivers. In high-voltage mode these outputs can provide up to 12V for driving the gates of n-channel MOSFETs so that they can be used as high-side power switches controlling the supplies with a programmable ramp rate for both ramp up and ramp down. The ispPAC-POWR1220AT8 incorporates a 48-macrocell CPLD that can be used to implement complex state machine sequencing for the control of multiple power supplies as well as combinatorial logic functions. The status of all of the comparators on the analog input channels as well as the general purpose digital inputs are used as inputs by the CPLD array, and all digital outputs may be controlled by the CPLD. Four independently programmable timers can create delays and time-outs ranging from 32μs to 2 seconds. The CPLD is programmed using Logi- Builder™, an easy-to-learn language integrated into the PAC-Designer® software. Control sequences are written to monitor the status of any of the analog input channel comparators or the digital inputs. In addition to the sequence control functions, the ispPAC-POWR1220AT8 incorporates eight DACs for generating trimming voltage to control the output voltage of a DC-DC converter. The trimming voltage can be set to four hard-ware selectable preset values (voltage profiles) or can be dynamically loaded in to the DAC through the I2C bus. Additionally, each power supply output voltage can be maintained typically within 0.5% tolerance across various load conditions using the Digital Closed Loop Control mode. The operating voltage profile can either be selected using external hardware pins or through the PLD outputs. The on-chip 10-bit A/D converter can both be used to monitor the VMON voltage through the I2C bus as well as for implementing digital closed loop mode for maintaining the output voltage of all power supplies controlled by the monitoring and trimming section of the ispPAC-POWR1220AT8 device. The I2C bus/SMBus interface allows an external microcontroller to measure the voltages connected to the VMON inputs, read back the status of each of the VMON comparator and PLD outputs, control logic signals IN2 to IN5, con-trol the output pins, and load the DACs for the generation of the trimming voltage of the external DC-DC converter.

ispPAC-POWR1220AT8 主要特性:

Monitor, Control, and Margin Multiple Power Supplies

• Simultaneously monitors up to 12 power supplies

• Provides up to 20 output control signals

• Provides up to eight analog outputs for margining/trimming power supply voltages

•Programmable digital and analog circuitry

Power Supply Margin and Trim Functions

• Trim and margin up to eight power supplies

• Dynamic voltage control through I2C

• Four hardware selectable voltage profiles

•Independent Digital Closed-Loop Trim function for each output

Embedded PLD for Sequence Control

•48-macrocell CPLD implements both state machines and combinatorial logic functions

Embedded Programmable Timers

• Four independent timers

•32μs to 2 second intervals for timing sequences

Analog Input Monitoring

• 12 independent analog monitor inputs

• Differential inputs for remote ground sense

• Two programmable threshold comparators per analog input

• Hardware window comparison

•10-bit ADC for I2C monitoring

High-Voltage FET Drivers

• Power supply ramp up/down control

• Programmable current and voltage output

•Independently configurable for FET control or digital output

2-Wire (I2C/SMBus™ Compatible) Interface

• Comparator status monitor

• ADC readout

• Direct control of inputs and outputs

• Power sequence control

•Dynamic trimming/margining control

3.3V Operation, Wide Supply Range 2.8V to 3.96V

• In-system programmable through JTAG

• Industrial temperature range: -40℃ to +85℃

•100-pin TQFP package, lead-free option

ispPAC-POWR1220AT8典型应用:

The Power Manager II POWR1220AT8 provides a standard command interface to the IPMC while performing FRU specific payload power management functions using the on-chip CPLD. The POWR1220AT8 also converts all on board DC-DC converters into accurate digitally controlled supplies.

图1.ispPAC-POWR1220AT8方框图

图2.ispPAC-POWR1220AT8应用方框图

图3.ispPAC-POWR1220AT8提高DC/DC转换器精度的应用方框图

The PAC-POWR1220AT8 evaluation board allows the designer to quickly configure and evaluate the ispPAC-POWR1220AT8 device on a fully assembled printed-circuit board. The four-layer board supports a 100-pin TQFP package, pads for user I/O, a JTAG programming cable connector, and a connector for the device’s I2C interface. JTAG programming signals can be generated by using an ispDOWNLOAD® programming cable connected between the evaluation board and a PC. Both analog and digital features of the ispPACPOWR1220AT8 device can be easily configured using PAC-Designer® software.

The PAC-POWR1220AT8 evaluation board is available in a Development Kit that includes:

PAC-POWR1220AT8 Evaluation Board

ispDOWNLOAD Cable

AC Adapter (International plugs)

User Documentation

图4.ispPAC-POWR1220AT8评估板外形图

采用ispPAC-POWR1220AT8的12V热插拔控制器参考设计

A hot swap controller is used to limit the inrush current when a circuit board is plugged into a powered backplane.

In addition, a hot swap controller may offer some or all of the following features: over-current protection (electronic circuit breaker), over-voltage protection, and under-voltage protection. Hot swap controllers are also required to isolate the board from the backplane which is useful in troubleshooting, maintenance, and upgrade activities. The power-down request may come from the backplane (remote) or an on-board switch (manual).

This document describes how a Lattice Power Manager II ispPAC®-POWR1220AT8 can be used to implement the functions required for 12V hot swap applications. This reference design is targeted to operate on the Power Manager Hercules Development Kit (PAC-POWR1220AT8-HS-EVN – Standard or PAC-POWR1220AT8-HA-EVN –Advanced).

12V热插拔控制器主要特性:

• Programmable inrush current limit (default 2 amps)

• Programmable de-bounce delay (default 30ms)

• Programmable over-current limit (default 15 amps)

• Over and under-voltage limits both at source and load

• Short circuit protection

• Programmable SOA drive of N-channel MOSFET

• Power supply OR’ing

图5. 12V热插拔控制器框图

图6. ispPAC-POWR1220AT8电源管理电路图

图7. 12V热插拔控制器电路图

电子发烧友App

电子发烧友App

评论