长期平均误码率,简称误码率(BitErrorRate,BER),是光通信网络及设备的重要指标之一。目前光通信网络及设备正朝着小型化、高频率、高速率、大容量的方向发展,对作为测量仪器的误码测试仪速率及功能的要求也越来越高。虽然国内外仪器仪表厂,如安捷伦(Agilent)、泰克(Tektronix)等推出了各种高速误码测试仪,但是大多价格昂贵,并且系统复杂。所以,对于国内通信行业,开发一种价廉、方便、速率可达10 Gb/s的高速误码测试系统,具有实用价值。

1 系统概述

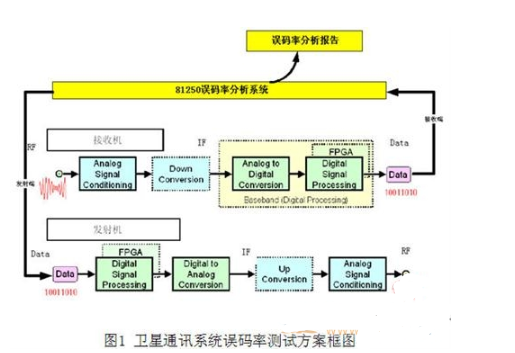

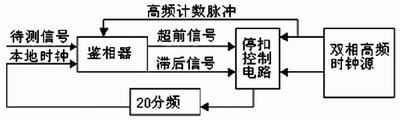

本误码测试系统由两部分组成:误码测试部分和上位机人机界面部分。其中误码测试部分由高速误码仪、光衰减器、光功率计和光源等组成。高速误码仪以微控制器ADμC7020为核心,控制XFP收发控制器Si5040来实现。

ADμC7020是ADI公司的基于ARM7TDMI的体系结构的控制器,支持16/32位精简指令集(RISC)。片内集成了12位的ADC(1MSPS)、4通道12位带缓冲的DAC、电压比较器、62 KB可在系统中编程(ISP)的片内闪速/电擦除存储器Flash和8 KB RAM,串行接口包括UART、SPI、2个I2C、用于下载/调试的JTAG端口、4个定时器、14个通用I/0引脚、片内可编程逻辑阵列(PLA)。CPU时钟高达45 MHz,可使用片内晶体振荡器和片内PLL。

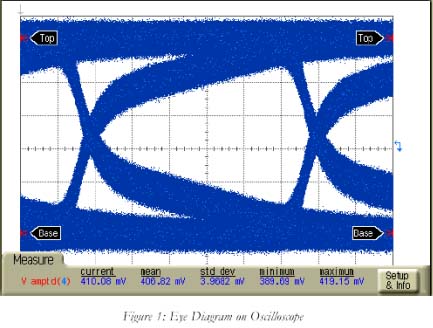

Si5040是Silicon Laboratories公司高速物理层(highspeed PHY)产品线的产品。采用其已通过市场验证的DSPLL技术,同时在数据发送和接收路径提供信号抖动消除功能的10 Gb/s XFP收发器。Si5040支持3种不同的模拟与数字信号质量监测功能,分别是模拟信号LOS监测、CID(连O或连1)监测以及专有的数字眼图开度测量功能,还提供线路环回测试、XFI回路测试和接收/发送双方向的PRBS码流生成和检查功能。

此设计中,ADμC7020作为控制器,对Si5040芯片进行配置和初始化,完成误码数的采集,并作为整个系统上位机和Si5040之间的桥梁,及时向上位机提供测量的误码及状态值等数据;Si5040完成伪随机码型(PRBS)的产生、同步及对比检测,计算出误码数(Error Count);上位机由LabWindows/CVI构造的测试平台,通过上位机PC的并口(LPT)模拟I2C总线读ADμC7020所构建的寄存器映射表,将测试系统各器件的状态(包括Si5040)及误码数显示出来,计算误码数和测试时间内的总发送码数的比值得出误码率(BER),通过I2C总线读写ADμC7020的寄存器表完成对系统各部分(包括Si5040)的控制和查询。

2 原理及组成

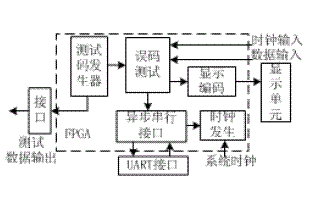

误码测试仪框图如图1所示。

2.1 测试原理

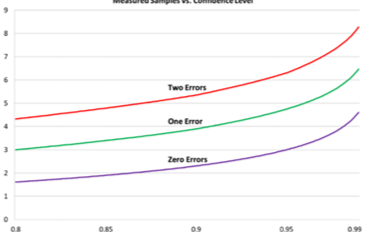

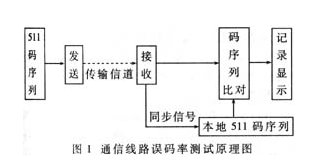

在数字光纤通信系统中,经常测试或验证系统和器件的误码率指标,若要获得精确的测试结果,必须进行无限长时间的试验。根据统计置信度原理,只要验证数字系统或器件的误码率指标是否优于某一规定标准,即可在测量精度和测试时间之间进行折中处理,而且仍能保证测试结果的可信度。产生误码的主要原因是传输系统的噪声和脉冲抖动,误码性能用误比特率BER来衡量。但在实际测量中,常以长时间测量中误码数目与传送的总码元数之比来表示BER,BER=错误比特数/传输总的比特数。

由于这是一个统计过程,因此当被测比特数接近于无穷大时,被测BER才能接近实际BER。但是在大多数情况下,只需测试小于预定义阈值的BER即可。完成测试所需的比特数取决于所需的置信度和BER阈值。置信度是指,系统的真实BER小于指定BER时的测试占全部测试的百分比。由于无法测量无穷位,也无法准确预测什么时候会出现误码,因此置信度永远不会达到100%。另外,IEEE802.3规定最坏情况的误码率是10E-10。在这种条件下,出现的误码不会降低网络的性能,因为所有的网络软硬件都按这个要求建立。因此,这个条件下出现的噪声将不足以改变接收端的比特值,不会造成误码。一般情况下,选择的误码率标准比IEEE标准高出100倍,并把10E-12误码率称为零误码率。零误码率意味着每10万亿位中产生的误码小于1个。置信度的公式如下:

其中CL为置信度,Nbits为接收的总比特数。

在生产和测试中,只考虑零误码且置信度为标准的95%的情况,用比特数除以数据速率可确定测试所需时间。得出常用的方程式如下:

对于10 Gbps的系统,测试30 s基本可以达到10E-12的要求。

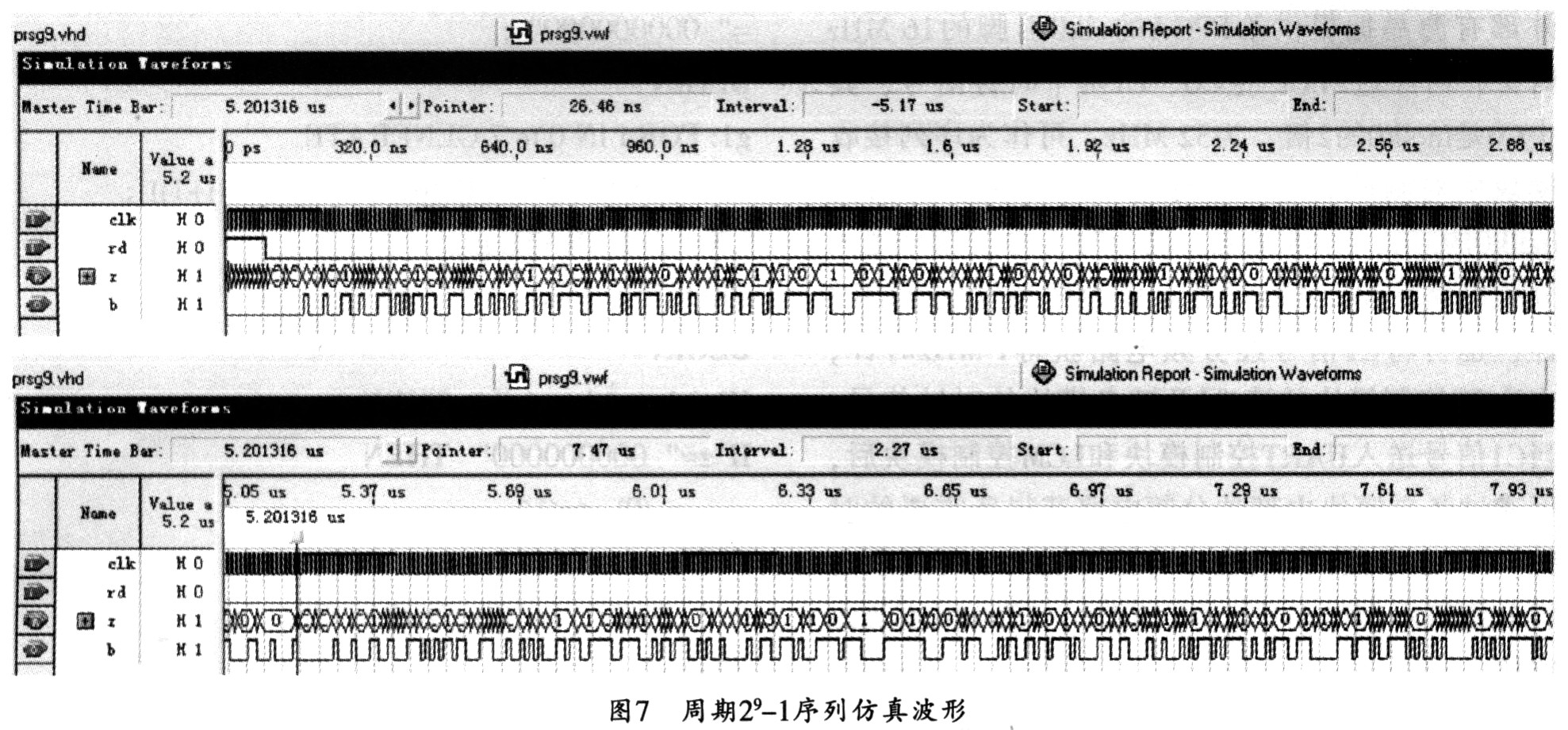

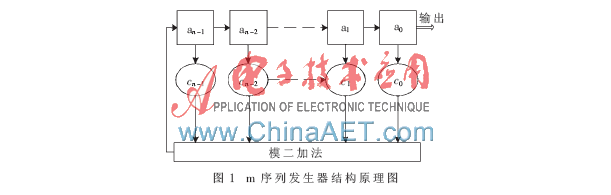

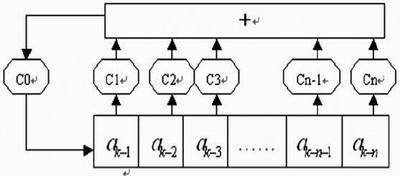

Si5040的发端模块产生伪随机码序列数据流,作为通信系统的信源数据流,收端模块接收通信系统输出的比特流,并与本地产生的与发端形式相同的伪随机码比特流相比较,如比较结果不同即系统有误码。Si5040在收端和发端信道上都有可编程的模式生成器和检查器。发端信道通过配置寄存器(tpSel Register 157),收端信道通过配置寄存器(RxtpSel Register 29),可以生成PRBS7、PRBS31或者64位用户自定义码型。模式检查器还提供了不同步信号(Loss-of-Sync)检查。在同步情况下,测试中发端的误码值结果存于Si5040中40位的寄存器组(tp-ChkErrCnt registerl76-180)和一个8位浮点数的寄存器(tpChkErr register 181)。收端的误码值结果存于40位寄存器组(RxtpChkErrCntRe-gister48-52)或8位浮点数据类型的寄存器(RxtpChkErr Register 53)。本设计仅使用Si5040的发端信号的模式生成器和检查器功能。

2.2 硬件设计

本文硬件设计仅列出Si5040和ADμC7020两部分的原理图。

2.2.1 Si5040

Si5040的PINl3和PINl4是参考时钟输入引脚。在此设计应用中使用Silicon Laboratories公司的SI534四频晶体振荡器(XO),其工作频率范围10 MHz~1.4 GHz,RMS抖动低于O.3 ps,可提供高线性度的控制电压及宽范围的电压增益选择,并可以支持PECL、LVDS、CMOS和CML各种电平形式的输出。

Si5040的通信接口支持I2C和类SPI模式。通过SPSEL(PIN9)来选择使用接口的类型。当SPSEL置低电平时,使用I2C接口类型,PIN25(ser-ial data line,SD)and PIN24(serial clock input,SCK)作为I2C总线的SDA和SCL。当SPSEL置高电平时,使用类SPI接口类型。

Si5040在发端和收端都有可编程的码型模式生成器和检查器。发端信道使用TxtpSel寄存器,可配置成PRBS7、PRBS31或者64位用户自定义码型。

Interrupt、RX_LOL和Rx_LOS反映Si5040的工作状态。由ADμC7020的I/O口来采样其电平逻辑,由此反映Si5040的工作状态。

TD+、TD-、TXDOUT+、TXDOUT-和RD+、RD-、RXDIN+、RXDIN-接入SMA头,信号为差分CML信号。

Si5040原理图如图2所示。

2.2.2 ADμC7020

使用JTAG仿真调试ADμC7020,其引脚为TMS、TDI、TCK、TD0、TRST。

使用ADμC7020的两个I2C接口。P1.1和P1.2构成I2C总线O,ADμC7020作为I2C从机。上位机PC作为I2C主机。P1.3和P1.4构成I2总线1,ADμC7020作为I2C主机,Si5040作为I2C从机。

P0.6、P0.4和P0.5引脚作为输入脚测试Si5040的状态RX LOS、RX LOK和Interrupt。

P1.4、P1.5、P1.6、P1.7和P4.2引脚控制测试待测XFP模块的各种状态。

ADC0、ADC1和ADC2测量误码测试系统中有关电压值+5 V、+3.3 V和+1.8 V的各电压通道上的总电流值。

ADC3、ADC4和ADC12测量误码测试系统中XFP模块的电压值+5 V、+3.3 V和+1.8 V。

跳线接地时即P0.0接地,同时Flash 0x14地址的内容为0xFFFFFFFF时,在两个条件同时满足时,在ADμC7020复位时可自动进入Bootlo-ader程序(即在系统中编程ISP),这样可以不使用JTAG仿真器,以方便误码测试仪的ADμC7020的Firmware在线升级换代。

ADμC7020部分原理图如图3所示。

3 FIRMWARE设计

①当ADμC7020作为I2C从机时,构建一个I2C访问的寄存器映射表(Memory Map)。共有2个页面,每个页面256个寄存器。其中页面0有待测XFP模块和Si5040的状态显示、控制、上电初始化值、仪器接口初始化等寄存器。页面1为Si5040的映射寄存器,其将Si5040内部全部的184个寄存器全部映射到本页,测试人员可以通过该页的寄存器对应访问Si5040的相关寄存器,每个页面的最后一个寄存器是页面选择寄存器。

②收到上位机命令,解释上位机命令并完成测试或控制待测模块和Si5040功能。

③设置Si5040循环控制定时器值为100 ms,即每100 ms检测待测模块的状态和Si5040的寄存器值,并映射到构建的相关寄存器中。

④设置ADC采样TIMER也为100 ms,即每100 ms通过ADC采样测量相应的电压值和电流值。并将值映射到构建的相关寄存器中,供上位机查询。

⑤上电初始化Si5040相关测试误码寄存器。在上电复位时,ADμC7020按照其寄存器映射表的初始值配置Si5040。修改初始配置表可以改变Si5040的上电寄存器设置。在上电初始化完成后,通过I2C接口修改Tablel的Si5040映射寄存器值,也可以改变Si5040的相关寄存器的配置。

4 上位机及人机界面

4.1 人机界面

Lab Windows/CVI所设计的人机界面如图4所示,左部为误码率测试,右部为寄存器状态及控制。在测试前,通过串口读光功率计和衰减器的值,根据生产和测试要求配置衰减器衰减量,在完成整个测试平台的配置并选择测试时的伪随机码列后,按下“开始”按键,可以开始测试。在Elapsed Time(s)、Error Count和BER三个显示框中分别显示测试时间、误码个数及误码率。“信号发生器”按键为使用Si5040配置TX信道的端口信号,不读Si5040的误码个数,不计算RFR值。

4.2 底层驱动

控制上位机PC的并口,按I2C协议产生相应的I2C读写时序。上位机PC的并口DB25由3个寄存器组成:数据寄存器(Data Register)、状态寄存器(Status Register)和控制寄存器(Control Register),在SPP(Standard Parallel Port)模式,即标准并口模式下,地址为:数据寄存器(0x378)、状态寄存器(0x379)、控制寄存器(0x37a)。通过数据寄存器的数据输出和状态寄存器数据的读入,控制SCL和SDA总线以及读SCL和SDA的状态,可以方便地产生I2C时序中的START、STOP、ACK、NACK等基本的时序,通过这些基本时序生成了完整的I2C读写的时序。

5 实验

在码型中可选择PRBS7、PRBS31或64位用户自定义码型,针对XFP光模块一般选择PRBS31码型,置信度为95%,短时间测量采用30 s,长时间测量采用3000 s。对比实验采用Agilent 86100 Infinite DAC和Agilent70843B 12 Gb/s误码测试仪搭建的误码测试系统。结果显示,在测量时间内两系统测试的误码个数相近,而且误码率测试结果达到10E-12。

结语

本系统充分利用了ADμC7020强大功能及Si5040的误码检测功能,结合虚拟仪器特点,构造了一种误码测试系统。对于大多数光收发模块生产厂家,其对XFP模块生产及测试线有一定的量及周期要求,本系统以其体积小、系统搭建简便、灵活性强、成本低的特点,可以代替部分国内外高速误码测试仪。与进口误码测试仪的对比测量,充分证明了这点。另外,本测试系统可利用ADμC7020的强大Bootloader程序,完成Firmware升级,实现在系统编程,同时整套系统硬件稍加以改进就可以应用于XFP模块的灵敏度测试。

电子发烧友App

电子发烧友App

评论