凌力尔特公司 (Linear Technology Corporation) 推出超低抖动 1.8GHz 时钟分配芯片系列 LTC6954,该器件有 3 个独立的输出,每个都有自己的分频器和相位延迟

2015-11-24 09:55:58 3006

3006 SYSREF分频器SYSREF时钟的25ps步进模拟延迟设备时钟和SYSREF的数字延迟和动态数字延迟PLL1的保持模式PLL1或PLL2的0延迟环境温度范围:–55°C至125°CLMK5C33216LMK04816LMK04808LMK04832-SPLMK04906LMK04001LMK05318BLMK04100LMK04002LMK5B12204LMK04101LMK04010LMK05318LMK04111CDCM7005-SPLMK04832LMK04131LMK04000LMK05028LMK04133LMK04011LMK04228LMK04102LMK04031LMK04828-EPLMK04110LMK04033LMK04616LMK04803CDCM7005LMK04821LMK04805LMK04610LMK04826LMK04806CDCE813-Q1LMK04828LMK04208深圳市立年电子科技有限公司QQ330538935***`

2021-03-24 16:13:02

产品概述NKP8233D、NKP8233F 系列是单通道触摸检测芯片。该芯片内置 LDO 稳压电路单元模块,提供稳定电压给芯片触摸单元块使用。芯片内部集成高效完善的触摸检测算法,使得芯片具有稳定

2021-04-27 11:08:44

噪声抑制和出色的电源抑制比 (PSRR) 来帮助改进无错数据传输。图2显示的是使用LMK03328时对PSRR和TX眼图性能的改进,其原因就在于LMK03328集成了一个LDO。图2:SAW示波器和TI LMK03328时钟发生器的PSRR请在下方给我们留言,告诉我们你在正在研究的、最能从超低抖动中受益的应用。

2018-09-05 16:07:30

AR8031网络应该怎么调试

2022-01-13 06:28:42

什么是BAW技术?BAW谐振器技术的优势TI 突破性BAW技术芯片无外置石英晶振的无线MCU——CC2652RB网络同步器时钟——LMK05318

2021-01-25 06:59:25

的尺寸大小为2.00mm x 2.00mm x 0.40mm,实物如图1所示,引脚配置如图2所示。BD9D322QWZ和BD9D323QWZ单通道同步降压DC/DC转换器的典型应用电路如图3所示,主要

2019-04-22 06:20:03

CC2652RB无线MCU的主要特性和优势是什么?LMK05318网络同步器时钟的主要特性和优势是什么?

2021-07-21 08:40:06

,因而当它们之间进行节目交换或是要采用统一的时钟时必须使用同步器,DAY-1000就是为了适应这种需要研制出来的同步器。用户可以输入4种各种采样频率的AES/EBU数字信号。根据需要选择32KHZ

2011-03-03 00:23:57

NAT-PT实现互连原理是什么?NAT-PT的工作机制是怎样的?IPv4网络和IPv6网络互连技术对比分析哪个好?

2021-05-26 07:07:06

的时钟规范,以及利用TI 公司的芯片实现其时序要求。1. JESD204B 介绍1.1 JESD204B 规范及其优势 JESD204 是基于SerDes 的串行接口标准,主要用于数模转换器和逻辑器件

2019-06-19 05:00:06

在上篇文章《STM32网络之SMI接口》中,我们介绍了STM32网络控制器的SMI接口,SMI接口主要是用于和外部PHY芯片通信,配置PHY寄存器用的。真正网络通信的数据流并不是通过SMI接口

2021-08-05 07:01:43

之前的推文已经将STM32网络的三大件讲完了①PHY接口,《STM32网络电路设计》②MAC控制器,《STM32网络之MAC控制器》③DMA控制器,《STM32网络之DMA控制器》本文将聚焦

2021-08-02 09:54:55

STM32之如何使用野火w5500网络模块

2021-10-13 09:06:03

申请理由:熟悉AT91SAM9261评估套件以及WinCE6.0系统的特性,实现RS485网络配置功能以及各个网络终端参数设置。项目描述:利用AT91SAM9261评估套件以及WinCE6.0系统连接RS485网络终端,设计显示界面并配置RS485终端参数。

2016-05-05 10:39:23

倍频来产生用于以太网,10G光纤通道,和其他网络应用工作的高频率的时钟输出。Maxim专有的PLL设计具有超低抖动和优异的电源噪声抑制,最大限度地减少对网络设备的设计风险。该MAX3625B有三个LVPECL输出。可选择的输出分频器和反馈分频器允许范围的输出频率。

2021-05-18 07:39:05

,是 LMK00338 的另一大重要优势。以上分析表明,只要 RefClk 生成器符合抖动要求,就可以放心大胆地在通用 RefClk 系统中使用超低附加抖动时钟缓冲器。此外,LMK00338 的通用输入级不仅可接收任何

2018-09-17 16:12:25

SI5348-D-EVB,评估板用于评估用于SyncE / 1588和Stratum 3 / 3E应用的Si5348网络同步器时钟。 Si5348在一个IC中包含三个独立的DSPLL,每个DSPLL

2019-02-25 09:56:55

本文针对全方位的信号路径系统中的高速全差分运放及高频宽14位模拟/数字转换器的随机及固定时钟抖动,具体分析、研究了超低噪声兼时钟抖动滤除技术。研究选用双级联PLLatinum架构,配置高性能压控振荡器(VCXO),很好地实现了降噪和时钟抖动滤除的作用。

2019-07-05 07:47:46

同步器就是键鼠同步器控制器,用于一套键盘鼠标显示器同时同步操作多台电脑主机(通常是4口8口16口或级联更多),主要应用于游戏领域。键鼠同步器这种产品一直被游戏厂家打压,因为这样会干扰游戏的公平性

2022-10-10 09:41:23

RS-232串口与RJ45网络接口转换器是由哪些部分组成的?如何去设计RS-232串口与RJ45网络接口转换器?

2021-05-14 07:26:44

LMK04800的主要特性LMK04800的应用

2021-04-07 06:59:35

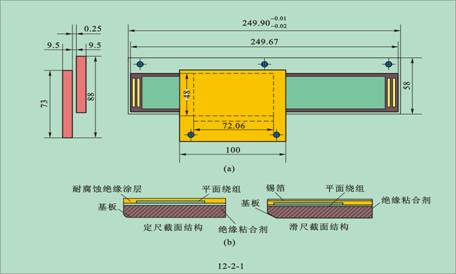

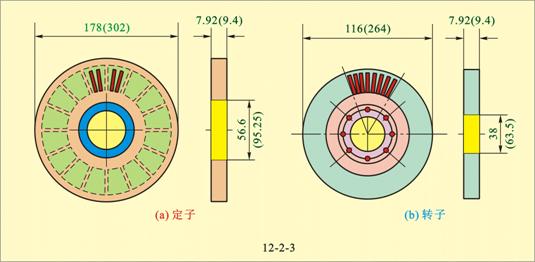

感应同步器是利用两个平面形绕组的互感随位置不同而变化的原理组成的。可用来测量直线或转角位移。测量直线位移的称长感应同步器,测量转角位移的称圆感应同步器。长感应同步器由定尺和滑尺组成。圆感应同步器

2018-10-30 16:10:20

迈拓维矩键盘鼠标同步器,可以实现将一套键鼠的信息同时发给多台电脑,适用于游戏,教学,测试等领域。由于采用了绝对同步技术,鼠标在多台电脑画面完全一致,这一特点,在游戏领域非常重要。迈拓维矩游戏同步器

2018-02-25 09:00:42

AR8031网络应该怎么调试

2022-01-11 07:28:40

各位大侠: 想请教个问题,使用两片AD2S1210能否实现双通道感应同步器的位置采样转换,需要怎样连接,如不能实现,还有其他方法实现双通道采样的问题。

2018-10-29 09:20:02

怎样去设计时间同步器的硬件电路?怎样去设计时间同步器的软件电路?

2021-05-21 06:22:30

寻求c6748网络例程,希望能ping ip的,谢谢。y

2019-04-24 07:03:41

多通道 JESD204B 时钟,采用 TI LMK04828 时钟抖动清除器和带有集成式 VCO 的 LMX2594 宽带 PLL,能够实现低于 10ps 的时钟间偏斜。此设计经过 TI

2018-12-28 11:54:19

耐辐射且符合 JESD204C 标准的 30krad 超低噪声 3.2GHz、15 路输出时钟抖动清除器 Function Dual-loop PLL, Ultra-low jitter

2022-12-02 13:47:46

具有集成式 2.5GHz 体声波 VCO 的 14 路输出、三个 DPLL 和 APLL 网络同步器 Function Clock network synthesizer Number

2022-12-02 13:47:46

具有集成式 2.5GHz 体声波 VCO、16 路输出、三个 DPLL 和 APLL 的网络同步器 Function Clock network synchronizer Number

2022-12-02 13:47:47

适用于通过 BAW 进行无线通信且采用 JESD204B 的超低抖动时钟同步器 Function Clock network synchronizer Number

2022-12-02 13:47:47

耐辐射加固保障 (RHA)、超低噪声、3.2GHz、15 路输出时钟抖动清除器 Function Dual-loop PLL, Single-loop PLL, Ultra-low

2022-12-02 13:47:48

采用 BAW 技术的超低抖动、单通道网络同步器时钟 Function Clock network synchronizer Number of outputs 8 RMS

2022-12-02 13:47:48

采用网络同步和 BAW 技术的超低抖动时钟发生器 Function Clock network synchronizer, Ultra-low jitter clock generator

2022-12-02 13:47:49

采用 BAW 技术的超低抖动、单通道网络同步器时钟 Function Clock network synchronizer Number of outputs 8 RMS

2022-12-02 13:47:49

具有双环路且符合 JESD204B 标准的超低噪声 3.2GHz、15 路输出时钟抖动清除器 Function Dual-loop PLL Number of outputs 15

2022-12-02 13:47:50

低抖动双通道网络同步器时钟 Function Clock network synchronizer Number of outputs 8 RMS jitter (fs

2022-12-02 13:47:50

具有双环 PLL 的超低噪声时钟抖动消除器 Function Dual-loop PLL Number of outputs 15 RMS jitter (fs) 156

2022-12-02 13:47:51

温度范围为 -55°C 至 105°C 且符合 JESD204B 标准的超低噪声时钟抖动消除器 Function Dual-loop PLL Number of outputs

2022-12-02 13:47:51

符合 JESD204B 标准的超低噪声和低功耗时钟抖动消除器 Function Dual-loop PLL Number of outputs 16 RMS jitter

2022-12-02 13:47:52

具有双 PLL 且符合 JESD204B 标准的超低噪声和低功耗时钟抖动消除器 Function Dual-loop PLL Number of outputs 10 RMS

2022-12-02 13:47:52

具有 6 个可编程输出的超低噪声时钟抖动消除器 Function Dual-loop PLL Number of outputs 7 RMS jitter (fs

2022-12-02 13:47:54

支持 JESD204B 的超低抖动合成器和抖动消除器 Function Dual-loop PLL Number of outputs 15 RMS jitter (fs

2022-12-02 13:47:54

具有集成式 1840 至 1970MHz VCO0 且符合 JESD204B 标准的超低噪声时钟抖动消除器 Function Dual-loop PLL Number

2022-12-02 13:47:54

具有集成式 2370 至 2630MHz VCO0 且符合 JESD204B 标准的超低噪声时钟抖动消除器 Function Dual-loop PLL Number

2022-12-02 13:47:55

带 6 路可编程输出的超低噪声时钟抖动消除器/倍频器 Function Dual-loop PLL Number of outputs 7 RMS jitter (fs

2022-12-02 13:47:56

具有级联 PLL 的精密时钟调节器时钟抖动消除器 Function Cascaded PLLs Number of outputs 7 RMS jitter (fs

2022-12-02 13:47:56

具有双级联 PLL 和集成式 1.9GHz VCO 的低噪声时钟抖动消除器 Function Cascaded PLLs Number of outputs 14 RMS

2022-12-02 13:48:00

具有双级联 PLL 和集成式 2.2GHz VCO 的低噪声时钟抖动消除器 Function Cascaded PLLs Number of outputs 14 RMS

2022-12-02 13:48:00

耐辐射加固保障 (RHA) 3.3V 高性能时钟抖动清除器和同步器 Function Single-loop PLL Number of outputs 5 Output

2022-12-02 13:48:03

具有级联 PLL 的精密时钟调节器低噪声时钟抖动消除器 Function Cascaded PLLs Number of outputs 7 RMS jitter (fs

2022-12-02 13:48:04

高性能、低相位噪声、低偏移的时钟同步器(使参考时钟与 VCXO 同步) Function Single-loop PLL Number of outputs 5 Output

2022-12-02 13:48:05

该应用笔记提出了超低抖动时钟合成器的一种设计思路,其目标是产生2GHz时钟时,边沿之间的抖动< 100fs。分析和仿真结果表明,要达到这一抖动指标,设计难度远远高于预期。关

2009-04-21 23:14:05 723

723

摘要:该应用笔记提出了超低抖动时钟合成器的一种设计思路,其目标是产生2GHz时钟时,边沿之间的抖动< 100fs。分析和仿真结果表明,要达到这一抖动指标,设计难度远远高于预

2009-04-22 09:35:13 296

296

摘要:该应用笔记提出了超低抖动时钟合成器的一种设计思路,其目标是产生2GHz时钟时,边沿之间的抖动< 100fs。分析和仿真结果表明,要达到这一抖动指标,设计难度远远高于预

2009-04-25 09:54:26 482

482

摘要:该应用笔记提出了超低抖动时钟合成器的一种设计思路,其目标是产生2GHz时钟时,边沿之间的抖动< 100fs。分析和仿真结果表明,要达到这一抖动指标,设计难度远远高于预

2009-05-08 10:19:03 431

431

摘要:介绍了迟早门同步器的基本工作原理,提出了在迟早门同步器中引入模糊逻辑控制获得较小相位抖动的方法,给出了迟早门同步器在FPGA上的

2009-06-20 13:44:46 712

712

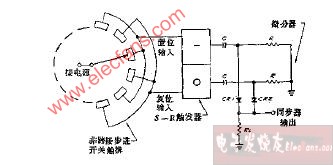

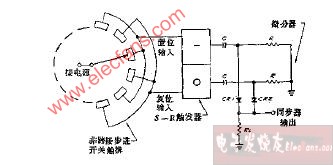

同步开关同步器电路图

2009-07-03 14:31:45 1893

1893

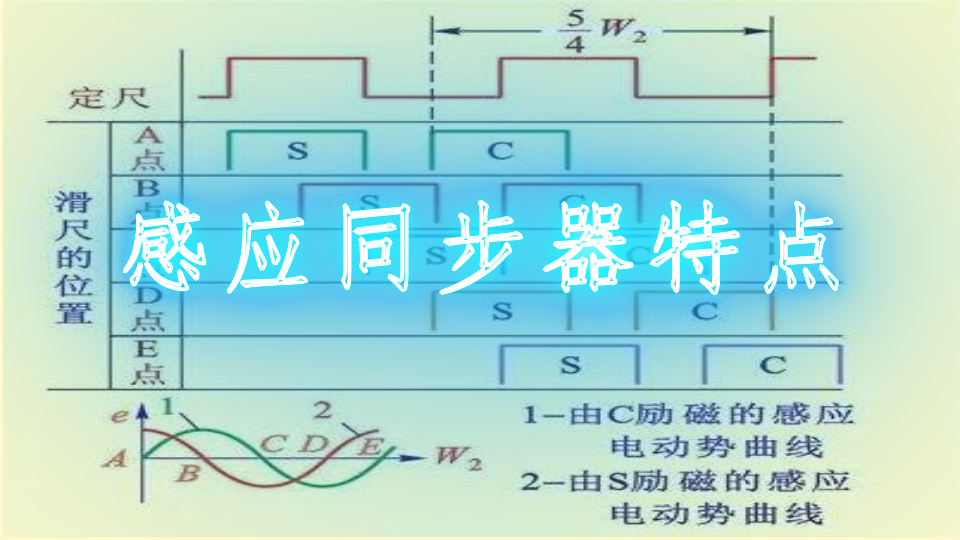

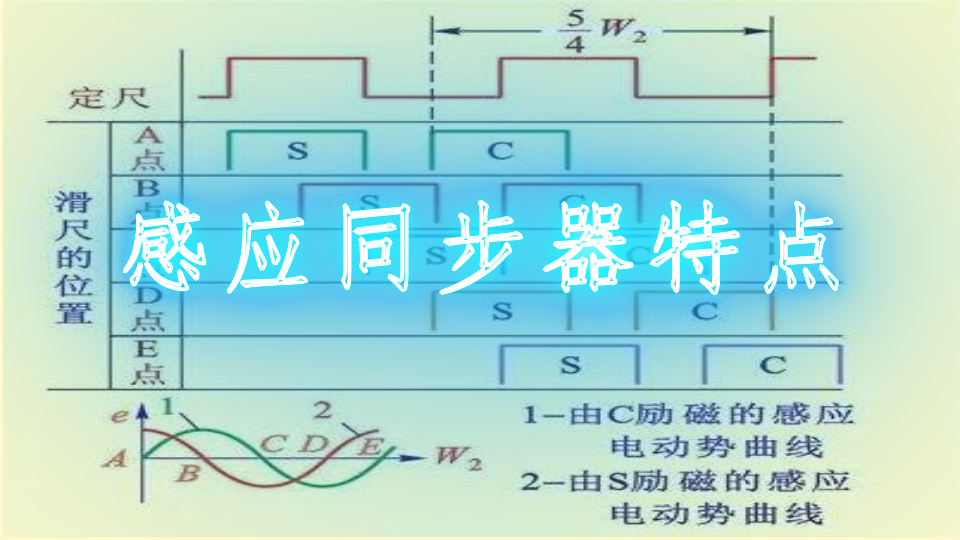

感应同步器

感应同步器由两个平面印刷电路绕组构成,类似于变压器的初、次级绕组,故又称平面变压器。感应同步器通过位移

2009-10-29 22:45:40 2416

2416

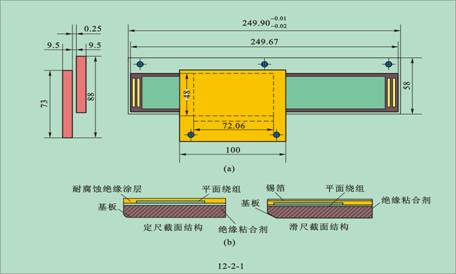

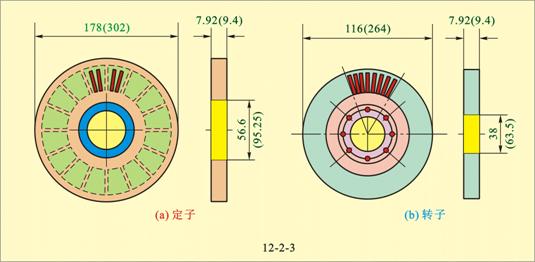

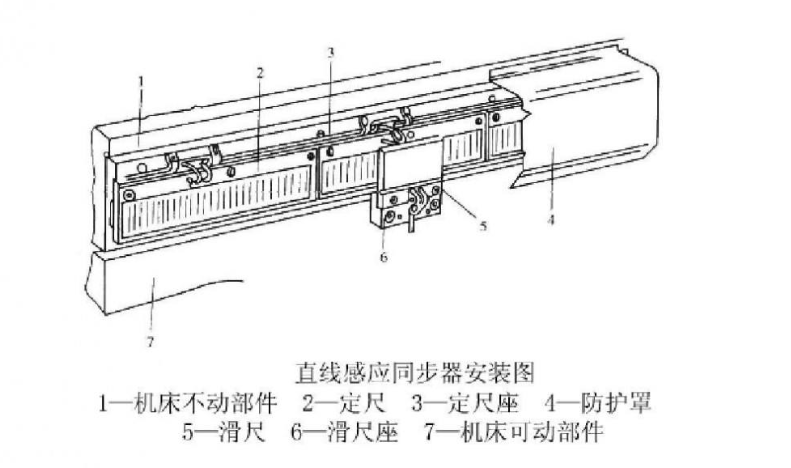

感应同步器的基本结构

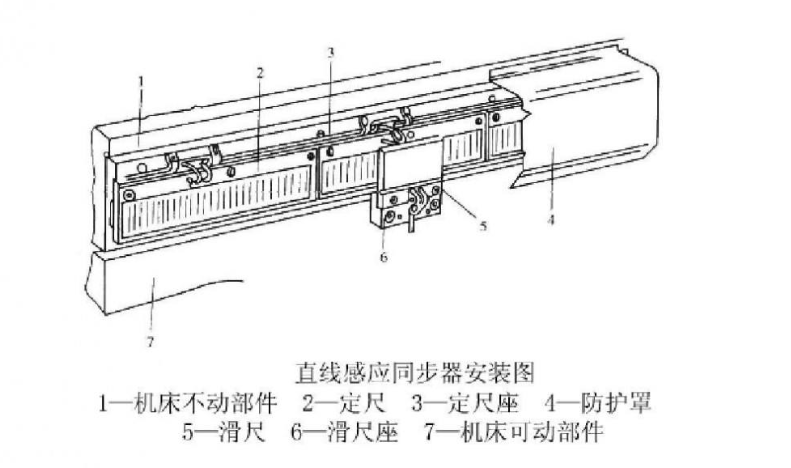

1.直线式感应同步器 直线式感应同步器的结构如图12.2.1所示,它由定尺和滑尺两部分组成,长尺为定尺,短尺为滑尺。感应同步器的

2009-10-29 22:46:10 4269

4269

感应同步器的工作原理

直线式感应同步器和圆盘式感应同步器的工作原理基本相同,都是利用电磁感应原理工作。下面以直线式感应同步器为例介绍其工作原理。

2009-10-29 22:47:49 8281

8281

感应同步器的信号处理

感应同步器有两种激励方式:一种是滑尺(或定子)激磁,从定尺(或转子)绕组取出感应电势;另一种是定尺(或转子)

2009-10-29 22:49:18 4218

4218

感应同步器的应用

感应同步器具有以下特点:(1)感应同步器基于电磁感应原理,感应电势仅取决于磁通量的变化率,几乎不受环境因素如温度、油污、尘埃等的

2009-10-29 22:49:54 3323

3323

光同步线路的抖动特性和分类有哪些?

抖动的影响 定时抖动(简称抖动)定义为数字信号的特定时刻相对其理想参考时间位置的时间

2010-03-19 17:11:58 969

969 单通道超低功耗运放IC SGM8041

圣邦微电子(SGMICRO)最新推出的SGM8041单通道超低功耗运算放大器,静态电流710nA,最大失调电压2.5mV,

2010-05-18 09:23:50 6005

6005

基于FPGA的帧同步器的设计与仿真。。。。

2016-01-04 15:31:55 25

25 系列增添三款新器件,包括两款单通道超低抖动网络同步器产品ZL30721 和 ZL30722 ,以及双通道产品ZL30723 。

2016-02-29 09:39:45 827

827 作为一种高性能、低成本的线卡时钟解决方案,LMK04800 可以实现传统的 SDH/SONET 系统时钟和分组交换网络中的同步以太网时钟频率的灵活转换,同时提供 150fs 级别的低抖动性能,满足

2017-11-28 16:57:56 5

5 该应用报告提出了在TI仪器上的CDCE72010抖动清理器和同步器PLL器件上获取的相位噪声数据。CDCE72010的相位噪声性能取决于基准时钟、VCXO时钟和CDCE72010本身的相位噪声。该应用报告显示了几个最流行的CDMA频率的相位噪声性能。此数据有助于用户为特定应用选择正确的时钟解决方案。

2018-05-15 10:58:53 7

7 LMK0033x是德州仪器(TI)推出的业界最低抖动的PCIe时钟扇形缓冲器。现在就让德仪的工程师向你介绍它的具体情况吧!

2018-06-13 11:52:00 4883

4883 本视频主要介绍了同步器的作用,为了简化操作,并避免齿间冲击,可以在换档装置中设置同步器。惯性式同步器是依靠摩擦作用实现同步的,在其上面设有专设机构保证接合套与待接合的花键齿圈在达到同步之前不可能接触,从而避免了齿间冲击。

2018-10-21 09:57:38 9729

9729 感应同步器是一种电磁式位置检测元件,本视频首先介绍了感应同步器特点,其次介绍了感应同步器的结构特点,最后介绍了感应同步器的优点。

2018-10-21 10:28:39 7238

7238

最新可定制化和提高系统性能产品LMK61XX超低抖动振荡器

2020-05-29 09:10:00 1889

1889 电子发烧友网为你提供TI(TI)LMK04826相关产品参数、数据手册,更有LMK04826的引脚图、接线图、封装手册、中文资料、英文资料,LMK04826真值表,LMK04826管脚等资料,希望可以帮助到广大的电子工程师们。

2019-04-18 22:48:10

电子发烧友网为你提供TI(TI)LMK04828相关产品参数、数据手册,更有LMK04828的引脚图、接线图、封装手册、中文资料、英文资料,LMK04828真值表,LMK04828管脚等资料,希望可以帮助到广大的电子工程师们。

2019-04-18 22:48:10

专注于引入新品并提供海量库存的电子元器件分销商贸泽电子(Mouser Electronics)即日起备货Texas Instruments(TI)的LMK05318网络同步时钟。这款超低抖动单通道

2019-06-20 11:37:03 3458

3458 TI推出超低抖动时钟发生器,以实现更可靠的电信基础设施设备,设计人员可以优化系统性能,简化设备配置并减少设计周期时间。

2019-08-09 15:10:28 1653

1653 本文首先介绍了感应同步器的概念以及感应同步器的工作原理,然后分别从直线感应同步器和旋转感应同步器两种同步器出发介绍了组成,最后介绍了感应同步器的特点。

2019-08-06 15:36:01 9598

9598

在通信或者工业应用中,同步时钟非常重要,它确保了信号的完整性和一致性。

2019-08-07 15:16:24 6479

6479

在感应同步器的运用进程中,除一样会遇到旋改动压器在运用进程中所遇到的角须绑缚在[-π,π]内的疑问或央求以外,直线式感应同步器还常常会遇到有关接长的疑问。例如,当感应同步器用于查看机床作业台的位移

2020-04-19 05:14:00 2779

2779 不同变速箱同步器有多有少,一款变速箱不同挡位同步器也各不相同,那么单锥同步器、双锥同步器、三锥同步器有何区别,同步器是如何工作的,给用户带来什么价值?

2020-05-25 16:19:06 5913

5913 具 PLL 的 5 输出超低抖动时钟分配器提供独特的多芯片输出同步方法

2021-03-19 10:54:50 10

10 AD9546:双DPLL数字化时钟同步器数据表

2021-03-22 20:36:12 7

7 AD9548:四/八路输入网络时钟发生器/同步器数据表

2021-04-16 11:41:04 10

10 超低抖动时钟的产生与分配

2021-04-18 14:13:51 8

8 AD9547:双/四输入网络时钟发生器/同步器数据表

2021-04-30 08:48:14 10

10 AD9543:四路输入、10路输出、双DPLL/IEEE 1588同步器和抖动清除器

2021-05-27 15:35:55 3

3 Other Parts Discussed in Post: LMK05318在分布式网络中,由于网络传输时延的不确定性,导致采用网络命令触发的同步精度差;同时,由于分布式网络各节点位置的分散性

2022-01-15 14:35:31 2389

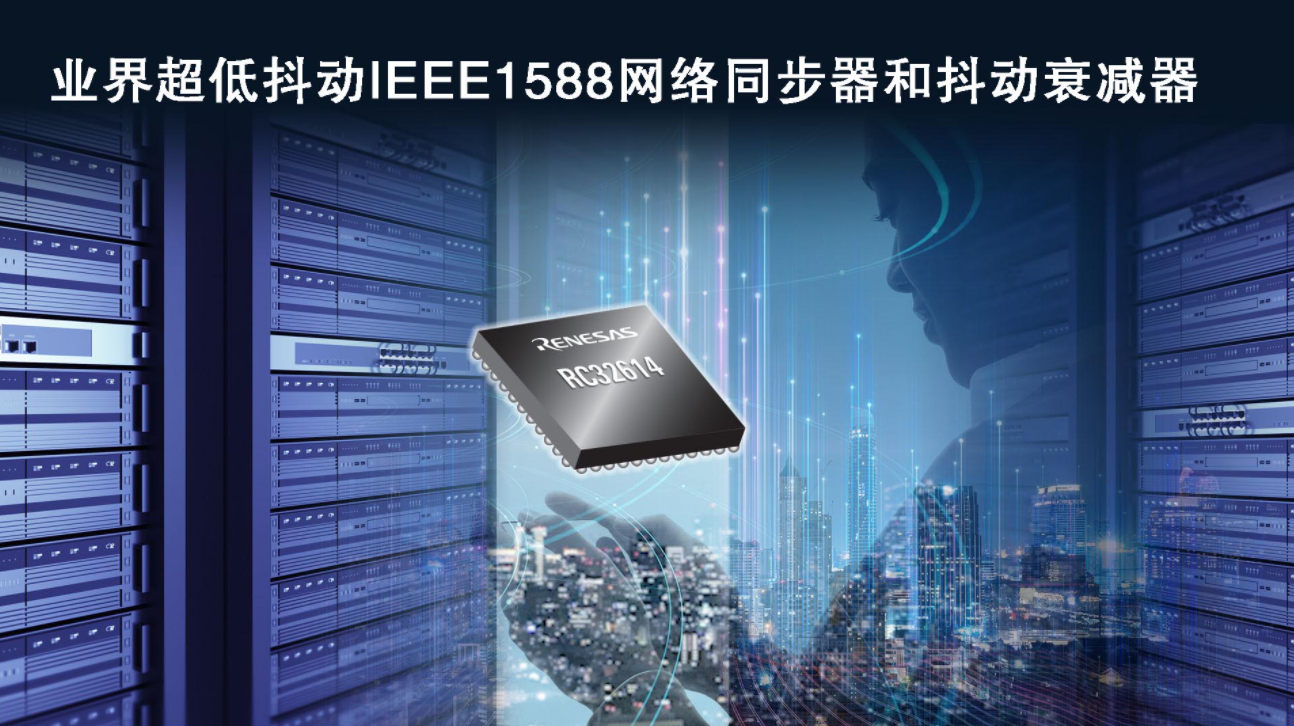

2389 全新ClockMatrix2提供具有超低抖动时钟输出的单芯片网络同步器和抖动衰减器,同时支持所有IEEE1588操作模式。

2021-12-15 16:30:58 877

877

KOYUELEC光与电子提供技术支持,有容微电子GM50101:超低附加抖动时钟缓冲器。

2022-05-07 11:40:15 1070

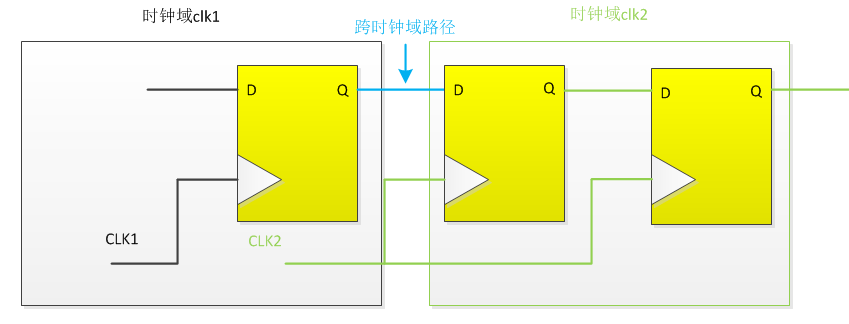

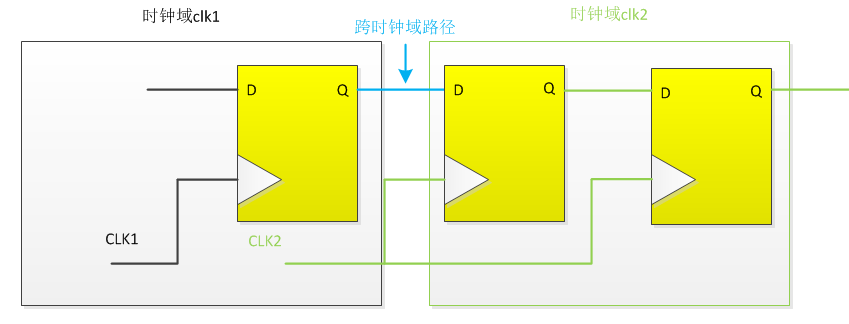

1070 如图1所示电路结构就叫同步器。左边为时钟域clk1,右边两个FF为时钟域clk2,蓝色的为CDC(clock domain cross)路径。这种电路结构常用于两个不同的时钟域数据传输。

2023-06-28 14:09:49 1577

1577

电子发烧友网站提供《毫微微时钟网络同步器、抖动衰减器和时钟发生器RC32112A 数据表.pdf》资料免费下载

2024-01-31 10:09:17 0

0

正在加载...

电子发烧友App

电子发烧友App

评论