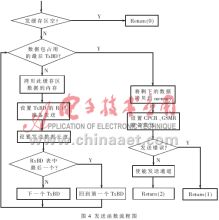

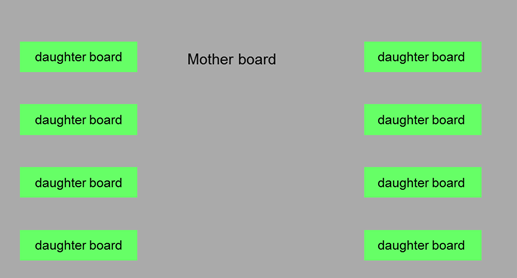

Device)生成各种逻辑电平来控制螺线管和步进电机,所以CPLD被横机客户广泛使用。横机机头板一般由主板和子板,子板通过接插件插在主板上完成最终的控制功能(如图一)。因为每个子板都有控制信号来自母板,所以CPLD需要放置在母板上以便信号合理布局,但有时机头板母板受机械结构的限

2018-03-07 08:53:01 9032

9032

本文描述了复位的定义,分类及不同复位设计的影响,并讨论了针对FPGA和CPLD的内部自复位方案。

2016-07-11 14:33:49 6228

6228

CPLD逻辑电路

2019-10-29 09:10:54

,现有一个逻辑关系不会处理,请各位帮忙(尽量用图形输入法,VHDL看不懂,正在学习中),我看过用触发器去做,但需要CLK信号,这个信号要从CPLDI/O口引入,但板子已做好,该逻辑关系是后加的,所以希望

2012-12-24 22:39:54

最近想做一个液晶屏驱动板,采用CPLD+Sram的方案,性价比高,芯片也不贵,做好驱动板之后,可以用单片机控制驱动板来最终实现控制液晶屏显示,CPLD采用EPM240Sram采用

2019-02-25 20:28:54

抗干扰能力是系统设计的关键。根据汽车制动力测量精度的要求和整个系统的控制逻辑提出了采用单片机和CPLD 双控制器的总体方案,并根据所要实现的功能设计了软件。而滤波和抗干扰是任何智能仪器系统都必须考虑

2009-04-16 13:56:57

我用MAX3491做422接口,CPLD作为422与DSP之间逻辑配置,实现数据收发尽量减少对DSP的占用。这样的话CPLD空间大概要多少?EPM1270资源够用不?

2017-08-28 14:38:22

MPC850 - Communications Controller Hardware Specifications - Motorola, Inc

2022-11-04 17:22:44

我正在为 MPC5744P 编写引导加载程序。当在 APP 中检测到下载请求时,看门狗复位用于从 APP 跳转到引导加载程序。我想将此请求标志保存在 RAM 中。当项目重置时,标志如何保留在 RAM 中?谢谢你!

2023-03-27 09:10:16

5748G 引导加载程序源代码是否集成在项目源代码中?否则如何识别s31 design studio 2.1中的bootloader源代码?以及如何识别应用程序的跳转是在哪个地址实现的?如何实现极简引导加载程序

2023-03-23 08:31:46

FPGA与CPLD(特权同学版权所有)本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》(特权同学版权所有)配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt

2019-02-21 06:19:27

也不会丢失

立即上电 :上电后立即开始运作

可在单芯片上运作

内建高性能硬宏功能

PLL

存储器模块

DSP模块

用最先进的技术实现高集成度,高性能

需要外部配置ROM

应用范围偏向于简单的控制通道应用以及

胶合逻辑偏向于较复杂且高速的控制通道应用以及数据处理集成度小~中规模中~大规模

2011-09-27 09:49:48

的路径。这就是为何CPLD被认为是“逻辑丰富”型的。宏单元以逻辑模块的形式排列(LB),每个逻辑模块由16个宏单元组成。宏单元执行一个AND操作,然后一个OR操作以实现组合逻辑。每个逻辑群有8个逻辑模块

2012-10-26 08:10:36

,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。内部基本结构为门阵列构成静态存储器(SRAM)。该SRAM可构成函数发生器,即查找表(LUT),通过查找表可实现逻辑函数功能

2020-08-28 15:41:47

用“与—或”表达式来描述,所以该“与或阵列”结构能实现大量的组合逻辑功能) 简单的“与或”阵列:(PAL、GAL、CPLD) 含查找表的逻辑单元:(FPGA) CPLD和FPGA的主要

2020-07-16 10:46:21

FPGA与CPLD(特权同学版权所有)本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》(特权同学版权所有)配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt

2015-03-12 13:54:42

大家好...一世我正在使用XC95144xl CPLD从事系统内编程项目。一世想知道JTAG协议如何用于编程CPLD。我的意思是四个信号tck,tdi,tdo和tms如何实现“CPLD编程”。除了

2019-01-15 10:08:00

函数四.总流程五.结果六.后记(含代码链接)一. 简介 RTOS中的多任务切换是操作系统与裸机编程的一个非常大的区别,一般逻辑变成运行在一个循环内,裸机编程很难实现两个事件的并行(这里的并行指的是

2021-12-06 07:08:15

8641, MPC8641D MPC8XX 系列MPC823, MPC823E, MPC850, MPC852T, MPC853T, MPC855T, MPC857DSL,MPC857T, MPC

2010-07-29 10:38:34

verilog实现I2C透传,作为主从机设备之间的传输通道,但是SDA信号在cpld的端口进行输入、输出状态切换的逻辑始终处理不好,有没有大佬能帮忙分析一下!

2022-08-17 11:22:27

,我们可以改变任意地址C1B1A1CBAS2S1S0的值,即完成任意驱动信号的实现,解决了CPLD在横机机头板应用中不方便布板的问题,增加了客户布板的灵活性。欢迎登录进行评论

2017-08-22 10:11:38

Device)生成各种逻辑电平来控制螺线管和步进电机,所以CPLD被横机客户广泛使用。横机机头板一般由主板和子板,子板通过接插件插在主板上完成最终的控制功能(如图一)。因为每个子板都有控制信号来自母板,所以

2022-11-14 06:52:19

专家都是如何使用超低功耗的复杂可编程逻辑器件(CPLD)的?从他们的嵌入式设计中的I/O子系统中学到了什么?

2021-04-08 06:31:20

主板上。图二由此可见通过上述方法,我们可以改变任意地址C1B1A1CBAS2S1S0的值,即完成任意驱动信号的实现,解决了CPLD在横机机头板应用中不方便布板的问题,增加了客户布板的灵活性。欢迎登录进行评论

2019-03-26 06:45:09

可编程逻辑器件FPGA/CPLD结构与应用.ppt

2017-01-21 20:34:49

可编程逻辑阵列fpga和cpld

2023-09-20 07:58:59

以及安排足够的锁存器就能仅通过19根I/O口线在FPGA/CPLD与单片机之间进行各种类型的数据与控制信息交换。(3)相对于非总线方式单片机的编程简捷控制可靠。(4)在FPGA/CPLD中通过逻辑切换

2018-12-10 10:18:34

现在大多数的CPLD(复杂可编程逻辑器件)都采用可减少功耗的工作模式,但当系统未使用时,应完全切断电源以保存电池能量,从而实现很多设计者的终极节能目标。图1描述了如何在一片CPLD 上增加几只

2018-09-26 17:29:24

相关接口)是物理层芯片与物理介质的接口;PCS、PMA和PMD则分别表示实现物理层协议的各子层。在实际应用系统中,这些子层的操作细节将全部由PHY芯片实现,只需对MII和MDI接口进行设计与操作即可。吉

2018-11-30 11:27:55

七大模块组成。FPGA核心调度模块是下位机的核心部分,完成对下位机各个模块间的协调运行与逻辑控制,实现全局时钟管理、TCP/IP协议与串口通信、命令和数据的组帧与解析、通道切换与配置、信号采集与数据处理

2021-07-12 08:30:00

独立的配置空间,可实现即插即用。这些优点使得PCI总线在数据采集、嵌入式系统和测控等领域得到广泛应用。实现PCI总线协议目前主要有专用接口芯片和CPLD实现两种方式。专用接口芯片使用简单方便、工作稳定

2019-05-29 05:00:02

使用方便性和编程的保密性均优于FPGA。 微机保护系统中的数字组合逻辑电路和时序逻辑电路规模均不大,宜采用CPLD芯片实现,有利于微机保护系统的微型化和智能化设计。 微机保护装置控制接口设计 微机保护

2019-04-25 07:00:04

一种可行的方案就是利用CPLD作为沟通单片机与PCI设备间的桥梁,充分利用CPLD中I/O资源丰富,用户可自定制逻辑的优势,来帮助单片机完成与PCI设备间的通信任务。

2021-04-29 06:28:43

本设计利用CPLD进行数字逻辑器件设计,并配合多路精密程控放大,实现了宽输入范围高精度频率测量,频率测量稳定度达10 -7,而且将输入信号的范围进行了有效地拓宽,使这种高精度频率计的应用领域更加广泛。同时,解决了传统分立数字器件测频时存在的问题。

2021-05-14 06:24:24

嗨, 我正在通过App。关于如何连接CRII CPLD中的LED的说明805。该说明提到CPLD可以在LED的情况下吸收电流,即。如果连接的引脚处于逻辑0,那么LED将发光,反之亦然。如果连接的引脚

2019-08-08 06:20:48

直流电动机的PWM控制原理是什么?如何采用CPLD实现数字控制PWM信号?如何利用CPLD技术实现了逻辑和时序的控制?

2021-05-07 06:03:34

本文在对异步串行通信协议进行分析的基础上,根据实际工程的需要,对异步串行通信控制器进行了详细设计,并结合CPLD器件,采用VHDL语言,对设计方案进行了实现和验证,通过最后时序仿真的波形图得出

2021-05-28 06:53:11

我想通过按键实现复位,能不能提示下怎么写外部复位逻辑啊?

2015-01-20 21:37:58

数字系统的设计人员擅长在其印制电路板上用FPGA和CPLD将各种处理器、存储器和标准的功能元件粘合在一起来实现数字设计。除了这些数字功能之外,FPGA和CPLD还可以使用LVDS输入、简单的电阻电容(RC)电路和一些FPGA或CPLD的数字逻辑单元实现共模功能,从而构建模数转换器(ADC)。

2019-08-19 06:15:33

我想做一个纯硬件的电路,实现用自复位的按键,按一下实现高低电平的切换,简单来说就是按一下输出高电平,再按一下输出低电平,虽然用CPU可以很简单的实现,但是因为项目需要硬件来实现,大家有没有什么好的方法,谢谢大家!!!

2019-06-21 14:47:56

依旧是2M,经测试,最多只能例化两次。CPLD型号是EPM570T100C5, 时钟50MHz,异步复位,RTL视图和波形示意图如下所示:

2016-09-01 10:42:44

。MPC8260支持多种DMA实现方式,分别适用于不同数据传输源/目的设备、不同传输数据块大小和存储模式的需要,因此需要根据主控板的系统特点设计出合适的DMA传输接口。1MPC8260的 DMA系统结构图2CPM

2019-05-22 05:00:53

XC9500系列CPLD器件是什么?XC9500系列CPLD器件遥控编程的实现方法有哪些?如何实现CPLD遥控编程?

2021-04-27 07:15:42

如何通过添加一个简单的RC电路至FPGA或CPLD 的LVDS输入来实现模数转换器?请问怎么实现低频率(DC至1K Hz)和高频率(高达50K Hz)ADC?

2021-04-15 06:29:55

嗨,我目前正在使用Artix-7 FPGA和Coolrunner II CPLD。在完成FPGA配置之前,CPLD将在复位时保留电路板上的所有内容。所以,我需要监控那个引脚。我的DONE引脚如下

2020-07-20 10:43:01

在于:① SDRAM中的数据和MPC8260的数据同步比较复杂。② 每次发出请求信号后都要进行总线仲裁,并且在得到总线使用权之后一次只能够传输外设端口大小或者32位的数据,总线利用率低。③ 握手控制逻辑

2019-04-18 07:00:08

为了获得一定的灵活性,嵌入式系统大都设计有可编程逻辑器件CPLD。利用单片机对CPLD进行编程,可以方便地升级、修改和测试已完成的设计。文中给出了它的实现过程。

2009-04-03 10:49:49 22

22 在电动车驱动控制单元的设计中,逻辑处理部分的设计是关系到汽车安全可靠行使的关键环节。本文中采用CPLD 逻辑处理与微处理器管理相结合实现逻辑控制,可以根据不同运行

2009-05-30 08:22:39 8

8 Motorola’s MPC850 broadens the PowerPC™ family portfolio by offering similar integration

2009-06-19 09:32:27 21

21 characteristics, and AC timing speciÞcations for revision A and B of the MPC850.This document contains the following topics:Topic PageS

2009-06-24 11:40:39 34

34 The MPC850 integrated communications microprocessor is a versatile, one-chip integrated

2009-06-24 11:42:15 24

24 在使用Flash 存储数据时,有时需要对其设计读写控制逻辑。本文介绍了用VHDL 语言在CPLD内部编程,实现对Flash 中数据的读取控制的具体方法,并给出

2009-09-04 09:29:36 35

35 摘要:介绍了一种采用CPLD实现嵌入式CPU外围电路的方法,将数据总线、译码单元、分频电路及逻辑电路集成于一片CPLD,大大缩小了印制板的面积并提高了系统可靠性,同时,由于CPLD

2010-05-10 09:23:49 29

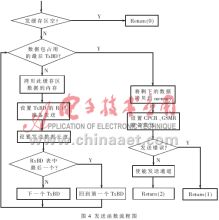

29 阐述了MPC860芯片及其SCC接口的基本工作原理,介绍了在SCC通道上实现HDLC协议的基本设计思想及具体实现,并给出了主要功能函数的设计流程。

2010-07-02 17:01:12 17

17 介绍了基于CPLD的刷卡式电脑联网集控型自动存包系统的设计,并对系统的软硬件构成、CPLD内部逻辑设计、工作原理等进行了详细说明。该系统速度快、安全性好、可靠性高,而且具

2010-07-16 15:11:12 20

20 摩托罗拉MPC8260 微处理器芯片因其强大的通信处理能力和多种协议的支持而被广泛应用于通信和网络领域。本文以MPC8260 为例,探讨在嵌入式系统中实现基于VxWorks 操作系统的快

2010-10-08 16:05:54 32

32 摘 要: 本文采用Altera的CPLD实现了PCI总线至UTOPIA接口的逻辑转换控制,为低成本实现ATM终端奠定了基础。

2006-03-11 13:16:50 864

864

换体DMA高速数据采集电路的CPLD实现

介绍了换体DMA高速数据采集电路原理及其CPLD实现。用CPLD设计双端口RAM缓存、控制译码、时序逻辑电路,很好地解决了电路元件所占体积

2009-03-28 15:09:18 666

666

什么是CPLD

CPLD(Complex Programmable Logic Device)是Complex PLD的简称,一种较PLD为复杂的逻辑元件。CPLD是一种用户根据各自

2009-03-30 13:40:43 3143

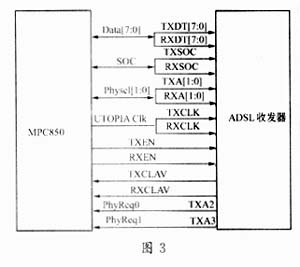

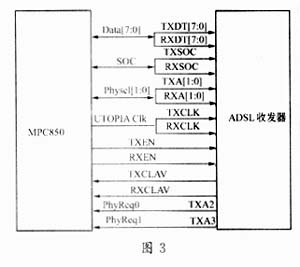

3143 【摘 要】 介绍了基于PowerPC内核的嵌入式通信控制器芯片MPC850,及一种开发MPC850通信功能的硬件平台设计。 关键词:嵌

2009-05-11 19:38:12 1422

1422

摘 要:介绍了一种利用ALTERA公司的复杂可编程逻辑器件(CPLD)快速卷积法实现数字滤波器的设计 关键词:CPLD 数字滤波器 信号处理

2009-06-20 14:23:56 999

999

摘要:介绍了换体DMA高速数据采集电路原理及其CPLD实现。用CPLD设计双端口RAM缓存、控制译码、时序逻辑电路,很好地解决了电路元件所占体积大、电路复杂、不能实现在线

2009-06-20 15:12:07 878

878

CPLD逻辑电路 图6是CPLD内部逻辑电路,CPLD选用的是LATTICE公司的ispLSI1016E,逻辑设计采用原理图输入法,主要功能是对MUX的通道进行选择、对A/D转换器进

2009-11-13 12:04:13 2502

2502

基于MPC860的HDLC通道驱动程序的设计与实现

摘 要: 阐述了MPC860芯片及其SCC接口的基本工作原理,介绍了在SCC通道上实现HDLC协议的基本设计思想及具体实现,并给出了

2010-01-14 10:41:56 903

903

CPLD,CPLD是什么意思

CPLD是指结构比较复杂的可编程逻辑器件,它包括下述输出宏单元结构:

(1)可编程I/O 允

2010-03-26 17:08:50 3081

3081 基于FPGA和CPLD数字逻辑实现ADC技术

数字系统的设计人员擅长在其印制电路板上用FPGA和CPLD将各种处理器、存储器和标准的功能元件粘合在一起来实现

2010-05-25 09:39:10 1309

1309

MPC8260有两个CPU:嵌入的PowerPC内核和通信处理模块(CPM)。由于CPM分担了嵌入式PowerPC核的外围工作任务,这种双处理器体系结构功耗要低于传统的体系结构的处理器。

2011-03-17 11:22:45 3316

3316 提出了以 MPC850 微处理器和FPGA 芯片为核心的非对称数字用户线路技术(AD2SL) 的实现方案,解决了系统的局端和用户端的接入问题. 微处理器MPC850 完成 ADSL 系统的控制和管理,大规模FPGA 芯片

2011-06-08 18:00:49 35

35 用欧姆龙CPM1A型PLC设计出了八路抢答器, 该抢答器集抢答、声音警示、灯光指示和计时功能于一身,易于制作。

2012-02-06 10:56:23 2480

2480

编码输入,带同步功能可接手轮,多个模块组网工作可达120轴,任意两轴直线插补,任意两轴圆弧插补,自带基本逻辑判断能力,指令自动缓存式连续执行,简单的18条指令配合可实现强大的运动控制功能。

2016-03-15 09:58:49 23

23 PC与欧姆龙CPM1A系列PLC的通信协议,感兴趣的小伙伴们可以瞧一瞧。

2016-10-26 15:55:29 28

28 可编程逻辑器件FPGA/CPLD结构与应用

2016-12-11 23:38:39 0

0 在CPLD中用UART逻辑实现高速异步串行通信

2017-01-24 16:54:24 12

12 基于CPLD的SGPIO总线实现及应用

2017-01-24 16:00:51 75

75 本文介绍了PowerPC MPC8260工作在ATM模式的原理,给出了在VxWorks实时操作系统下的END模式的ATM驱动程序设计及实现,实验证实该驱动通过Mux层在IP层与链路层之间建立

2017-11-08 10:25:39 1

1 数字系统的设计人员擅长在其印制电路板上用FPGA和CPLD将各种处理器、存储器和标准的功能元件粘合在一起来实现数字设计。除了这些数字功能之外,FPGA和CPLD还可以使用LVDS输入、简单的电阻电容(RC)电路和一些FPGA或CPLD的数字逻辑单元实现共模功能,从而构建模数转换器(ADC)。

2018-04-26 11:53:00 1121

1121

CPLD通常用于实现前面提到的简单组合逻辑功能,并负责“引导”FPGA以及控制整个电路板的复位和引导顺序。

2018-09-27 11:56:01 6191

6191 本文档的主要内容详细介绍的是如何使用Verilog-HDL做CPLD设计的时序逻辑电路的实现。

2018-12-12 16:25:46 8

8 介绍了一种用CPLD(复杂可编程逻辑器件)作为核心控制电路的测试系统接口,通过时cPLD和竹L电路的比较及cPLD在系统中实现的强大功能,论述了CPLD在测试系统接口中应用的可行性和优越性,简单介绍

2019-01-01 16:18:00 1472

1472

CPLD实现Watchdog 功能,通过对寄存器的操作,实现Watchdog各项功能。CPLD 内部Watchdog 模块逻辑框图如下所示。

2019-06-12 15:59:33 10

10 实现PCI总线协议目前主要有专用接口芯片和CPLD实现两种方式。专用接口芯片使用简单方便、工作稳定可靠,但往往具体应用中只用到部分功能,并且需要可编程逻辑配合使用,这样不仅浪费专用芯片的资源,而且

2020-03-20 09:54:04 1268

1268

可编程逻辑阵列fpga和cpld说明。

2021-03-30 09:30:05 25

25 CPM功能块使用入门免费下载。

2021-05-09 09:58:42 27

27 的,MPC5744P 支持CAN2.0B。CAN 的高层协议,J1939 是基于CAN2.0B的扩展帧,29位标识符,支持单帧和多帧收发通信。本次设计主要实现SAE J1939 数据链路

2021-09-24 16:15:38 7767

7767

电子发烧友网站提供《Compact系列CPLD可配置逻辑模块(CLM)用户指南.pdf》资料免费下载

2022-09-26 10:06:25 2

2 一种使用分立逻辑芯片代替CPLD的解决方案

2022-11-01 08:27:25 0

0 列的 Versal 的产品可支持的 PCIE 最高速率不同,能够支持PCIE5.0协议的产品,例如 VPK120,其 CIPS 内使用的是 CPM5,而只能支持到 PCIE 4.0 协议的产品,例如 VCK190

2023-05-10 09:47:13 890

890

可编程逻辑包括 PAL、GAL、PLD 等。通过不断发展,它已经发展成为现在的CPLD/FPGA。CPLD(复杂可编程逻辑器件)和FPGA(现场可编程门阵列)的功能基本相同,只是实现原理略有不同

2023-07-03 14:33:38 6041

6041

其实这个分频时钟切换很简单,根本不需要额外的切换电路。一个共用的计数器,加一点控制逻辑,就可以了,而且可以实现2到16任意整数分频率之间的无缝切换。

2023-12-14 15:28:56 257

257

正在加载...

电子发烧友App

电子发烧友App

评论