引 言

随着航空事业的发展,空中流量的增加使空中交通管理系统的作用显得非常重要。空管人员利用雷达为已被识别的航空器提供管制服务,可以从雷达屏幕上看到飞机的信息参数。在航管体系中,常规模式及S模式技术用于监视功能,建立在独立编址,选择询问的基础之上,信息交换是通过将上行询问内容和下行应答内容进行脉冲编码实现。编码器是整个雷达的中心,用于产生整机同步信号和询问信号。因此,具有高优良性能询问机编码器脉冲编码信号处理技术至关重要。同时对雷达信号处理的实时性提出了严格的要求,在毫秒级的时间内完成对应答信号的处理,完成目标识别,给出目标飞行器的信息参数;同时在设备体积、功耗方面的严格要求使信号处理设备必须向小型化、智能化、可编程的趋势发展,又要求信号处理系统具有高可靠性和系统升级的需要。

现场可编程逻辑器件及其相关技术是当代微电子技术迅速发展的产物,FPGA是一种多用途、高密度的可重复编程逻辑门阵列。与传统技术相比,FPGA不仅具有设计方便,灵活和校验快等特点,可以大大缩减研发时间,减少设计费用,降低设计风险;同时将:FPGA技术、微控制器、雷达显控界面结合的系统应用于设计高性能的雷达信号处理机,可提高系统集成度,减小电路规模,从而提高可靠性,无论在速度、体积方面,还是在设计的灵活性上都能适应现代雷达信号处理系统的要求。

1 航管二次雷达地面询问编码器的工作原理

1.1 编码器功能描述

航管二次雷达地面站收发系统由编码器、询问器、接收机三部分组成。如图1所示,编码器是整个雷达的中心,它有三个作用:

(1)产生整机的同步脉冲。它可以工作于外同步和内同步两种方式。当同步脉冲工作于内同步,即当二次雷达独立工作时,产生重复频率f=150~450 Hz的整机同步信号S0。当二次雷达和一次雷达配合工作时,由一次雷达提供整机同步触发信号,即外同步时,二次雷达的重复频率f2和一次雷达的重复频率 f1有以下的关系:

①当150 Hz≤f2≤450 Hz时,f2=f1;

②当450 Hz

③当900 Hz

民航规定f2≤450 Hz。重复频率的选择取决于作用距离的大小。

(2)产生各种询问模式。

发射机在询问脉冲的调制下,产生1 030 MHz的射频脉冲,经三端环形器送到天线。天线在同步脉冲的控制下,将P1,P3进入和通道,P2进入差通道。接收机在将1 090 MHz的射频应答信号转换成视频信号,送至终端装置进行处理。

1.2 编码器同步信号S0产生原理

式中:Rlmax为最大询问距离;λI为询问射频波长;GI为询问天线增益;GR为应答天线增益;Prmin为应答器接收机灵敏度;Pr为地面发射机的发射功率;LI为三端环形器和馈线系统损耗;LR为应答器馈线增益。

询问周期对应S0同步信号周期。结合实际工程的参数,按照上面公式计算出询问时间每1μs对应的询问距离为150 m的比例。由人工航线监视的二次雷达的作用距离为450 km时,对应询问周期为3.5 ms;为370 km左右时,对应询问周期为2.5 ms。机场终端区域Ⅲ监视用的作用距离为140 km时,对应询问周期为0.000 9 ms。

1.3 编码器系统结构

图2所示为编码器信号处理框图。它采用雷达显控界面、微处理器和FPGA芯片相结合的信号处理系统。对于编码器的设计主要实现上述三个功能(见1.1小节),采用IPcore技术提取界面下传数据采集和微处理器命令,采用分频电路产生各模块所需的时钟,依据询问命令产生同步编码信号S0。由此编码产生常规模式及其交替模式,S模式的询问信号。可用数字示波器进行实时测量;射频组件可对编码信号进行测试并产生线性检波信号,经A/D转换后,送入 IPcore采集数字信号,并上传至界面定性显示波形。

2 编码器的询问信号格式

2.1 常规模式

按照国际民航组织的规定有六种常规询问模式,分别称为1,2,3/A,B,C,D模式,各种模式的P1与P2,P1与P3之间的时间关系如表1所示。

其中,1,2两种模式专用于军用识别询问;3/A模式用于军用和民用识别询问;C模式用于高度询问;D模式作为备用询问模式,其询问内容目前还在商议之中。这些询问模式,由间隔不同的脉冲对组成,其时间关系如表1所示。其中,第一个脉冲称为P1;第二个脉冲称为P2;第三个脉冲称为P3。脉冲P1, P2,P3格式为脉宽(O.8±O.1)μs,上升沿在1~5 μs之间,延迟在0.2~5μs之间。脉冲P1和P3都是通过询问通道传输的,它们之间允许不同的时间间隔。

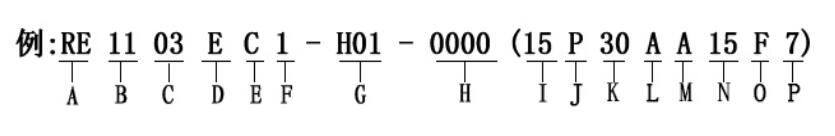

2.2 S模式询问信号格式

图3表示S模式询问格式。前两个脉冲P1和P2的脉宽为0.8μs,间隔为2.0μs。在P2脉冲后是一个长脉冲P6,它的持续期为其脉宽,取16. 25μs或者30.25μs,其中有许多相位为反转脉冲,用其携带发射数据。P6的最后24位为飞机地址,是通过全呼询问获得的。其中,第一个反相位于脉冲前沿后1.25μs,即P5为“同步相位反转”信号,提供给S模式应答器作为始终同步,从而对后续的数据进行对应解码;同步相位反转脉冲也用作应答信号发射的时钟参考。询问机通过计算同步相位反转脉冲的发射与接收到的第一个应答脉冲之间的时间间隔来测量飞机的距离。数据通过DPSK信号来发射反相位置的间隔为0.25μs,从而产生4 MHz的数据比特率。根据要求,整个发射数据的比特为56 b或者112 b。

2.3 S模式奇偶与地址

S模式P6数据位的最后奇偶24 b信息通过改进的循环冗余(CRC)编码来计算,其多项式如下:

奇偶性在发射端计算,并与24个比特位飞机地址加入到信息中。在接收端,奇偶性再次被计算,并与信号中的奇偶和地址信息做比较,这样可以确定信息是否发送无误。多项式G(x)有助于错误探测和纠正,可以利用移位寄存器来实现,其电路如图4所示。前32个比特位(或长S模式的88个比特位)无修改地发送,但在其发送时,会在移位寄存器反馈端乘以G(x)。对于最后循环反馈端探测信息的最后24 b会被断开,并由24 b地址比特位代替。其结果就是信息的最后24 b包含了24 b的奇偶区域,并与飞机地址相加再乘以G(x)。

3 编码器设计流程

编码器的FPGA设计流程图如图5所示。首先提取雷达控制界面的控制命令,判断出询问模式和询问方式(询问交替方式)。结合S0产生原理和雷达询问距离理论,用计数分频编码产生S0同步信号。

若是常规模式,在S0同步信号沿触发下,按照软件控制界面不同的控制命令,分别编码产生周期性的6种单模式(见表1)询问信号;并且产生对应的周期性提取信号,结合交替模式产生相应的编码信号。

若是S模式询问,设计流程是:首先产生S模式的前导脉冲P1,P2和数据位同步信号P5,然后判断是短S模式(P5数据位56 b),还是长S模式(P6数据位112 b),再调用XCV600E内部的双口RAM IPcore模块进行数据采集,对s模式最后24 b的飞机地址数据位进行奇偶地址校验编码,校验规则如图4所示。之后再对校验结果进行DPSK调制编码,然后按照S模式的信号格式,在数据同步位信号P5 (见图3)控制下,产生S模式询问信号。

4 询问信号的仿真波形

4.1 常规模式1:1:1交替询问信号的仿真波形

首先是同步触发信号S0的产生,由雷达显控界面人工操作改变,对应二次雷达监视的范围不同而具有不同的周期。一般S0的周期有2.5 ms,3.5 ms,0.000 9 ms 。

当S0的周期为3.5 ms时,其仿真结果如图6所示。XCV600E的FPGA时钟为40 MHz,产生周期性的S0信号。采用计数4倍、8倍、1O倍分频产生各模块所需的时钟。如果改变S0的周期,可用类似的方法产生;其次是三三交替询问模式的产生。如图6所示,在询问控制界面中,任选6种常规模式中的3种。在同步编码信号S0的上升沿进行触发,在第一个S0周期内产生询问模式mode_1,第二个S0周期内产生询问模式mode_2,第三个S0周期内产生询问模式mode_3 A,第四个S0周期内产生询问模式mode_1。按此规律周期性的产生即为三三交替询问模式。其中,S1_revert,S2_revert, S3_revert是循环状态机产生的周期性提取信号,分别周期性提取mode 1,mode 2,mode 3 A的编码信号,其他单模式的编码产生方式类似。

4.2 S模式CRC校验编码和译码仿真波形

依据S模式询问机编码器的P5位奇偶地址校验的多项式电路规则(见图4),应用Matlab软件建立24个D触发器组成的移位寄存器进行仿真。如图7所示,仿真结果中以P5。为56 b为例,data为原始的P6数据信号,data为 “11111111101101010011010100100000011011111101001100001000”序列。其中,最后24 b表示飞机地址(初次获得飞机地址是由“全呼询问”获得该校验是“点名询问”方式);encode为校验输出,其序列为 “11111111101101010011010100100000000101101010000100110000”;然后把encode作为输入按照应答器解码电路进行译码,译码结果为decode。由此发现译码结果与原始输入数据相同,保证了校验编码设计的正确性。

5 结 语

利用FPGA的高速运算能力和IPcore技术设计高性能的二次雷达地面询问编码器,不但在数据采集、信号编码时具有自适应性和可控性,而且解决了雷达信号的实时性问题,完成了多种复杂信号处理的单片FP-GA集成,有效地解决了小电路板尺寸与大存储空间的矛盾,从而提高了系统的集成性,进一步节约了资源。同时利用“软件显控界面+FPGA+MCU”结合的架构技术使之更容易成为微型系统。

电子发烧友App

电子发烧友App

评论