多线程是一种基于硬件或软件的处理技术,它的首要目标是计算型工作中利用并发来提高性能。多线程也可以用于区别各种任务,以便可以将优先权分配给更多时间敏感的流量,如语音、视频或关键数据。而公认的基于软件的多线程技术,如任务切换和基于软件的线程调度已经存在了相当一段时间,很少有人知道基于硬件的多线程的历史。基于硬件的多线程技术其实已经存在了相当长一段时间,其实现可以追溯到20世纪60年代的CDC6600。在CDC6600电脑中,10个硬件线程被用来保证从I/O处理器到约16个外围设备的响应时间。这个例子的处理器运行速度远远超过了许多I/O设备,是一个充分利用多线程优势的典型应用,因为空闲处理时间可以被从线程到线程切换的有益工作所取代。在70年代,Denelcor HEP机是在CPU内,而不是在I/O实际执行线程切换。类似上例,最终结果是每个周期的指令(IPC)有了显著改善。之后10年推出的其他几个系统和学术研究进一步展示了硬件多线程的好处。

今天的市场上有许多多线程处理器。英特尔公司已经利用其超线程技术将该技术引入高端计算应用领域。此外,其他许多SoC制造商,如Broadcom、Lantiq、Mobileye、NetLogic Microsystems、PMC-Sierra、Ralink Technology和Sigma Designs也交付了上百万个采用多线程处理器的产品。许多这样的SoC都采用了基于业界标准MIPS架构的多线程MIPS32 34K系列内核或多线程、多处理MIPS32 1004K一致处理系统(CPS)。目前硬件多线程已经成为主流应用,并越来越被视为SoC设计中实现最佳性能的有效方法。

用多线程提高流水线利用率

如前所述,增加一个给定单线程处理器的IPC数量是一个主要目标。通常情况下,即使是非常高性能的处理器也有大量时间闲置,目的是等待数据到达。常见的情况是,带有共享存储系统先进处理器需花50%的时间等待数据在缓存未中(cache miss)后返回。此数据检索的等待时间可能会持续几十个周期,在极端情况下甚至是数百个周期。无论数量多少,处理器在此期间做的都是无效工作。多线程处理器可以在多个线程之间切换以利用这些闲置的周期。这些周期现在可以用来自其他线程的有用指令填满,从而避免未使用的周期白白浪费。这最终将获得更好的流水线利用率并提升系统的吞吐量。

确保线程切换效率的一个关键环节是怎样进行线程相关信息或语境的管理。当映射到一个线程时,每个任务都有相关的上下文信息,如程序计数器和寄存器信息子集,这些信息是以硬件加载和更新的。在单线程处理器中,由于处理器在线程之间切换,这些上下文必须导入(swapped in)或导出。当在线程之间变换时,需要有与保存和恢复操作有关的额外处理。这种负担可能会变得非常繁重,尤其是采用高语境(high context)切换。多线程处理器支持由每个硬件支持的线程的完整上下文存储,无需保存和恢复操作。这种机制支持切换线程或上下文的零周期开销。

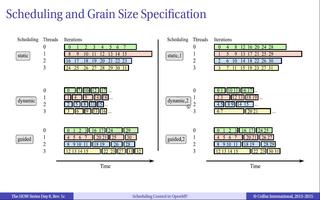

图1显示了多线程是如何提高流水线利用率的基本机制。在这种情况下,在不同的时间点有三个线程出现了缓存未中。在这些线程暂停(stall)期间,其他线程在同一条流水线上做着有用的工作,从而增加了IPC。

MIPS多线程技术

MIPS科技的多线程技术基于两个层次框架,涉及虚拟处理单元(VPE)和线程上下文(TC),支持每个周期的线程切换。每个多线程内核多达可支持两个VPE,它们共享其他硬件资源中的一条流水线。不过,由于每个VPE可以有自己针对高速缓存的转换后备缓冲器(Translation Look-aside Buffer,TLB),因此它们都可作为针对一个SMP Linux操作系统的两个独立处理器出现。对于更细粒度的线程处理应用,每个VPE可以支持多个TC。这些TC共享一个执行单元,但各有各的程序计数器和内核寄存器文件,以便每个TC都可以处理来自软件的线程。34K内核多达可以支持分配在两个VPE上的九个TC,在运行时进行优化和分区。利用最小的芯片面积可执行MIPS多线程功能。

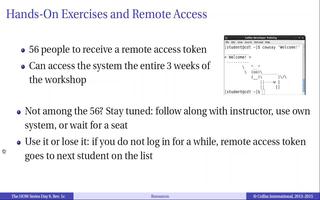

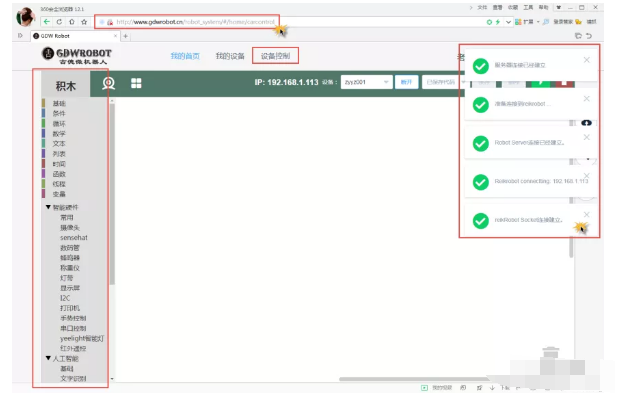

34K内核也允许为线程分配处理器周期,并利用一个可选的服务质量(QoS)管理块设置相对线程优先权。这有助于实现两个优先机制,确定总线上的信息流量。第一个机制允许用户让某一个线程优先于另一个。第二个机制用来根据时间的变化为特定线程分配一个指定的周期率。这两个机制的结合使用可以有效地给线程组分配带宽,更好地控制延迟。在实时系统中,系统级的决定是非常关键的,而QoS块有利于改善系统的可预测性。图2a显示了34K内核中VPE、TC和QoS块的关系。

1004K CPS是MIPS科技的最新一代多线程处理器。该系统支持多达四个多线程内核,每个内核都可以配置为像34K内核那样支持2个VPE。在1004K CPS中的多个内核通过一个一致管理单元连接在一起,以保持每个CPU的L1高速缓存之间的一致性。一致多内核架构的每个内核的多线程集成允许1004K CPS超过同类单线程多核处理器的总性能。该系统还包括一个可选模块,为来自I/O外围设备的数据传输提供一致性,从而通过卸载作为操作系统一部分、通常运行于软件的I/O一致性方案获得额外的性能。一致处理系统还包括一个全局中断控制器,可以接收多达256个中断并把它们分配到内核,或每个内核内的硬件线程。整个系统采用MIPS L2高速缓存控制器,通过一个扩展的256位宽接口连接到一致管理单元,以优化一致系统和L2高速缓存之间的吞吐量。EJTAG、“一致管控”程序和数据跟踪块完善了系统,通过开发工具为系统中的每个CPU内核和一致单元提供了同步的能见度。

SMP Linux被用来考察VPE接口的效应,从而保持高级API不变。这使得对现有传统内核的利用在新内核出现后也不会改变。此外,一些诸如ThreadX的RTOS的SMP版本包括对细粒度、基于TC的多线程的支持。应该指出的是,1004K的多线程和多核硬件功能利用了一个通用的软件编程模型。也就是说,例如,有人用SMP Linux开发的线程应用可以有效地运行在34K或1004K上,而无需修改,而SMP内核可以实现任务的亲和性以及跨线程和内核的工作量负载均衡决策。

图2a:34K顶层架构。

图2b:1004K顶层架构。

多线程应用实例

当决定多线程系统是否适用于一个特定应用时,设计人员必须考虑几个因素。首先,设计人员必须考虑软件和所需的功能集,包括不同的任务、可能分割这些任务的方式、每个任务的性能需求、不同任务的总线互动、多媒体等任务的特殊需求,以及其他考虑因素。其他主要考虑因素包括任务、安全性,当然还有功耗和成本的协调程度。

的确,分析起来往往不太简单,因此很好地理解重点至关重要。例如,如果目标是以最低的成本实现最高的IPC,设计人员就可以创建多线程系统来利用单个内核中不同的线程,并运行在最高频率下。在另一个设计中,功率可能是一个关键问题,所以设计人员可以选择将任务分布于多个内核的多个线程,并降低频率以减少功耗。MIPS-Based多线程系统的关键是可扩展性,在需要时帮助设计人员达到尽可能高的性能,而当性能并不是最优先考虑时,则可以缩减可扩展性。另一个例子是,一个系统可能需要运行2个操作系统,同时要满足非常严格的QoS和成本限制。设计人员可以利用两个VPE运行软件,其中一个运行RTOS,另一个运行bare iron,同时完全隔离语音或视频等QoS敏感的应用。这些都可以在不运行第二个内核的情况下实现。以下例子的使用模型已经部署在用于汽车和网络的MIPS-Based多线程SoC中,证明了广泛的应用都可以受益于多线程。

1.汽车驾驶辅助系统

多线程系统设计实际部署的第一个例子来自一家基于视觉的驾驶辅助系统(DAS)的SoC领先供应商。图像和视频分析在性能和成本方面的进步使这些技术开始进入消费市场。但是,对这类技术的不断改进是一个非常艰巨的任务。例如,该SoC供应商使用了34K处理器的多线程功能,大幅提高了其视觉系统(原本基于单线程内核)的性能和效率,系统接收来自摄像头的数据,查找图像中的元素,生成车道偏离、前向碰撞、视觉/雷达融合及行人侦测等警告。

该SoC系统采用一系列图像处理引擎作为外围设备到主CPU总线的连接,以提供和接收实时数据。在这个系统中,大量的数据和指令从CPU传输到图像处理引擎。伴随着典型的指令缓存未中,这导致了单线程CPU无法解决的极具挑战性的瓶颈。事实上,供应商的原始系统具有一个仅为0.3的IPC。新系统采用一个单线程架构,由于其性能要求很高,这意味着要么放慢整个系统,要么跳过数据处理,因而有可能导致错误。增加CPU时钟速度更加剧了这一问题,因为这只是增加了处理器暂停的频率。此外,增加的额外内核增加了总线竞争数量,从而影响了实时带宽。

通过仿真,设计人员的结论是,一个多线程系统将通过管理整个系统包括8个图像处理引擎的多个操作来性能提升。他们采用了一个4线程34Kf内核与8的图像处理引擎互动。一个QoS管理器起到了调整和优化关键线程的重要作用。实际上,这种架构有助于将IPC从0.3提高到0.9。使用QoS管理器对IPC从0.6到0.9非常关键。此外,有了如此高的IPC,增加的CPU时钟实现了显著的改善。事实上,由于利用了其多线程和其他架构的改进,供应商只需将频率从110MHz适度地增加至166MHz,同时维持3W的功耗(这是前一代产品的功耗),就能够实现其性能目标。此外,第二个34Kf内核的实例可以支持一个用户的专有算法。在这两个处理器线程之间的通信是通过对一个线程间通信块的修改来实现的,这实际上有助于提高系统一致性。对于未来的系统,将要求更高的性能和更低的成本。该SoC供应商将会采用一个4内核1004Kf CPS,以确保设计能够满足这些目标。

2.宽带CPE/住宅网关

住宅网关是另一个面临日益集成的系统。宽带客户端设备已经发展到不仅是提供DSL、有线或PON等宽带服务等基本接入的调制解调器设备。它们已成为集成式住宅网关或集成式接入设备,其中包括路由/交换、双绞线/同轴/电源线/WiFi网络功能、安全、USB和VoIP支持等,以及基本的调制解调器功能。某些架构还集成了存储功能,其中的网关可作为媒体服务器使用。这种集成使网关系统的设计极具挑战性,而多线程可以提高性能和/或改进这些设备的整体架构。

无线家庭网络和宽带接入半导体市场的全球技术领导厂商Ralink Technology已在网关中成功部署了多线程MIPS-Based SoC。ADSL IAD是Ralink的首个基于34K内核的芯片,目前已批量生产,并已成功部署在欧洲电信运营商的网络中。多线程已被证明非常适合这个三网融合系统,因为它有助于更有效地运行多个应用。此外,通过使用VPE对时间敏感流量进行隔离是保证确定性响应的关键。该SoC采用一个34K内核和在两个VPE上的四个线程。第一个VPE即VPE0执行三个线程,支持WLAN、以太网和USB处理,而第二个VPE即VPE1执行一个线程,支持ATM和VoIP。凭借这个架构,Ralink能够以单个器件有效地提供确定性VoIP响应,支持多个应用。

本文小结

硬件多线程是一种已经成为主流的技术,今天有许多芯片供应商在为各种应用提供MIPS-Based多线程SoC。本文讨论了网络和汽车应用,而多线程可以用于任何具有很多并发任务,或者是QoS非常重要的系统。其他厂商已经实现了用于机顶盒、高端存储和网络基础设施设备的MIPS多线程SoC。而一些评估已开始用于移动应用中使用的多线程,如智能手机和平板电脑。作为集成的通信、生产力和多媒体娱乐设备,这些设备的复杂性还在不断增长。多线程将是有效处理多个移动应用(其中一些是延迟敏感的应用)的理想解决方案。当然,可以采用使用多个内核同时处理线程的强制方法,但是采用多线程是迄今为止实现IPC和/或QoS性能要求的一个更完美和成本更低的方法。通过提供支持硬件多线程的单内核和多内核产品,MIPS科技具备独特的优势,可帮助设计人员以非常具有成本效益的方式开发高性能和低功耗的SoC。

电子发烧友App

电子发烧友App

评论