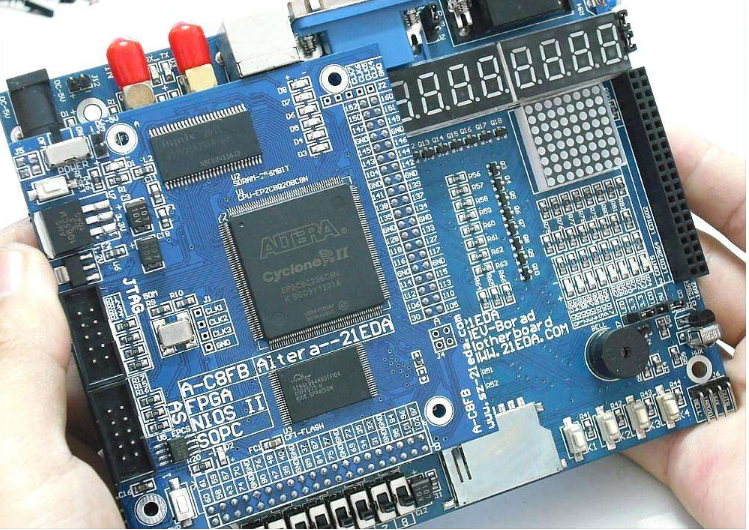

电子设计自动化EDA(Electronic Design AutomaTIon)是指以计算机为工作平台,以EDA软件为开发环境,以硬件描述语言为设计语言,以可编程逻辑器件PLD为实验载体(包括CPLD、FPGA、EPLD等),以集成电路芯片为目标器件的电子产品自动化设计过程。该过程目前已广泛应用于电子电路与系统的设计和产品的开发中.逐渐取代了传统的手工硬件电路设计方式。设计的系统具有体积小、重量轻、功耗小、速度快、价格低、可靠性高、设计周期短等优点。一个功能完备的EDA设计软件加上一片普通功能的可编程逻辑芯片就可以构成以前需几百个集成电路才能构成的电子系统。

目前常用的可编程逻辑器件有CPLD(Complex Programmable Logic Device,复杂可编程逻辑器件)和FPGA(Field Programmable Gate Array,现场可编程门阵列)。常用的EDA软件包括VHDL、Verilog HDL、ABEL等硬件描述语言。其中,VHDL作为IEEE的工业标准硬件描述语言,受到众多EDA工具厂家的支持,在电子工程领域,已成为事实上的通用硬件描述语言。

Xilinx公司和Ahera公司的FPGA可编程部分的物理实现方式为RAM。它最大的优点是可以多次重复编翟,缺点是易失性。因此每次上电后,处理机都需要将用户设计的FPGA配置文件从外部存储器中下载到FPGA中。从外部存储器将FPGA配置文件下载更新的方式有以下三种:

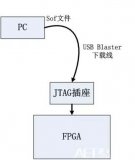

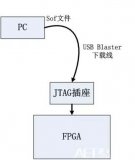

(1)JTAG口下载方式

将配置文件放到一台主机中,主机通过专用线与单板上的JTAG口硬件相连接。在这种方式下每次下载都需要硬件操作,因此只适用于开发、调试阶段,设备在现场工作时就不能再使用这种方式。

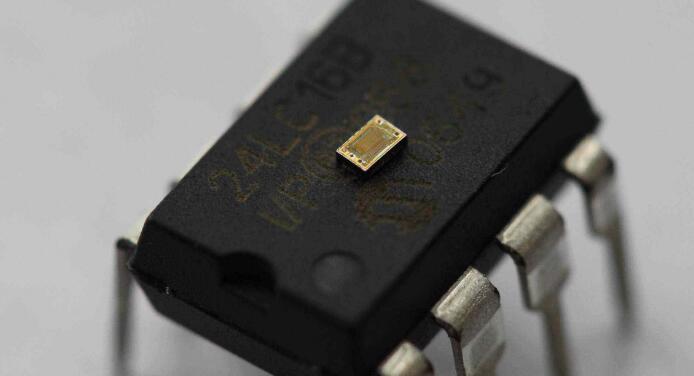

(2)片外串行PROM下载方式

在每片FPGA周围放置一片或几片(由FPGA容量决定)串行PROM,在系统上电时,自动将FPGA配置文件从PROM下载到FPGA中。此方式也是xilinx、A1tera等公司重点介绍的方式,适用于比较稳定的系统。但随着FPGA芯片密度的增加,串行PROM已不能适应大容量、高密度的FPGA的配置。而大容量的并行PROM所要求的寻址方式又不能直接与FPGA接口。当系统中的FPGA配置文件需要升级更新时,必须将机箱打开,通过JTAG口首先将.PROM中的配置文件更新,然后再重新启动系统,将更新后的配置文件从PROM下载到FPGA中,这样才能完成一次FPGA配置文件的更新。

以上两种方案都存在必须进行硬件操作(将机箱打开,使用主机通过JTAG口)的缺点,在主机上必须安装专业软件才能完成FPGA配置文件的更新。

(3)处理机控制Flash下载方式

本文根据Xilinx、Altra公司手册及以前的工作经验,提出和完成了一种新的FPGA配置文件下载更新的方式。这种方式适用于支持网络通信的系统中。在每次系统启动时。由处理机从Flash中读出FPGA配置文件,再下载到FPGA中。即当需要升级更新FPGA配置文件时,通过网络将配置文件发送给处理机,由处理机更新系统中的Flash。当Flash内容更新后,再由处理机控制将配置文件自动下载到FPGA中。这样在不需要任何硬件动作和专业软件的情况下,只需要进行常规软件操作就可以更新FPGA的配置文件。但由于Flash是并行数据线,需要通过一片CPLD将从Flash中读来的数据转换成串行数据输出到FPGA。

1 FPGA下载配置模式

FPGA配置文件的下载模式有五种:主串模式(masterserial)、从串模式(slave serial)、主并模式(master selectMAP)、从并模式(slave selectMAP)及JTAG模式。其中,JTAG模式在开发调试阶段使用。为了便于开发设计阶段的调试,本核心路由器设计将JTAG口直接做在信号处理板上。

主、从模式的最大区别在于:主模式的下载同步时钟(CCLK)由FPGA提供;从模式的下载同步时钟(CCLK)由外部时钟源或者外部控制信号提供。主模式对下载时序的要求比从模式严格得多。因此从处理机易于控制下载过程的角度考虑,选择使用从串模式或从并模式较为合适。本设计采用从串模式进行FPGA配置。从串模式引脚说明如表l所示。

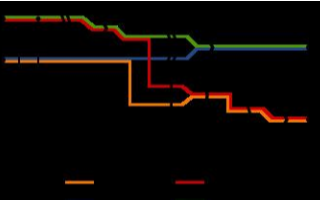

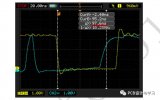

从串配置时序图如图l所示。TPROGRAM是配置逻辑的复位时间,对xilinx VIRTEXE和VIRTEX2系列,最小应大于300ns。TPL为复位延迟时问,表明配置逻辑复位的延续。对VIRTEXE系列来说,当复位信号PROG变为高电平时,INIT立即变为高电平,配置逻辑就可以接收配置数据流;而对于VIRTEX2系列,TPL最小有500ns的延迟。TICCK为配置时钟CCLK的输出延迟。

当PROG有效(对配置逻辑进行复位)时,FPGA将置低INIT和DONE;PROG变为高电平时,INIT将延迟一段时间用于表明复位状态的延续,继续置低INIT可以延迟配置的进行。当FPGA正在接收配置数据时,INIT变低,表明CRC校验错。当配置完所有的数据时,若配置正确,DONE将会变高。此后FPGA开始启动序列,继续置低DONE可以延迟启动的进行。

2 具体设计

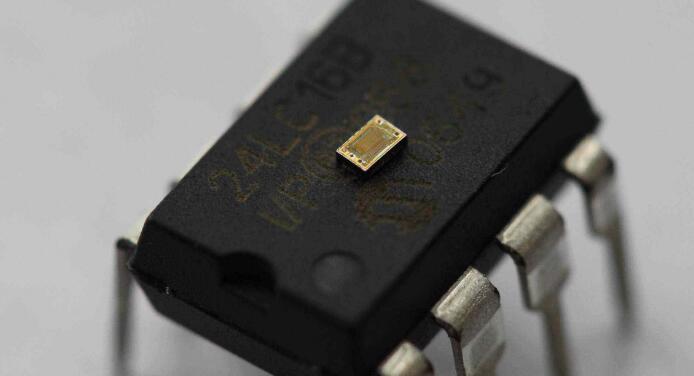

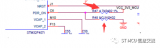

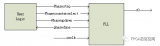

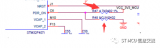

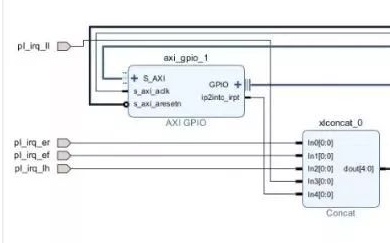

国家数字交换系统工程技术研究中心承担的国家863项目高性能IPv6核心路由器采用一片Intel E28F128J3A150 16位Flash作为BootFlash对PowerPC2860(MPC860)处理机进行加电配置下载更新的方案,其多余的存储空间完全可以存放下FPGA所需的配置文件。加电复位、系统启动后,由处理机与一片XilinxXC95288XL CPLD配合,控制FPGA配置文件从Flash下载到FPGA中,完成对FPGA的配置。860处理机支持网络功能,当配置文件需要更新时,可通过网络将新的配置文件发送到处理机,然后再由处理机更新系统中的Flash。采用XC95288CPLD配置FPGA的具体电路设计结构如图2所示。

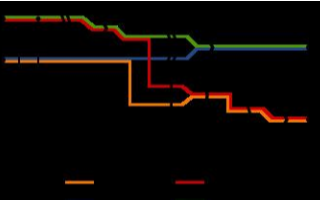

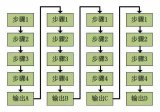

图2中,CPLD主要功能是把从Flash中读出的数据转换成串行输出,然后再将地址递增。CCLK(信号由CPU时钟产生。PROG信号则由CPU输出的地址数据经译码模块产生。XC95288C PLD逻辑结构如图3所示。

下面分别介绍各功能模块的具体实现:

(1)数据转换成串行输出功能模块:使用了一个右移寄存器。从16位Flash来的并行数据DIN[0:15]加载到移位寄存器后,依次从DOUT串行输出到FPGA中。

(2)地址递增功能模块:此功能由两个计数器完成。由于Flash是16位并行数据端口,因此第一个计数器功能是逢16进1,第二个计数器功能是Flash地址递增。当移位寄存器的16位数据都输出到FPGA中后,第一个计数器输出端口CNT[0:3]都为“1”,经过“与门”逻辑使得第二个计数器加l。Intel E28F128J3A150 Flash为16MB,共需要25根地址线。由于Flash是16位的,因此ADD[3l]不连接。所以第二个计数器和地址线ADD[7:30]相连.以完成Flash地址的递增。

(3)CCLK信号产生模块:CPU来的时钟信号将数据信号DOUT输出,经一个“非门”逻辑延迟半个周期后产生CCLK,CCLK再将DOUT上的数据送到FPGA中。这样将读写。DOUT数据的时刻叉开,避免了冲突。

(4)PROG信号产生模块:当需要下载FPGA程序时,由CPU产生一个地址信号ADD[O:30],经译码器译码产牛PROG控制信号。此地址由用户自行设定。

以上模块均采用VHDL语言描述。数据转换成串行输出功能模块是核心部分,它可实现并行数据串行输出。

本文介绍了通过处理机用CPLD和Flash实现FPGA配置文件下载更新的方法。与传统的JTAG或PROM串行下载配置方法相比,此方法具有更新配置文件灵活方便、易于操作、适用于大容量FPGA下载的特点。采用此方法可以不用打开机箱即可随时更新FPGA配置程序,特别适用于需要不断更新的系统设计中,具有较为广阔的应用前景。

相关推荐

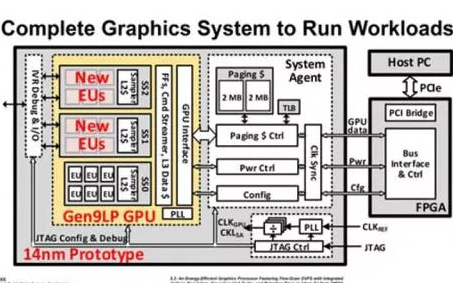

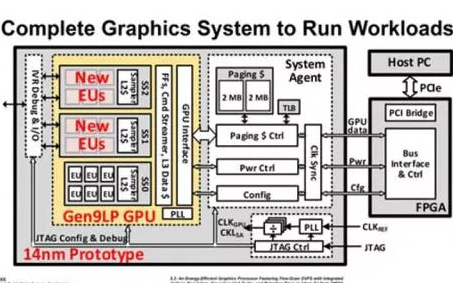

英特尔通过聘请业内最知名的AMD前GPU架构师Raja Koduri负责研发其独立GPU产品。

发表于 2018-04-04 08:52

•

57次阅读

Intel公司的Cyclone 10 LP FPGA系列是低成本和低静态功耗的器件,提供高密度可编门...

发表于 2018-04-04 08:15

•

3次阅读

致力于在功耗、安全、可靠性和性能方面提供差异化的领先半导体技术方案供应商美高森美公司(Micros...

发表于 2018-04-03 10:40

•

469次阅读

ZCU104 评估套件可帮助设计人员为监控、高级驾驶员辅助系统 (ADAS)、机器视觉、增强实境 (...

发表于 2018-04-03 08:30

•

671次阅读

CPU和GPU都属于冯·诺依曼结构,指令译码执行,共享内存。FPGA之所以比CPU、GPU更快,本质...

发表于 2018-04-02 17:52

•

338次阅读

FLASH芯片已经是应用十分广泛的存储材料,flash芯片可进行可快速存储、擦除数据的存储物质。本文...

发表于 2018-04-02 17:22

•

290次阅读

发表于 2018-04-02 16:43

•

72次阅读

![fpga的图像mif文件vga显示问题,出来是白色一片]()

2018 年 3 月 16 日,赛灵思又面向中国市场专门举行了一场信任 CEO 见面会,会上,已经在...

发表于 2018-04-02 11:06

•

208次阅读

系统设计有时十分复杂,需要充分了解许多不同的元件,如果解决方案的各环节可以进行原型制作并快速演示,就...

发表于 2018-04-02 09:33

•

716次阅读

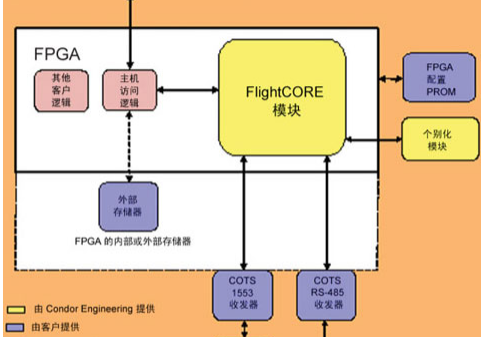

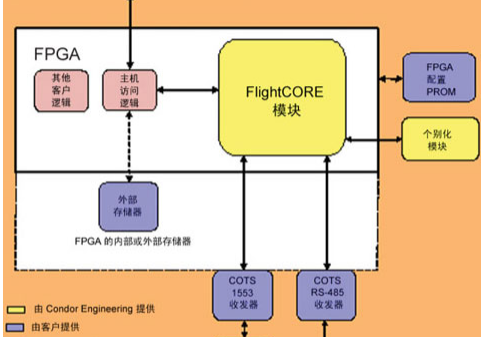

本文将介绍一种基于现场可编程门阵列 (FPGA) 核心的实施体现了先进的现代航空电子设计方法。这项技...

发表于 2018-04-02 09:27

•

641次阅读

FPGA 对绝大多数的人来说相对有些陌生。经常有朋友问我,你们成天搞的这个 FPGA 到底是什么东西...

发表于 2018-03-31 08:20

•

1710次阅读

今日发布“2011中国电子工程师生活与工作状况调查”结果。本次调查从2011年4月25日开始,至5月...

发表于 2018-03-31 07:14

•

236次阅读

这是一个非常经典的TI的关于FLASH存储模块的程序,在几乎所有的关于MSP430的书籍等资料上都可...

发表于 2018-03-30 16:02

•

186次阅读

发表于 2018-03-30 15:07

•

558次阅读

![【下载】《从零开始学CPLD和Verilog HDL编程技术》]()

在简单电路中,当频率较低时,数字信号的边沿时间可以忽略时,无需考虑时序约束。但在复杂电路中,为了减少...

发表于 2018-03-30 13:42

•

143次阅读

FLASH芯片是应用非常广泛的存储材料,Flash芯片可进行可快速存储、擦除数据的存储物质。本文主要...

发表于 2018-03-30 11:42

•

197次阅读

发表于 2018-03-29 17:11

•

573次阅读

![【下载】《CPLD/FPGA的开发与应用》]()

发表于 2018-03-29 17:11

•

573次阅读

![【下载】《CPLD/FPGA的开发与应用》]()

Critical Link选择其MityDSP-L138F嵌入式系统模块作为SDR的基础,因为该模块...

发表于 2018-03-29 11:05

•

49次阅读

发表于 2018-03-29 10:53

•

235次阅读

![怎么看FPGA管脚定义]()

发表于 2018-03-28 17:14

•

878次阅读

![【下载】《FPGA高手设计实战真经100则》]()

时钟是数字电路中所有信号的参考,特别是在FPGA中,时钟是时序电路的动力,是血液,是核心。

发表于 2018-03-28 17:12

•

534次阅读

FPGA相比于CPU,最大的优点在于速度,简单来讲,FPGA是靠控制每个时钟(Cycle)来驱动信号...

发表于 2018-03-28 17:10

•

726次阅读

FPGA中RAM的使用探索。以4bitX4为例,数据位宽为4,深度为4。

发表于 2018-03-28 17:07

•

476次阅读

在这个以数据为中心的世界,用户对搜索引擎提出了比以往更高的要求。先进的英特尔技术可帮助 必应 利用强...

发表于 2018-03-28 10:22

•

114次阅读

高云半导体 科技股份有限公司今日宣布签约ELDIS科技有限公司为以色列授权代理商。此举标志着高云半...

发表于 2018-03-28 10:19

•

71次阅读

嵌入式技术的发展对MAC协议的实现也提供了很好的技术支撑。本文搭建了一种基于 ARM 和 FPGA ...

发表于 2018-03-28 08:51

•

76次阅读

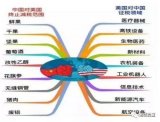

美国为何在许多自己的强项上制裁中国,中国又为何不对进口额超过石油的集成电路产品征收高关税呢?

发表于 2018-03-28 08:34

•

4829次阅读

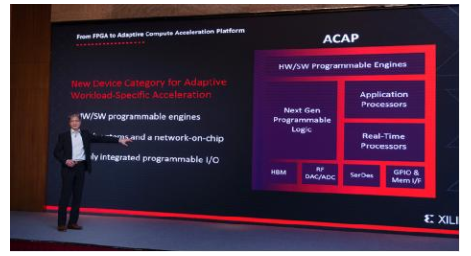

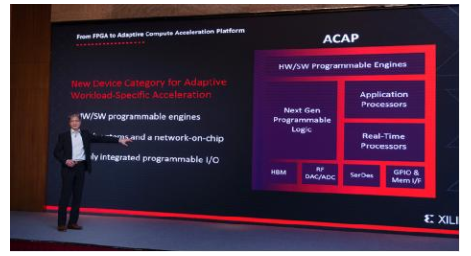

ACAP 的核心是新一代的 FPGA 架构,结合了分布式存储器与硬件可编程的 DSP 模块、一个多核...

发表于 2018-03-27 11:04

•

278次阅读

随着人工智能、5G通信、大数据、云计算等应用的出现,人们对于通信带宽的要求也在不断的提高,这些应用需...

发表于 2018-03-27 11:02

•

243次阅读

Lattice的ECP3/ECP5系列FPGA内部集成了多个sysDSP架构的乘法器模块,基于sy...

发表于 2018-03-27 08:54

•

243次阅读

发表于 2018-03-26 16:16

•

294次阅读

![特权同学海量fpga资料]()

发表于 2018-03-26 16:13

•

241次阅读

![勇敢的芯伴你玩转Altera FPGA连载57:3-8译码器实验]()

之前用serdes一直都是跑的比较低速的应用,3.125Gbps,按照官方文档一步一步来都没出过什么...

发表于 2018-03-26 14:40

•

59次阅读

赛灵思公司第四任CEO Victor Peng 走马上任,他同时兼任公司总裁,Victor Peng...

发表于 2018-03-26 14:34

•

184次阅读

像素是由比特组成的数字。例如,在256级灰度图像中,每个像素的灰度是由8比特(也就是1个字节)组成。...

发表于 2018-03-26 13:18

•

62次阅读

我们使用3x3模板进行边界提取,所以当3x3九个点都是‘1’的时候,输出为‘1’,当九个点都是‘0’...

发表于 2018-03-26 13:00

•

91次阅读

到此问题毫无进展,只好求助ST芯片设计人员做进一步确认,看看芯片是否真的坏了。同时,又请客户的硬件工...

发表于 2018-03-26 11:24

•

224次阅读

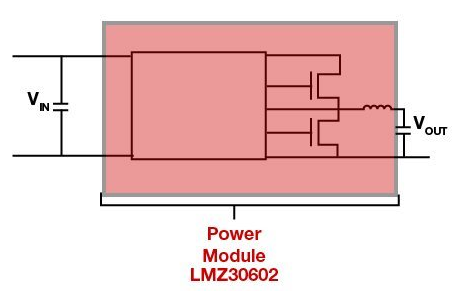

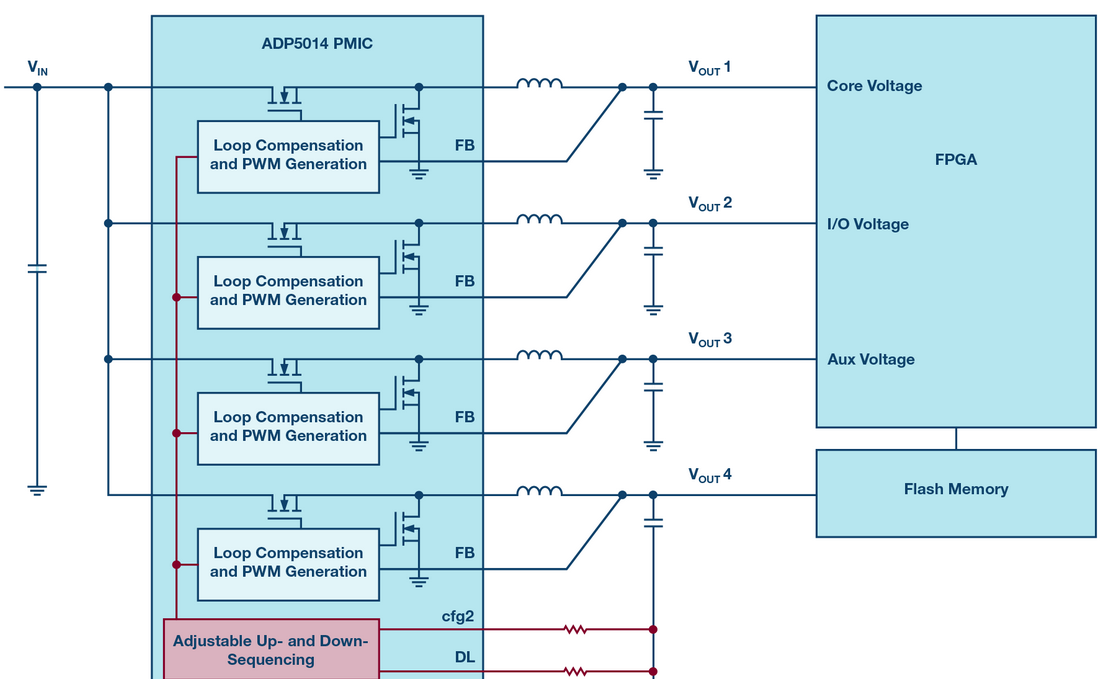

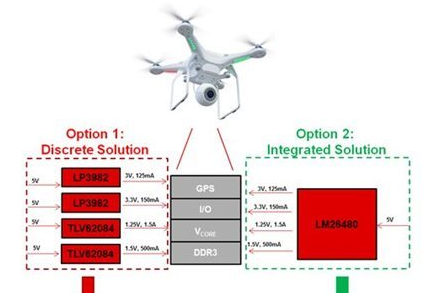

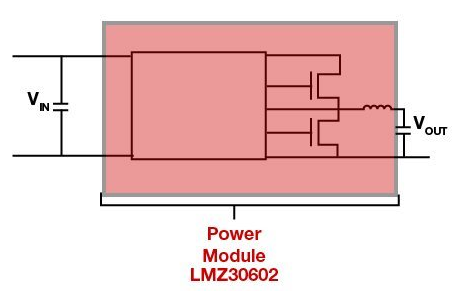

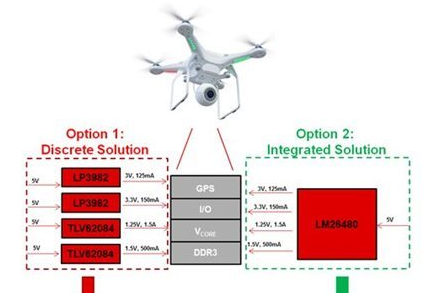

我不得不承认,随着时间的推移为 FPGA 供电变得越来越复杂,本文提供一些建议,希望可以帮助简化 F...

发表于 2018-03-26 09:08

•

2060次阅读

值得注意的是,以上测试是在资源足够频率不高的条件下测试的。根据经验,当资源使用较多,时钟频频较高时,...

发表于 2018-03-24 11:07

•

1079次阅读

发表于 2018-03-24 11:04

•

224次阅读

![fpga逻辑资源]()

相比分立IC,逻辑和线性模块能够提供不折不扣的高性能,同样地,ARM Cortex-M3处理器也是一...

发表于 2018-03-24 10:03

•

123次阅读

发表于 2018-03-23 21:38

•

315次阅读

![勇敢的芯伴你玩转Altera FPGA连载56:流水灯实例]()

找到问题根源后,根据测量结果修改 DSP 对 FLASH 空间的异步时序配置,以保证足够的裕量,问题...

发表于 2018-03-23 11:19

•

306次阅读

随着人工智能和深度学习对运算要求越来越高,人们逐渐认识到并行处理、低延时、低功耗和可重配置的重要性,...

发表于 2018-03-23 11:14

•

386次阅读

检测线圈和检测线路组成一个振荡器,当硬币通过币道时,线圈的电感会发生变化,引起检测电路振荡频率发生变...

发表于 2018-03-22 10:47

•

152次阅读

Victor Peng于2008年加入赛灵思,曾任赛灵思产品执行副总裁兼总经理,主要负责公司各种系列...

发表于 2018-03-22 09:17

•

1093次阅读

这一次给大家分享的内容主要涉及Xilinx FPGA内的CLBs,SelectIO和Clocking...

发表于 2018-03-21 14:48

•

57次阅读

多数FPGA开发者都习惯图形化界面(GUI)。GUI方式简单易学,为小项目提供了一键式流程。然而,随...

发表于 2018-03-21 14:03

•

57次阅读

在二值图像的腐蚀算法过程中我们使用二值图像3x3图像矩阵,由图2可知,当九个格子中不全为‘0’或者‘...

发表于 2018-03-21 11:14

•

66次阅读

信号处理系统一般不单单是模拟信号或者数字信号,一般两者都会有。信号的处理关注的是信号以及信号所包含的...

发表于 2018-03-21 11:08

•

137次阅读

比特币挖矿机,就是用于赚取比特币的电脑,这类电脑一般有专业的挖矿芯片,多采用烧显卡的方式工作,耗电量...

发表于 2018-03-21 10:00

•

643次阅读

总之,硬件的内容很多很杂,硬件那方面练成了都会成为一个高手,我时常会给人家做下方案评估,很多高级硬件...

发表于 2018-03-21 08:40

•

671次阅读

Intel公司的MAX 10 FPGA系列采用TSMC 55nm NOR闪存技术,容量从2K到50K...

发表于 2018-03-20 11:56

•

223次阅读

如果符合一些简单的设计原则,采用最新的Xilinx7系列FPGA架构上实现无线通信。Xilinx公司...

发表于 2018-03-20 11:18

•

394次阅读

加利福尼亚州圣何塞 —自适应和智能计算的全球领先企业赛灵思公司(Xilinx, Inc.,(NASD...

发表于 2018-03-20 10:21

•

1812次阅读

自适应和智能计算的全球领先企业赛灵思公司(Xilinx, Inc.,(NASDAQ:XLNX))总裁...

发表于 2018-03-20 09:23

•

1618次阅读

自适应和智能计算的全球领先企业赛灵思公司(Xilinx, Inc.,(NASDAQ:XLNX))总裁...

发表于 2018-03-20 04:39

•

211次阅读

1、高盛:比特币陷破底危机,恐再摔35% 据Coin Market Cap的报价,比特币昨(12)日...

发表于 2018-03-18 11:33

•

1006次阅读

如图7.20所示,在弹出的Hardware Setup页面里,选择当前硬件为USB Blaster,...

发表于 2018-03-18 10:15

•

536次阅读

在学习一门技术之前我们往往从它的编程语言入手,比如学习单片机时,我们往往从汇编或者C语言入门。所以不...

发表于 2018-03-17 09:19

•

537次阅读

典型高速系统应用框图举例

发表于 2018-03-16 16:25

•

582次阅读

电可擦除和编程只读存储器(EEPROM)是在绝大多数嵌入式应用中都会使用到的用于保存非易失性数据的关...

发表于 2018-03-16 13:55

•

141次阅读

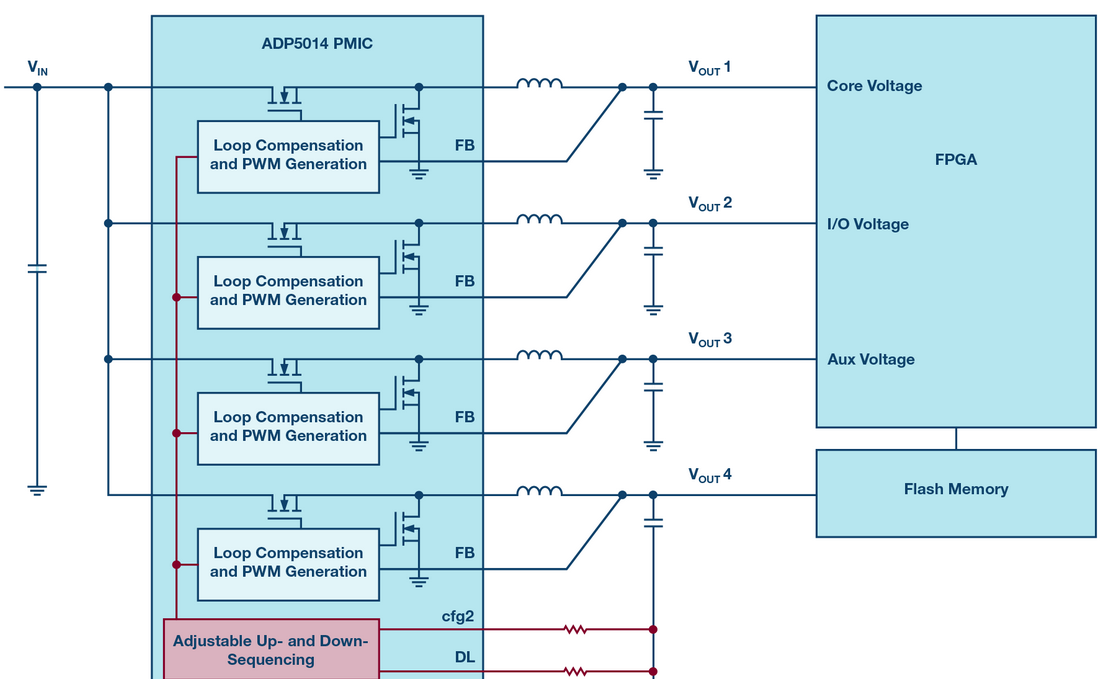

关于为FPGA应用设计优秀的电源管理解决方案已经有许多技术讨论,因为这不是一项简单的任务。 此任务的...

发表于 2018-03-16 11:57

•

1700次阅读

在高产量生产线的末端生产测试中,测试时间分秒必争。当生产线的测试速率与生产速率相匹配时,生产效率达到...

发表于 2018-03-16 10:32

•

110次阅读

随着实施基于云的服务和机器到机器通信所产生的数据呈指数级增长,数据中心面临重重挑战。这种增长毫无减缓...

发表于 2018-03-16 10:17

•

603次阅读

石油作为一种战略资源,越来越受到世界各国的重视;但石油又是一种不可再生的能源,随着世界经济的不断发展...

发表于 2018-03-16 10:16

•

108次阅读

关于外部Flash的代码安全问题和代码在外部执行对整个系统性能的影响,RT105x的加密启动(HA...

发表于 2018-03-16 09:32

•

575次阅读

从市场规模来看,全球FPGA近几年基本维持在50亿美元左右。当前,在国家大力支持集成电路产业发展的环...

发表于 2018-03-15 14:23

•

825次阅读

基于FPGA的二值图像的膨胀算法的实现 Xilinx 突破性技术与产品亮相 OFC 2018,大展光...

发表于 2018-03-14 18:29

•

362次阅读

目前大多数的机器学习是在处理器上完成的,大多数机器学习软件会针对GPU进行更多的优化,甚至有人认为学...

发表于 2018-03-14 18:29

•

2397次阅读

CAN总线规范采用了ISO-OSI(Open System Interconnection Refe...

发表于 2018-03-13 14:09

•

650次阅读

相信每一个电子工程师在项目开发的过程中都不可避免的要进行方案的调试,除了模拟调试我们还必须进行真机调...

发表于 2018-03-13 13:54

•

555次阅读

在Pin Planner界面最下面出现的“Node Name”一列中,有我们的3个信号接口,这里“L...

发表于 2018-03-13 10:09

•

489次阅读

3D图像传感器系统结构包含两只CMOS型图像传感器及缓存图像数据的SDRAM,为了对两只图像传感器...

发表于 2018-03-13 09:55

•

570次阅读

JTAG模式在线下载FPGA的原理如图7.15所示,PC端的Quartus II软件通过下载线缆将b...

发表于 2018-03-13 09:46

•

491次阅读

莱迪思半导体公司布推出全新的FPGA设计软件——Lattice Radiant™,适用于需要开发低功...

发表于 2018-03-12 15:52

•

153次阅读

在进行FPGA学习的时候,我遇到过问题停滞不前,试验没有进展,心情沮丧的时候。那时对底层硬件一无所知...

发表于 2018-03-12 14:18

•

846次阅读

通常如果需要乘以或除以2n,都可以用移位的方法代替。如果乘以2n,都可以生成左移的代码,而乘以其它的...

发表于 2018-03-12 13:56

•

432次阅读

FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在P...

发表于 2018-03-12 10:35

•

562次阅读

工业电子产品的发展趋势是更小的电路板尺寸、更时尚的外形和更具成本效益。由于这些趋势,电子系统设计人员...

发表于 2018-03-12 09:48

•

2943次阅读

抱着热情,自己后来一点一点地深入的学习fpga,一些常规逻辑电路的设计,包括逻辑门电路、数据选择器、...

发表于 2018-03-09 16:45

•

656次阅读

各种方案虽然只是初步的了解一些,但是发现这方面虽然有类似SOPC概念的海思和TI双核解决方案,而且是...

发表于 2018-03-09 14:19

•

651次阅读

横机是针织机械的一种,为生产羊毛衫,围巾帽子等的主要生产设备,全机由130多个零件装置而成。横机机头...

发表于 2018-03-07 08:53

•

3456次阅读

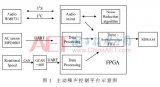

主动噪声控制平台的FPGA实现。基于FPGA搭建了针对汽车的主动噪声控制平台,此平台可以正确实时地采...

发表于 2018-03-05 10:34

•

569次阅读

如果你认为这么多书,怎么看都看不完。那是以一种静止、偏面的观点来分析问题了。其实上介绍那么多课,很多...

发表于 2018-03-04 15:28

•

1172次阅读

惯性导航系统(INS,Inertial Navigation System)也称作惯性参考系统,是一...

发表于 2018-03-04 09:25

•

83次阅读

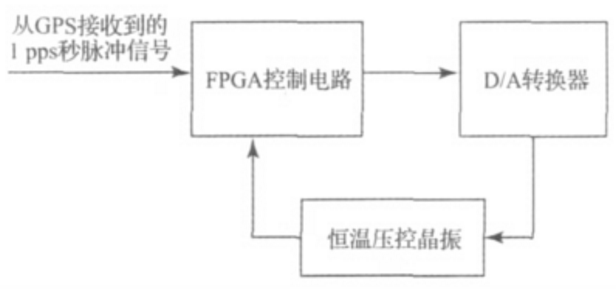

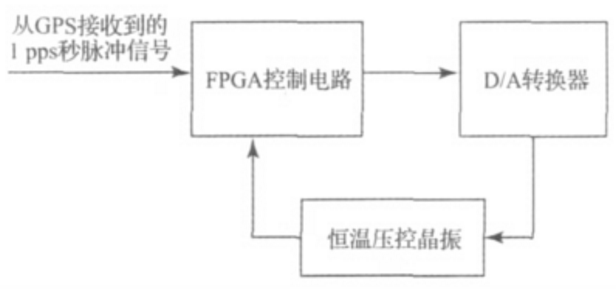

本文主要介绍了基于FPGA的压控晶振同步频率控制系统的研究与设计。利用GPS提供的1pps秒脉冲信号...

发表于 2018-03-02 14:55

•

310次阅读

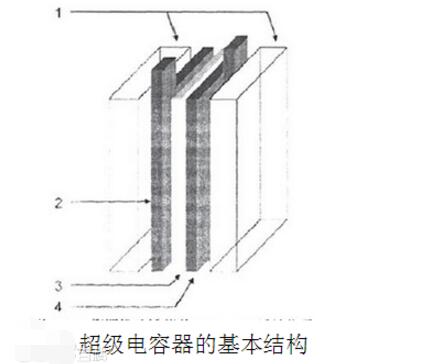

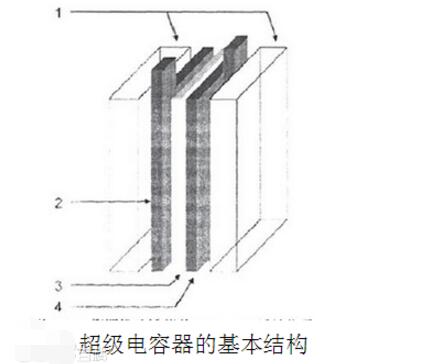

由于超级电容器单体性能参数的离散性,当多个单体串联组成电容器组时,在充放电过程中容易造成过充或过放现...

发表于 2018-02-28 08:40

•

416次阅读

英特尔宣布开始发售英特尔® Stratix® 10 TX FPGA ,这也是业内唯一一款采用 58G...

发表于 2018-02-27 11:55

•

483次阅读

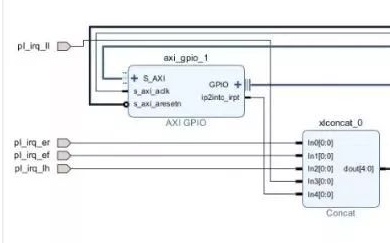

本实验工程将介绍如何利在赛灵思异构多处理器产品系列 Zynq UtralScale+ MPSoC ...

发表于 2018-02-27 11:01

•

4883次阅读

FIR数字滤波器在数字信号处理的过程中有很好的线性相位和稳定性,被广泛应用于音频处理、语音处理、信息...

发表于 2018-02-26 18:44

•

228次阅读

我们最近与Bunny Huang进行了有趣的交流,他是硬件大师以及Chumby,NetTV和Nove...

发表于 2018-02-24 10:53

•

931次阅读

虽然推动业界向小型基站转变的因素众多,但可能最重要的是,消费者想要随时随地都能快速有效地连接到服务提...

发表于 2018-02-20 09:21

•

1300次阅读

随着FPGA技术的发展,数字通信技术与FPGA的结合体现了现代数字通信系统发展的一个趋势。为了使高速...

发表于 2018-02-20 07:50

•

1308次阅读

高端设计工具为少有甚是没有硬件设计技术的工程师和科学家提供现场可编程门阵列(FPGA)。无论你使用图...

发表于 2018-02-17 19:38

•

1794次阅读

FPGA及其外围电路是整个测量系统的核心。外围电路包括以下几个部分:1)电源转换电路,将5V电源转换...

发表于 2018-02-17 03:02

•

110次阅读

不论从哪个角度看,今天的现场可编程门阵列(FPGA),都显得鹤立鸡群,真是非常棒的器件。如果在这个智...

发表于 2018-02-16 17:38

•

2836次阅读

在FPGA中,动态相位调整(DPA)主要是实现LVDS接口接收时对时钟和数据通道的相位补偿,以达到正...

发表于 2018-02-16 17:32

•

1495次阅读

随着检测节点的增多,视觉测量系统需要处理的数据量也不断增大,对视觉测量系统的测量速度提出了更高的要求...

发表于 2018-02-10 13:21

•

311次阅读

评论