摘要: 针对面阵CCD KAI-1020 在高帧频工作模式下的驱动要求, 以FPGA 作为控制单元及时序发生器,完成CCD 高帧频工作模式下的硬件及软件设计,仿真验证了驱动时序的正确性,完成了硬件电路的调试与试验。成像实验表明,该设计满足了CCD KAI-1020 在双端口输出模式下成像的各种驱动控制功能,图像分辨率为1 000×1 000,帧频达到48 f/s。

电荷耦合器件CCD (Charge Coupled Device) 自20 世纪70 年代由贝尔实验室发明以来, 因其分辨率高、测量误差小等优点, 被广泛应用于各种成像仪器中。CCD 按照成像维数分为线阵与面阵两种类型。线阵CCD 因其本身只有一维, 需要进行推扫才能形成二维图像, 主要用于光谱分析与图像扫描等领域; 面阵CCD 因其本身就能形成二维图像, 而被广泛应用于数码相机、摄像机及工业机器人等领域[ 1]。

面阵CCD 按电荷读出方式又分为全帧转移、帧转移、行间转移三种, 其中行间转移CCD 因其不需要机械快门、读出速度最快等优点, 一直被作为高帧频CCD 相机的首选。

CCD 的驱动时序产生方法主要有以下四种: 直接数字电路(IC) 驱动法、单片机驱动法、EPROM 驱动法、可编程逻辑器件法等[ 2]。近些年来, 随着可编程器件的高速发展,FPGA 因其高速并行处理方式, 极强的编程灵活性, 十分适合用来产生CCD 的驱动时序, 加之其能很好地避免其他驱动方式的弊端, 因而已经成为CCD 驱动电路的首选。

本文针对功耗体积要求严格的高帧频高分辨率CCD 相机应用场合, 选用FPGA 作为高速行间转移CCD的驱动控制, 在减小系统体积, 降低系统功耗的同时, 完成控制任务。

1 KAI-1020 结构及特点

KAI -1020 是美国柯达公司生产的行间转移型面阵CCD, 总像元数1 028 (H)×1 008 (V) , 其中有效像元1 000(H)×1 000(V) , 像元尺寸7.4 μm(V)×7.4 μm(H) , 有效成像面积10.5 mm[ 2-3]。

KAI -1020 具有逐行读出和交错读出( 只读取CCD 1 000 行成像有效单元中的500 行) 两种方式, 最大像元读出速率40 MHz , 可以选择单通道或双通道读出。采用逐行扫描, 双通道读出方式, 图像分辨率为1 000 (H)×1 000 (V) , 帧频可达48 帧/秒, 本文设计即为完成此工作模式。

为保证KAI -1020 在高帧频工作模式下的信号质量, 其内部集成了相关双采样电路。成像区在感光后, 将光信号转化为电荷包, 在驱动信号的控制下, 将电荷包转移到邻近的存储区, 依次将电荷信号转移、读出, 送入内部集成的CDS 电路采样后输出。

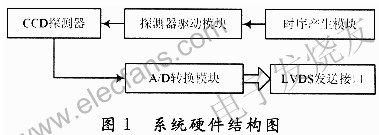

2 硬件电路设计

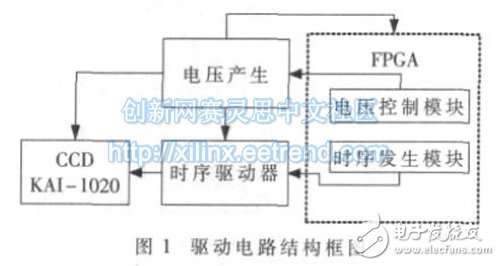

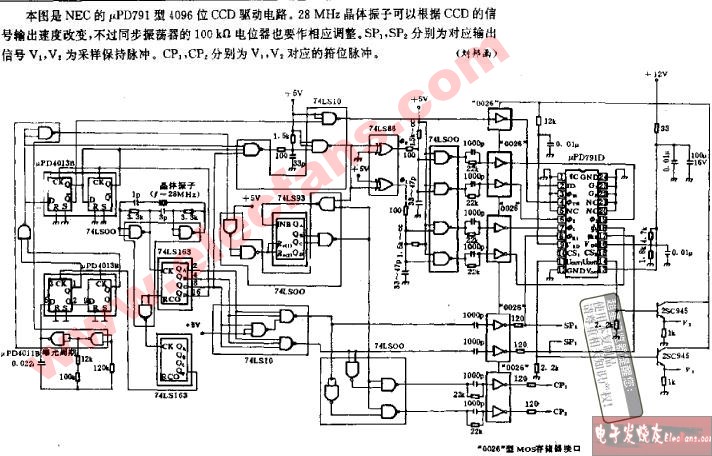

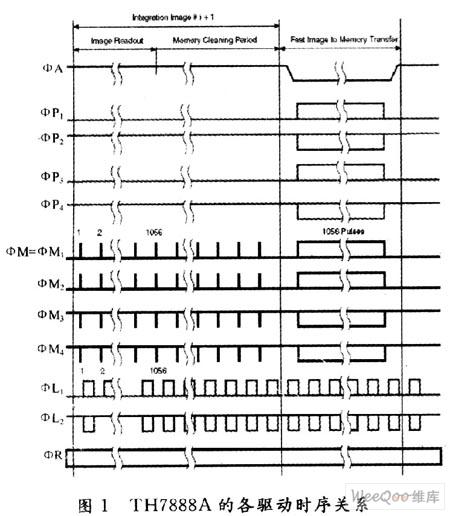

KAI-1020 工作时所需驱动信号较为复杂, 需要6 种偏置电压, 电压加载顺序也有一定要求。将驱动电路分为电压产生、FPGA 控制、时序驱动器3 个模块。电压产生模块用来产生FPGA 及CCD 工作需要的各种偏置电压;FPGA 控制模块分为电压控制模块和时序发生模块,分别用来控制CCD 电压上电顺序和CCD 驱动时序产生; 时序驱动器用来匹配FPGA 端口电压与CCD 驱动信号电压。驱动硬件结构如图1 所示。

2.1 电压产生模块

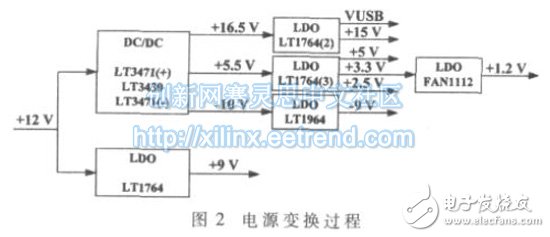

CCD 作为高精度的图像传感器, 对电源电压稳定性及电路噪声水平要求较高。DC/DC 电源效率高, 但纹波大。LDO 电源稳定性好, 但压差大时发热量也大, 会增加系统功耗及电路噪声[ 4]。

KAI -1020 因内部结构要求, 需要进行三步上电,FPGA 作为控制单元,+3.3 V、+2.5 V、+1.2 V 的工作电压需要随系统上电加载。

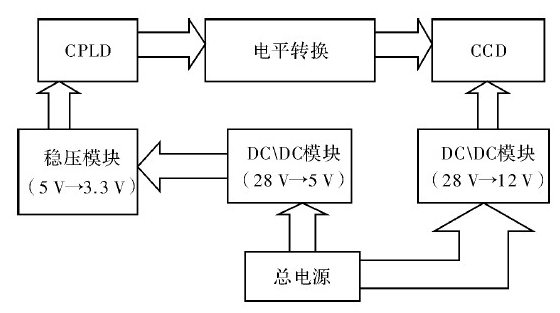

相机母线电压为+12 V, 为保证CCD 正常工作, 降低系统功耗, 减少CCD 高速工作时电压纹波及电路噪声造成的影响, 电压产生模块采用先大压差DC/DC 变换,再小压差线性稳压, 由FPGA 控制上电顺序的方案。电源模块电压变换过程如图2 所示。

2.2 FPGA 控制模块

为相机小型化考虑,FPGA 选用Xilinx 公司Spartan-3AN 系列中的XC3S400AN。XC3S400AN 资源丰富, 拥有40 万门电路和多达311 个用户I/O, 内部集成了4 Mbit Flash 作为程序存储区, 不需要外接配置芯片, 十分适合对空间敏感和安全性要求较高的场合。

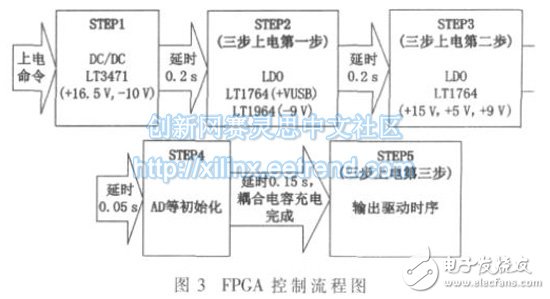

相机加电后,FPGA 完成配置, 进入工作状态, 接到上电命令后, 通过控制稳压器的使能端控制电压加载,完成CCD 三步上电。FPGA 控制流程如图3 所示。

-9 V 电压加载后,V1MID 与V1MID(-1.2 V) 通过对地串联的两个二极管导通形成。

2.3 时序驱动模块

XC3S400AN 每个BANK 都可配置管脚电压为LVTTL或LVCOMS , 但CCD 驱动时序电压为0 ~5 V, 所以需要在FPGA 与CCD 之间增加电平转换芯片。

TI 公司的SN74LV8T245 是一款8 bit 转换电压可调、输出三态、双供电总线收发器, 其内部分为AB 两路, 由DIR 控制数据流向为A 到B 或B 到A, 两路电压均可配置为1.65 V~5.5 V。将DIR 配置为1, 数据流向为A 到B,A 路接+3.3 V 电压, 接口与FPGA 驱动信号连接,B路接+5 V 电压, 接口与CCD 驱动电容连接, 完成FPGA与CCD 驱动电压的匹配。

3 软件设计

3.1 时序分析

KAI-1020 工作在逐行扫描、双通道读出模式下, 主要驱动信号有V2B、V2A、V1、H1、H2 、SH、R、SA、SB、T。V2B 为帧转移信号, 下降沿时,CCD 将感光单元中的电荷包转移到存储单元中;V2A、V1 为垂直转移信号, 负责将存储单元中每一行的电荷包转移到读出寄存器中;H1、H2 为水平转移信号, 负责将每一行中的每个像元从寄存器中读出;SH 为电子快门信号,SH 的一个高脉冲可以将CCD 之前曝光积累的电荷清零, 电荷的积累时间变为从SH 的下降沿到V2B 的下降沿, 从而实现控制曝光时间;R、SA、SB、T 为相关双采样的控制时序,R与T 同相, 与SA、SB 有一定的相位差, 其具体时序关系如图4 所示。

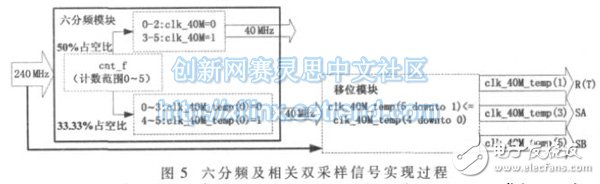

KAI-1020 驱动信号中, 水平转移信号与CDS 信号频率最高, 为40 MHz , 占空比分别为50%和33.33%, 这几个信号之间存在一定的相位关系, 通过更高频的信号分频实现。相机的工作时钟为30 MHz , 经FPGA 的DCM进行8 倍频后, 再将信号六分频并进行移位得到不同相位的40 MHz 信号。对于垂直转移信号及电子快门等低频信号, 通过对40 MHz 的信号计数分频实现。实现过程如图5 所示。

3.2 逻辑设计

KAI-1020 工作在双端口读出模式时, 左右两面的数据分左右两路读出。读出寄存器中, 左右两路各有8个空像元, 水平转移时序需要重复522 次, 才能将一行图像数据从左右两路读出。为保证读出行的电荷不对下一行电荷造成影响, 一般水平转移序列至少重复523次, 垂直转移时序需要重复1 008 次, 将1 008 行数据依次从存储区转移到读出寄存器。

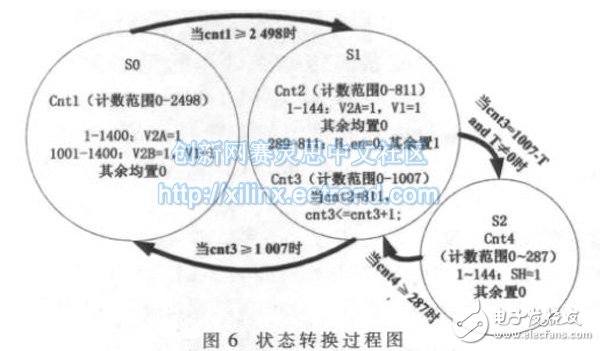

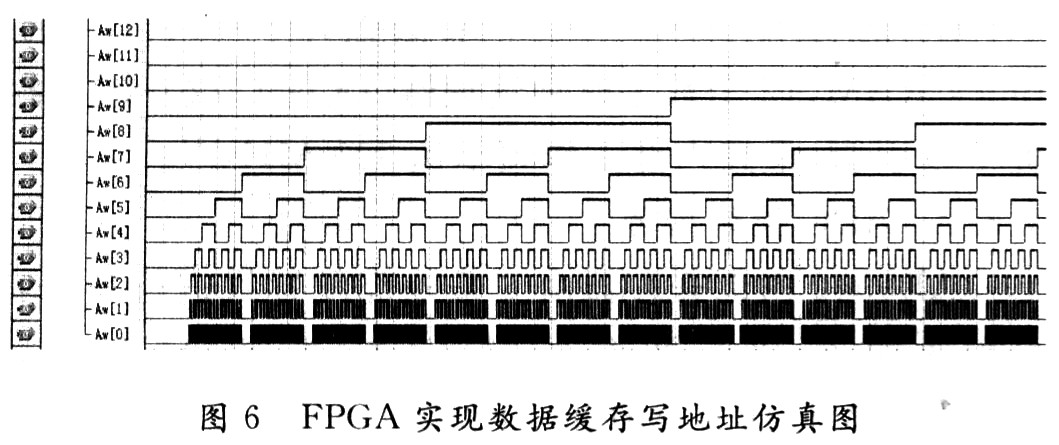

将驱动时序通过状态机实现, 帧转移由状态s0 表示, 垂直转移和水平转移由s1 表示, 通过计数器计数完成延时要求, 状态转换过程如图6 所示。

在垂直转移信号变化时, 水平转移信号H1、H2 需要分别保持高电平和低电平。在状态s1 中, 设置信号H_en , 通过将H_en 与40 MHz 信号进行“ 或” 运算, 得到H1 信号, 将H_en 与40 MHz 信号“ 或” 运算后再取反, 得到H2 信号。

电子快门信号SH 需要加载于某行电荷信号读取完成后,V1 与V2A 信号上升沿之前,H1、H2 在此期间需要保持变化。当计数器cnt3 计到曝光所需的行数T 后,状态机跳转到状态s2 , 完成SH 信号延时后跳转回s1 ,实现电子快门1-1007 级可调。

3.3 逻辑仿真

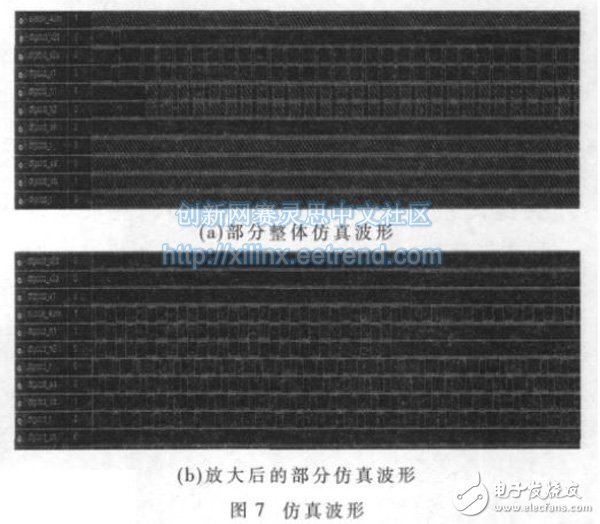

通过时序分析, 采用VHDL 语言进行程序设计, 在Xilinx 公司的集成开发环境ISE 10.1 中编写源代码, 并进行仿真, 仿真波形如图7 所示。

图7(a) 为整体仿真波形的一部分,V2B、V2A、V1 在帧转移阶段完成后,V2B 保持低电平,V2A、V1 开始重复; 图7(b) 为水平转移信号与相关双采样信号的部分仿真波形,H1、H2 反相,R、SA、SB、T 相位关系与时序要求相同,当V2A、V1 变化时,H1 为高电平,H2 为低电平。

4 实验结果

在仿真通过后,对VHDL 源代码进行综合和实现, 生成可编程文件, 将该文件下载到FPGA 后, 控制CCD 产生图像信号, 经过后端处理电路, 将模拟图像信号转化为数字信号, 并对两路输出的图像信号进行拼接, 形成一行图像, 通过高速串行LVDS 信号将图像信号发送至数据接收端, 解码LVDS 信号, 通过采集卡在上位机形成图像。经实际成像测试,CCD 在设计的软硬件驱动下,帧频可达48 帧/秒, 图像分辨率为1 000 (H)×1 000 (V) ,并能通过电子快门对曝光时间进行1-1007 级调节, 灵活控制图像亮度。

使用FPGA 作为CCD KAI-1020 的控制单元及时序发生器, 可以十分方便地产生各种控制及驱动信号, 完成CCD 上电顺序控制及复杂驱动时序产生, 其强大的可编程和并行处理能力也十分利于系统扩展和升级。

电子发烧友App

电子发烧友App

评论