分频器是数字系统设计中的基本电路,根据不同设计的需要,我们会遇到偶数分频、奇数分频、半整数分频等,有时要求等占空比,有时要求非等占空比。在同一个设计中有

2010-09-03 17:04:20 2442

2442

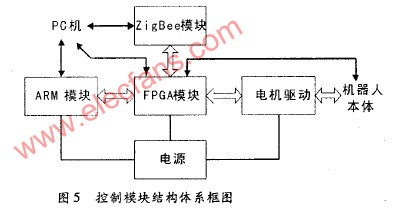

本文介绍的FPGA一体化高级设计方法是通过发挥 FPGA 主机的可再编程功能实现的。所有应用的层和接口以及功能设计本身都自动包含在 FPGA 系统中

2011-12-20 09:57:09 794

794 在FPGA中,我们怎么实现除法操作?最简单的方法当然是调IP Core。在Divider Generator的IP Core中,我们可以选择有/无符号数进行除法,还可以选择除法的延迟。当然,延迟越小

2020-12-24 16:06:22

FPGA数字信号处理实现原理及方法

2012-08-15 19:00:58

FPGA数字信号处理实现原理及方法

2012-08-19 13:37:35

本帖最后由 eehome 于 2013-1-5 09:47 编辑

周立功EASYFPGA原理图周立功大师经典力作,FPGA原理图。欢迎大家下载学习周立功大师EASY FPGA原理图

2012-03-16 11:02:04

本帖最后由 eehome 于 2013-1-5 09:53 编辑

周立功:如何兼顾学习ARM与FPGA

2012-08-19 23:31:12

咨询一个问题:CH34X系列USB转串口芯片的波特率分频方式只有整数分频?还是有小数分频?例如CP210x芯片的波特率生成只有整数分频,为48 MHz/(2 × Prescale × n),生成

2022-07-07 07:09:19

前言本文介绍STM32与FPGA通过fsmc通信的实现方法。一、fsmc介绍FSMC(Flexible Static Memory Controller,可变静态存储控制器)是STM32系列采用

2022-01-18 06:32:19

摘要:为了实现对非相干雷达的接收相参处理,基于数字稳定校正(DSU)的原理,采用ALTERA公司的StratixⅡ系列芯片和VHDL编程语言,设计了一种基于FPGA的DSU硬件实现方法。实验结果表明

2019-06-28 08:27:33

的UART的实现方法,具体描述了发送、接收等模块的设计,恰当使用了有限状态机,实现了FPGA片上UART的设计,给出了仿真结果。关键词:通用异步收发器;串口通信;现场可编程逻辑器件;有限状态机

2019-06-21 07:17:24

处理等方面受到了限制,由于FPGA中关于浮点数的运算只能自行设计,因此,研究浮点加法运算的FPGA实现方法很有必要。

2019-07-05 06:21:42

大家好,我想在Artix fpga上实现TMRmodule。经过一番搜索,似乎隔离设计流程(IDF)是一种很好的方法。我是以正确的方式吗?如果“是”,请帮我一个示例,告诉我如何为IDF准备我的设计。如果“不”请给出一些想法。谢谢

2020-08-17 10:49:06

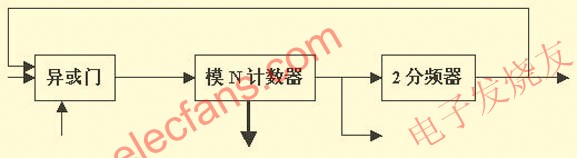

【摘要】:介绍了基于FPGA的任意分频系数的分频器的设计,该分频器能实现分频系数和占空比均可以调节的3类分频:整数分频、小数分频和分数分频。所有分频均通过VHDL语言进行了编译并且给出了仿真图。本

2010-04-26 16:09:01

双模前置小数分频原理是什么?如何对小数分频器进行仿真测试?

2021-04-29 07:29:41

小数分频器整数边界杂散问题的提出小数分频器整数边界杂散的优化设计

2021-04-19 08:32:15

如何将ip地址转成整数?ip地址的整数类型转成ip地址怎么实现?

2021-11-22 06:36:05

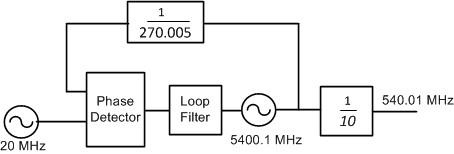

要设计小数分频PLL,基本架构已经确定:使用基于MASH111的DSM,双模预分频器+PScounter实现。现在遇到的问题是,不知道怎么把小数分频控制字经过DSM后的输出与整数分频控制字结合起来去控制(双模分频器+PScounter)可编程分频器此前没做过小数分频PLL,求助大佬们点拨一二

2021-06-24 07:20:38

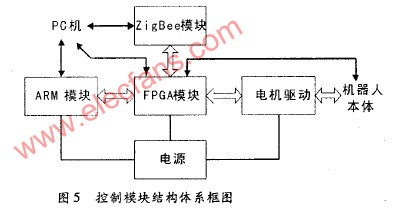

周学习FPGA的使用控制方法。在ISE和Modelsim环境下实现对FPGA的控制。第13周~第16周整理前期工作,测试人机交互界面的功能。撰写总结报告及毕业论文和翻译。

2014-03-16 23:39:13

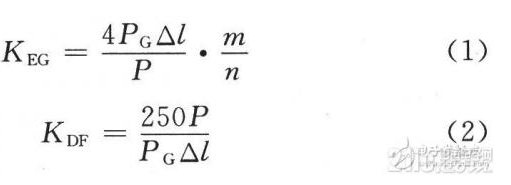

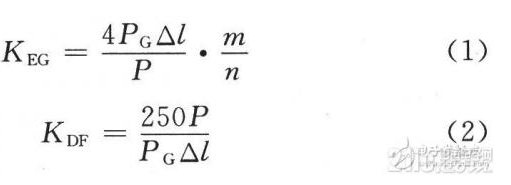

什么是电子齿轮比与分周比?分周比的结构是怎样构成的?

2021-04-29 06:11:55

使用VHDL语言怎样实现数控半整数分频器,就当输入为3时,就实现3.5分频,当输入为4时,就实现4.5分频,同时要求占空比为50%。

2014-12-02 18:28:57

成像技术中采集信号的周期是由发送信号的周期决定, 而对于其他复杂周期信号的周期获得可以通过所采用的方法获得。等效时间采样技术的原理作用及采用FPGA器件实现系统的设计图2 系统方案框图2.2 等效时间

2020-10-21 16:43:20

在复杂数字逻辑电路设计中,经常会用到多个不同的时钟信号。介绍一种通用的分频器,可实现2~256 之间的任意奇数、偶数、半整数分频。首先简要介绍了FPGA 器件的特点和应用范

2009-11-01 14:39:19 78

78 提出了一种基于FPGA 实现QPSK 调制器的方法。以FPGA 实现DDS,通过对DDS 信号输出相位的控制实现调相。仿真结果表明方案是可行的。

2009-12-18 11:57:08 66

66 NandFlash控制器的FPGA实现方法技巧与程序案例分享。

2017-09-21 09:40:00 78

78 基于FPGA的DDS信号源设计与实现

利用DDS和 FPGA 技术设计一种信号发生器.介绍了该信号发生器的工作原理、 设计思路及实现方法.在 FPGA 器件上实现了基于 DDS技

2010-02-11 08:48:05 223

223 基于FPGA 的等占空比任意整数分频器的设计

给出了一种基于FPGA 的等占空比任意整数分频电路的设计方法。首先简要介绍了FPGA 器件的特点和应用范围, 接着讨论了一

2010-02-22 14:22:32 39

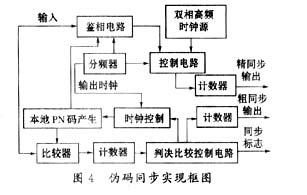

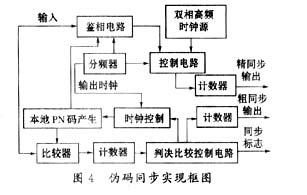

39 本文主要阐述了在某雷达系统中为实现伪码对齐,所采用的滑动控制方法的原理及在FPGA芯片上的实现。

2010-03-02 16:04:22 13

13 简要介绍了CPLD/FPGA器件的特点和应用范围,并以分频比为2.5和1.5的分频器的设计为例,介绍了在MaxPlusII开发软件下,利用VHDL硬件描述语言以及原理图的输入方式来设计数字逻辑电路的过

2010-07-17 17:55:57 36

36 乘累加器在DSP算法中有着举足轻重的地位。现在,很多前端DSP算法都通过FPGA实现。结合FPGA具体的硬件结构,提出了乘累加器在FPGA中实现的改进方法:流水线技术、CSD编码、DA算法,

2010-08-06 14:41:38 29

29 摘要:简要介绍了CPLD/FPGA器件的特点和应用范围,并以分频比为2.5的半整数分频器的设计为例,介绍了在MAX+plus II开发软件下,利用VHDL硬件描述语言以及原理图的输

2006-03-13 19:36:44 869

869

【摘 要】 介绍了基于伪码测距的某定位系统的设计方案,简要分析了伪码测距的原理,研究了用FPGA实现伪码的捕获与跟踪的方法。

2009-05-14 20:58:06 720

720

摘 要: 本文通过在QuartursⅡ开发平台下,一种能够实现等占空比、非等占空比整数分频及半整数分频的通用分频器的FPGA设计与实现,介绍了利用VHDL硬件描

2009-06-20 12:43:07 562

562

摘要:简要介绍了CPLD/FPGA器件的特点和应用范围,并以分频比为2.5的半整数分频器的设计为例,介绍了在MAX+plus II开发软件下,利用VHDL硬件描述语言以及原理图的输

2009-06-20 12:45:00 627

627

整数的表示方法

整数表示的数据的最小单位为1,可认为它是小数点定在数值最低位右面的一种数据。

2009-10-13 17:12:56 3871

3871 整数的编码方法

与定点小数的三种编码方法类似,整数也可以用原码、补码和反码三种不同的编码方法表示。区别主要表现在:

2009-10-13 17:19:26 5234

5234 用 FPGA 嵌入式处理器实现您的构想

在采用数值处理技术创建嵌入式应用时,通常以整数或定点表示法来确保算术运算尽量简单,这一点至关重要。因其不仅有助于使成本和

2009-11-05 16:28:48 882

882

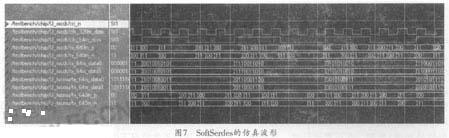

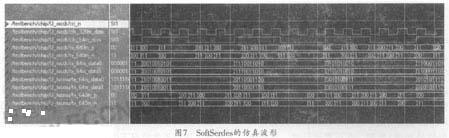

基于FPGA的SoftSerdes设计与实现

0 引言

在高速源同步应用中,时钟数据恢复是基本的方法。最普遍的时钟恢复方法是利用数字时钟模块(DCM)

2009-12-28 09:23:40 920

920

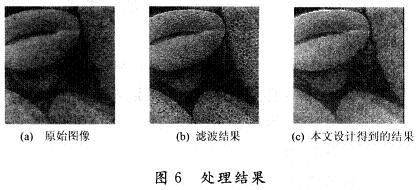

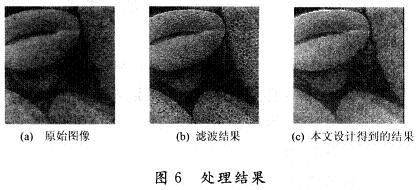

拉普拉斯算子的FPGA实现方法

引 言

在图像处理系统中常需要对图像进行预处理。由于图像处理的数据量大,对于实时性要求高的系统,采用软件实现通常

2010-02-11 11:01:22 1376

1376

摘要:文中详述了FPGA被动串行配置方式的时序,给出配置流程图及实现的程序代码,并通过实例验证了该方法的优越

2010-07-21 14:48:48 1326

1326

利用FPGA实现时分多址的方法有很多种,但大多数方法都对FPGA芯片资源的占用非常巨大。针对这一问题,提出一种改进型方法来实现时分多址。通过使用FPGA芯片内部的双口随机访问存储器(双口RAM),利用同一块RAM采用两套时钟线,地址线和数据线,例化双口RAM的

2011-01-15 15:41:26 29

29 给出了一种小数分频技术的实现方法, 并在实验的基础上进一步证实了小数分频的可行性该法通过微机控制,

2011-02-22 14:58:54 45

45 提出了一种基于FPGA的小数分频实现方法,介绍了现有分频方法的局限性,提出一种新的基于两级计数器的分频实现方法,给出了该设计方法的设计原理以及实现框图

2011-11-09 09:36:22 121

121 给出了一种基于FPGA的分频电路的设计方法.根据FPGA器件的特点和应用范围,提出了基于Verilog的分频方法.该方法时于在FPGA硬件平台上设计常用的任意偶数分频、奇数分频、半整数分频

2011-11-09 09:49:33 355

355 本文提出了一种用FPGA实现纠错编码的设计思想,并以Altera MAX+PluslI为硬件开发平台。利用FPGA编程的特点,用软件编程方法,很好的解决了纠错编码中存在的码速变换和实时性问题,实现

2011-11-10 17:10:59 61

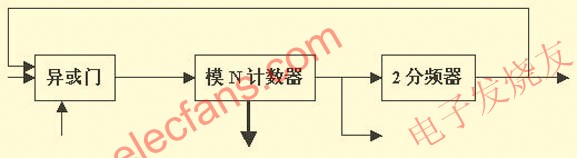

61 介绍了一种基于FPGA的双模前置小数分频器的分频原理及电路设计,并用VHDL编程实现分频器的仿真.

2011-11-29 16:43:06 48

48 LMX2531 系列产品被广泛应用于无线通讯基站系统,相比较整数分频,采用小数分频可以获得更好的相位噪声性能,但是小数分频会导致杂散问题,特别是整数边界杂散尤为突出。本文介绍一种在尽可能保证相位噪声性能的基础上,改善整数边界杂散达10dB。

2013-04-27 15:51:04 2619

2619 一种线性调频信号参数分析的综合方法,下来看看。

2016-01-15 15:17:24 10

10 用 Verilog实现基于FPGA 的通用分频器的设计时钟分频包括奇数和偶数分频

2016-07-14 11:32:47 45

45 三目立体视觉外极线校正及其FPGA实现方法

2016-09-17 07:30:24 16

16 面向特种LCD图像处理方法与FPGA实现研究,感兴趣的小伙伴们可以看一看。

2016-09-18 14:55:04 27

27 华清远见FPGA代码-整数DCT变换的设计与实现

2016-10-27 18:07:54 8

8 基于HEVC整数DST的VLSI设计与实现_杜高明

2017-01-03 17:41:32 0

0 非整数倍路径时延下的OMP信道估计方法_王东梅

2017-01-07 16:00:43 0

0 一种基于FPGA的E1数字传输分析仪成解帧实现方法_耿立华

2017-03-14 16:50:00 2

2 基于DSP的FPGA配置方法研究与实现

2017-10-19 16:15:19 36

36 本文详细介绍了完整数据采集系统的硬件的构建方法。

2017-11-15 14:35:34 20

20 的使用,同时以整数数据处理方式实现了向导滤波器中方差和变换系数的计算,并且通过参数调整,可以方便地实现不同大小图像的不同尺寸窗口的向导滤波。在Altera公司Cyclone系列FPGA芯片上进行了综合,实验结果表明,向导滤波整数FPGA结构的处理结果与

2017-11-22 15:43:12 12

12 研究了具有零相关区的高斯整数序列集构造方法。该方法基于二元正交矩阵,首先利用插零法构造出具有零相关区的三元序列集。然后利用完备高斯整数序列进行滤波,从而将三元序列变换成高斯整数序列且保持序列相关函数

2018-01-10 16:33:55 0

0 三分频,五分频,七分频等等奇数类分频,那究竟怎么办呢?在这里,让我介绍一个可以实现任意整数分频的方法,这个办法也是同样利用了计数器来计算,当是跟偶数分频不一样的地方是任意整数分频利用了两个计数器来实现。 设计原理 : 本

2018-06-13 11:21:48 12390

12390

脉冲按照一定的比例,即分周比进行分频。分频的难点是,无论设定分周比是整数还是分数,分频后输出的A‘相,B’相脉冲仍然要保持正交或近似正交。为此提出一种基于FPGA的整数分周比实现方法。该方法逻辑结构简单,配置灵活,易于扩展,具有很高的实用价值。

2018-11-20 09:39:03 1068

1068

在此Xilinx研究实验室演示中,解释了单源SYCL C ++示例以及生成在Xilinx FPGA上运行的硬件实现的方法。

2018-11-20 06:30:00 2918

2918 建立了一个基于FPGA的可实现流水化运行的OFDM系统的硬件平台,包括模拟前端、基于FPGA的OFDM调制器和OFDM 解调器。重点给出了OFDM调制解调器的实现构架,对FPGA实现方法进行了详细的描述,介绍了系统调试方法,并对系统进行了性能评价。

2018-12-13 16:45:51 22

22 分频器主要分为偶数分频、奇数分频、半整数分频和小数分频,如果在设计过程中采用参数化设计,就可以随时改变参量以得到不同的分频需要。

2019-02-01 01:28:00 15719

15719

针对高速运动平台弹速补偿的实时性要求,在基于距离徙动校正(Range Cell Migration Compensation,RCMC) 的思想上提出了一种弹速补偿的FPGA实现方法。将距离徙动校正

2019-03-30 09:56:14 2287

2287

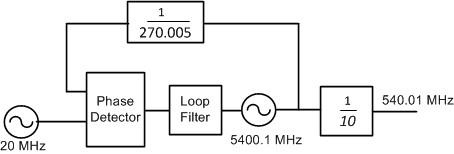

分频器是一种基本电路,通常用来对某个给定频率进行分频,得到所需的频率。整数分频器的实现非常简单,可采用标准的计数器,也可以采用可编逻辑器件设计实现。但在某些场合下,时钟源与所需的频率不成整数倍关系,此时可采用小数分频器进行分频。

2019-11-20 07:05:00 6652

6652 论文分析了双模前置小数分频器的分频原理和电路实现。结合脉冲删除技术,提出了一种适于硬件电路实现的任意小数分频的设计方案 ,用 VerilogHDL语 言编程 ,在 QuartusII下对 此方案进 行 了仿 真 ,并用 Cyclone 系 列 的 EP1C12Q240C8芯 片来 实 现 。

2019-08-02 08:00:00 5

5 讨论了利用FPGA工具实现MBUS总线的原理、方法,以实际操作介绍了FPGA设计流程,并给出FPGA常用设计技巧。

2019-12-24 14:54:08 9

9 在数字系统设计中,根据不同的设计需要,经常会遇到偶数分频、奇数分频、半整数分频等,有的还要求等占空比。在基于cpld(复杂可编程逻辑器件)的数字系统设计中,很容易实现由计数器或其级联构成各种形式的偶数分频及非等占空比的奇数分频,但对等占空比的奇数分频及半整数分频的实现较为困难。

2020-06-26 09:36:00 825

825

的实现方法,具体描述了发送、接收等模块的设计,恰当使用了有限状态机,实现了FPGA上的UART的设计,给出仿真结果。

2020-07-07 17:28:03 10

10 为了满足整数小波变换实时应用的需要,研究了整数小波变换的FPGA实现问题。相对于DSP等传统实现方式,用FPGA实现整数小波变换具有处理速度快,可重新配置硬件,易于修改移植等优点。论文首先描述了二维

2021-02-01 11:53:33 9

9 基于小波变换的滤波方法应用于红外图像处理中可以在降低噪声的同时提升图像细节,有效改善图像画质。介绍了一种采用FPGA的小波图像处理方法及其硬件处理架构。通过合理有效地进行算法硬件设计,在单片FPGA芯片上实现了图像的实时处理,有利于红外机芯的小型化。

2021-02-01 14:54:00 5

5 因为偶数分频器过于简单,所以我们从奇数分频器开始说起8 01 奇数分频器 假设我们要实现一个2N+1分频的分频器,就需要高电平占N+0.5个周期,低电平占N+0.5个周期,这样进行处理的最小

2021-03-12 15:44:54 5614

5614

简要介绍了CPLD/FPGA器件的特点和应用范围,并以分频比为2.5和1.5的分频器的设计为例,介绍了在MaxPlusII开发软件下,利用VHDL硬件描述语言以及原理图的输入方式来设计数字逻辑电路的过程和方法。该设计具有结构简单、实现方便、便于系统升级的特点。

2021-03-16 09:45:53 10

10 简要介绍了 CPLD/FPGA器件的特点和应用范围,并以分频比为2.5和15的分频器的设计为例,介绍了在 Maxplusll开发软件下,利用ⅤHDL硬件描述语言以及原理图的输入方式来设计数字逻辑电路的过程和方法。该设计具有结构简单、实现方便、便于系统升级的特点。

2021-03-22 16:52:15 5

5 整数上的离散高斯取样是格密码体制实现的基本操作,也是决定安全性的重要因素,但可能受到计时攻击从而造成秘密信息的泄漏。为此,在 Knuth-Yao算法的基础上,提出一种整数上离散高斯取样的常数时间实现

2021-03-24 16:30:13 6

6 简要介绍了CPLD/FPGA器件的特点和应用范围,并以分频比为25和15的分频器的设计为例,介绍了在 Maxplus开发软件下,利用VHDL硬件描述语言以及原理图的输入方式来设计数字逻辑电路的过程和方法该设计具有结构简单、实现方便、便于系统升级的特点。

2021-04-12 16:29:05 11

11 基于FPGA的神经网络硬件实现方法说明。

2021-06-01 09:35:16 37

37 基于CPLD/FPGA的半整数分频器设计方案

2021-06-17 09:37:02 21

21 基于新型FPGA的FFT设计与实现设计方法。

2021-06-17 17:07:03 42

42 2.3 python整数与浮点数 Python 支持的数字类型有三种:整数、浮点数和复数。 1. 整数(Int) 通常被称为整型,是正或负整数,不带小数点。例如:1,100,-8080,0,等等

2022-02-18 09:09:53 1570

1570 摘要:在对FFT(快速傅立叶变换)算法进行研究的基础上,描述了用FPGA实现FFT的方法,并对其中的整体结构、蝶形单元及性能等进行了分析。

2022-04-12 19:28:25 4515

4515 时序至关重要:改善分数分频锁相环合成器中的整数边界杂散状况

2022-11-04 09:50:31 1

1 整数在 IEEE 的规定上有短整数 short integer , 中整数 integer 和 长整数 long integer

2023-02-13 15:00:13 1144

1144 所谓“分频”,就是把输入信号的频率变成成倍数地低于输入频率的输出信号。数字电路中的分频器主要是分为两种:整数分频和小数分频。其中整数分频又分为偶分频和奇分频,首先从偶分频开始吧,入门先从简单的开始!

2023-03-23 15:06:22 948

948

前面分别介绍了偶数和奇数分频(即整数分频),接下来本文介绍小数分频。

2023-03-23 15:08:04 658

658

初学 Verilog 时许多模块都是通过计数与分频完成设计,例如 PWM 脉宽调制、频率计等。而分频逻辑往往通过计数逻辑完成。本节主要对偶数分频、奇数分频、半整数分频以及小数分频进行简单的总结。

2023-03-29 11:38:40 3108

3108

您曾设计过具有分数频率合成器的锁相环(PLL)吗?这种合成器在整数通道上看起来很棒,但在只稍微偏离这些整数通道的频率点上杂散就会变得高很多,是吧?如果是这样的话,您就已经遇到过整数边界杂散现象了 —— 该现象发生在载波的偏移距离等于到最近整数通道的距离时。

2023-04-18 09:29:56 687

687

上一篇文章时钟分频系列——偶数分频/奇数分频/分数分频,IC君介绍了各种分频器的设计原理,其中分数分频器较为复杂,这一篇文章IC君再跟大家聊聊分数分频的具体设计实现。

2023-04-25 14:47:44 1028

1028

是用于满足设计的需求。 分频:产生比板载时钟小的时钟。 倍频:产生比板载时钟大的时钟。 二:分频器的种类 对于分频电路来说,可以分为整数分频和小数分频。 整数分频:偶数分频和奇数分频。 小数分频:半整数分频和非半整数分频。 三:分频器的思想 采用计数器的思想实

2023-11-03 15:55:02 471

471

锁相环整数分频和小数分频的区别是什么? 锁相环(PLL)是一种常用的电子电路,用于将输入的时钟信号与参考信号进行同步,并生成输出信号的一种技术。在PLL中,分频器模块起到关键作用,可以实现整数分

2024-01-31 15:24:48 312

312

正在加载...

电子发烧友App

电子发烧友App

评论