一、计算机并口操作模式概述

1.SPP模式

SPP(Standard Parallel Port)模式即标准并口模式,是为打印输出而设计的。数据由计算机单向输出,不能用数据线进行数据输入,要做数据输入只能利用状态线。并口状态线只有5根,所以每个字节要分两次输入,再拼装为一个完整的字节。SPP模式速度较低,对硬件的要求不高,适用于低速的应用场合,如打印机、软件狗等。

2.PS/2模式

IBM公司引进了PS/2设计后开始支持并口的双向数据传输。PS/2模式和SPP模式兼容。它没有改变标准并口的信号定义,也没有改变并口接插件的引脚定义,而是通过一个方向控制位来设置并口的数据方向:如果设置为输出,PS/2模式就和SPP模式完全相同;如果设置为输入,则从并口数据线上每次可以读取一个字节的数据。同时,PS/2模式的总线控制功能提高了并口的速度。

无论是SPP模式还是PS/2模式,数据通信信度都不高。原因在于并口本身的I/O速度不高(只有100~400KB/s)。另一方面,每次数据传输都要通过I/O操作进行软件数据交换。通常情况下,一次互锁数据交换的数据传输至少需要5次I/O操作,才能保证进序的完整性。这两方面因素使SPP模式和PS/2模式只能用于速度较低的应用领域。

3.EPP模式

EPP(Enhanced Parallel Port)增强并口模式支持并口和外设间的双向数据交换,速度能够达到1~2MB/s。增强并口通过精密的逻辑界面和明确定义的电气参数保证了数据传输的速度和准确性。

4.ECP模式

ECP(Extended Capabilities Port)模式,即扩展功能和模式,其性能更高。ECP模式有16个字节的FIFO,并且支持DMA功能。在不降低系统性能的前提下减轻计算机CPU的负担,提高了应用系统的整体性能。更为重要的是,ECP模式把其他几种并口模式都纳入了ECP模式的定义中。ECP模式定义了ECR扩展控制寄存器,可以把并口的操作模式设置为SPP,PS/2,EPP或者ECP,从而构成一个完整的并口系统。

SPP模式、PS/2模式和EPP模式都是主从式结构,数据传输双方是一种不对等的关系。数据传输只能由计算机来启动,外设不能启动数据传输。如果外设要进行数据传输,它只能向计算机提出中断申请,然后由计算机启动数据传输。ECP模式则不是主从式结构,数据传输的双方都可以启动数据传输。ECP模式可以用于计算机之间的互联,而EPP模式则不能。

虽然ECP并口模式的性能比EPP高,但是ECP模式不太容易实现,大部分的设计者都采用了EPP模式来设计自己的应用系统。EPP模式比ECP模式更简洁,灵活,可靠,在工业界得到了更多的实际应用。

二、EPP增强并口的实现方案

1.EPP增益并口时序

EPP协议定义了4种并口周期:数据写周期、数据读周期、地址写周期和地址读周期。数据周期用于计算机和外设间传送数据;地址周期用于传送地址、通道、命令、控制和状态等辅助信息。图1是EPP数据写的时序图,图中的nIOW信号实际上在进行EPP数据写时并不会产生,只不过是表示所有的操作都发生在一个I/O周期内。在t1时刻,计算机检测nWAIT信号,如果nWAIT为低,则表明外设已经准备好,可以启动一个EPP周期了。在t2时刻,计算机把nWRITE信号置为低,表明是写周期,同时驱动数据线。在t3时刻,计算机把nDataStrobe信号置为低,表明是数据周期。外设在检测到nDataStrobe为低后读取数据并做相应的数据处理。在t4时刻把nWAIT置为高,表明已经读取数据,计算机可以结束该EPP周期。在t5和t6时刻,计算机把nDataStrobe和nWRITE置为高。这样,一个完整的EPP数据写周期就完成了。图1中的nDataStrobe信号如果换为nAddStrobe信号,就是EPP地址写周期。图2是EPP地址读周期。与EPP写周期类似,只不过是由外设来驱动数据线。

EPP时序还包括初始化、中断申请等,可以查阅参考文献1获得详细的时序图及时序说明。

2.EPP增益并口的逻辑界面

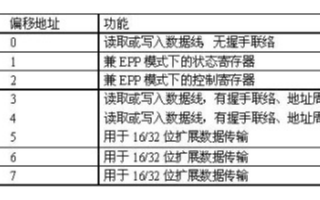

EPP增强并口模式使用与标准并口模式相同的基地址,定义了8个I/O地址。基地址+0是SPP数据口,基地址+1是SPP状态口,基地址+2是SPP控制口。这3个口实际上就是SPP模式下的数据、状态和控制口,这样保证了EPP模式和SPP模式的软硬件兼容性。

基地址+3是EPP地址口,向这个I/O口中写数据将产生一个连锁的EPP地址写周期,从这个I/O口中读数据将产生一个连锁的EPP地址读周期。在不同的EPP应用系统中,EPP地址口可以根据实际需要设计为设备选择、通道选择、控制寄存器、状态信息等,给EPP应用系统提供了极大的灵活性。

基地址+4是EPP数据口,向这个I/O口中写数据将产生一个连锁的EPP数据写周期,从这个I/O口读数据将产生一个连锁的EPP数据读周期。 基地址+5~+7与基地址+4一起提供地EPP数据口的双字操作能力。EPP允许主机在1个时钟周期内写1个32位双字,EPP电路再把32位双字拆为4个字节依次从EPP数据口中送出去。也可以用16位字方式进行数据传送。

3.EPP增强并口外设的硬件实现方案

EPP增强并口的速度可以达到1~2MB/s,这对外设的接口设计提出了一个很高的要求。如果外设响应太慢,则系统的整体性能将大大下降。EPP接口设计方案是整个EPP应用系统整体性能的关键。

(1)门电路实现

这种实现方案可以实现基本的接口,但是无法对地址周期作出具体的处理。门电路实现方案的最大缺点是缺乏基本的灵活性,并且没有任何的保密措施。设计方案的任何改动都要重新设计整个接口系统。因此,不推荐使用这种实现方案。

(2)可编程逻辑器件实现

用户可编程逻辑器件如FPGA和CPLD可以实现EPP增强并口的接口设计。这种实现方案可以达到并口的速度极限,并且提供了很大的灵活性。FPGA容量大、功耗低、寄存器资源丰富,可以把EPP应用系统的其他复杂接口和控制都做在一个芯片中。缺点是每次使用前FPGA都需要配置,并且FPGA抗干扰能力差,在恶劣的环境中容易丢失配置信息。CPLD容量较小,功耗较大,寄存器资源匮乏,可以实现EPP接口及一些不太复杂的接口和控制功能。CPLD用EEPROM或者FLASH来保存配置信息,掉电不丢失。可编程逻辑器件是EPP应用系统优先选用的实现方案。

(3)DSP实现

DSP的指令周期短,CPU运行速度快,也可以用来实现EPP增强并口的接口设计。但是DSP本身是用来做运算的,接口控制指令的运行效率不高,接口速度不如可编程逻辑器件实现方案的速度。如果EPP应用系统要求有比较强的运算能力,用DSP来实现整个应用系统的接口和运算功能是一个比较合适的选择。

(4)单片机实现

用单片机来实现EPP接口似乎有些不可思议,因为单片机的速度比较慢,并且指令的执行是串行的,不能像CPLD或者FPGA那样把一个大任务分成几个独立的小任务并行处理。作者原来一直用可编程逻辑器件实现EPP接口设计,认为单片机不可能实现EPP接口设计。在了解了Motorola公司的68HC908GP32(简称GP32)单片机卓越的超频性能后才用GP32单片机实现EPP接口设计。实践表明,GP32单片机可以很好地完成EPP接口任务,性能完全能够满足计算机和外设双方的要求。GP32单片机丰富的外高和高效率的I/O指令系统弥补了速度慢的不足。如果考虑一个EPP应用系统的整体功能,用单片机来实现接口和控制功能是性价比最高的实现方案。

三、用68HC908GP32单片机实现EPP接口设计

1.68HC908GP32单片机功能概述

68HC908GP32是Motorola公司1999年推出的68HC08系列单片机。GP32采用68HC08CPU,其性能是68HC05CPU的5~10倍。GP32有32KB的FLASH闪速存储器,具有在线编程能力和超强的保密功能;有512字节的RAM、增强型串行通信口SCI、串行外设接口SPI;有两个16位双通道定时器接口,每个通道可以选择为输入捕获、输出比较或PWM,其定时时钟可为内部总线的1,2,4,8,16,32和64分频;有8路8位A/D转换器、8位键盘唤醒口、29根通用I/O引脚。系统保护特性为:计算机工作正常(COP)复位、低压检测复位、非法指令检测复位及非法地址检测复位。

2.GP32的时钟发生模块

GP32有时钟发生模块,利用32kHz晶振和片内PLL(锁相环)电路可以产生高达19.5MHz的工作频率。一般的单片机不能超频运行,否则会因为读代码错误、代码运行错误、芯片发热等因素导致芯片不能正常运行,频繁死机,甚至会烧毁芯片。GP32的CPU正常情况工作在8MHz频率下,但是在2.4倍额定频率下还能够稳定运行。作者做过一个实验,GP32工作在19.5MHz下,在实验室环境中稳定运行了90h,在电力系统动态模拟实验室的直流发电机电刷附近稳定运行了90min,运行过程中没有出现过意外的死机现象。实验表明,GP32单片机是可以长期超频工作的。

3.用GP32单片机实现EPP增强并口的接口设计

EPP增强并口定义了8根数据线、2根状态线和3根控制线。用GP32的双向I/O线可以直接和EPP的信号线相连,GP32单片机有足够的驱动能力来驱动并口信号。

软件设计是用GP32单片机实现EPP接口设计的关键。为了保证通信速度,必须对GP32单片机的指令进行优化,选择那些执行速度快的指令;同时采用合理的数据流控制方法,既要保证通信的快速性,又要保证通信数据的正确性。例如,以数据包的方式传送大批量的数据,并以数据包为单位处理数据。

在19.5MHz的工作频率下,GP32实现的EPP增强并口可以达到400KB/s的通信速度。如果降低GP32的工作频率,则通信速度成比例地降低,但是最低不能低于100B/s,否则会因外设响应太慢而导致通信失败。

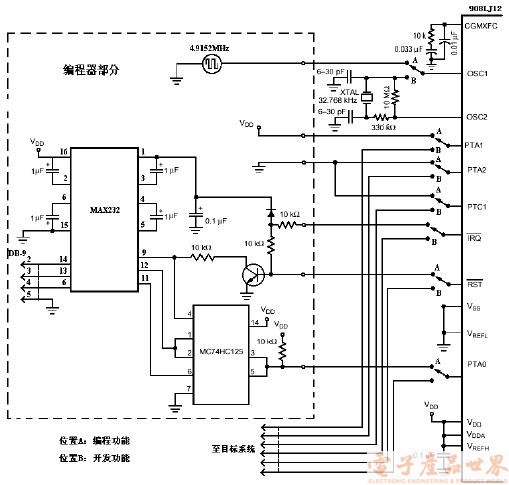

四、用GP32单片机实现的数据采集板

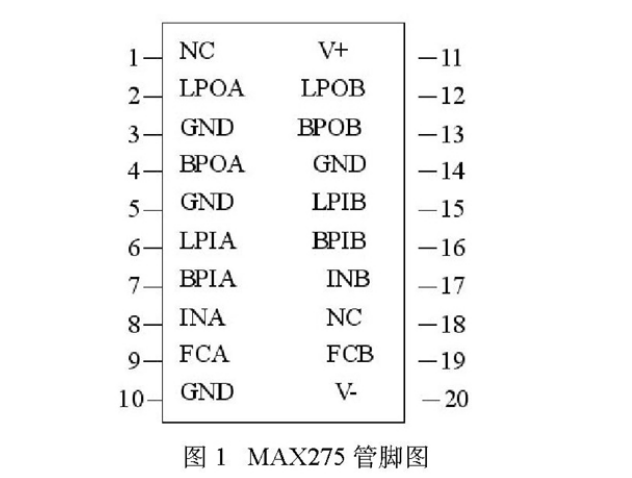

GP32单片机有8路8位的AD转换器,可以胜任一些要求低采样速度、低分辨率的应用场合。作者设计了一个采用GP32单片机实现的数据采集系统,电路图如图3所示。U1是GP32单片机,JAD是模拟信号输入接口,PARAPORT是并口,C1,C2,C3,X1,RB是Rs一起构成了GP32单片机锁相环电路。

通过计算机可以设置A/D转换的通道、启动条件,能够启动或者停止A/D采样。GP32有512字节的片内RAM,其中的384字节设定为A/D转换的缓冲器,其余的RAM用做堆栈和变量。如果A/D转换缓冲器已经满256字节,则GP32单片机向计算机发送一个中断,计算机用EPP并口协议读取A/D转换的数据。

计算机中由一个硬件驱动程序来处理并口的硬件中断。驱动程序在并口中断服务程序中通过EPP并口读取A/D转换的结果,并且向RING3的应用程序发送消息通知应用程序读取数据。应用程序对数据做进一步的分析和处理,如图形显示、数据文件的存取等。

电子发烧友App

电子发烧友App

评论