本帖最后由 gk320830 于 2015-3-5 17:59 编辑

我用51单片机设计小项目,要共用IO口,如P0,有八位A-D输入,也有八位数据输出。接锁存器1(74hc573)到P0口

2014-04-15 22:01:40

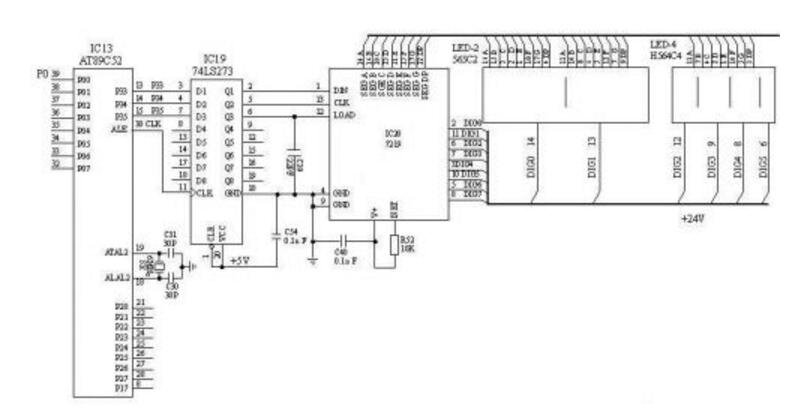

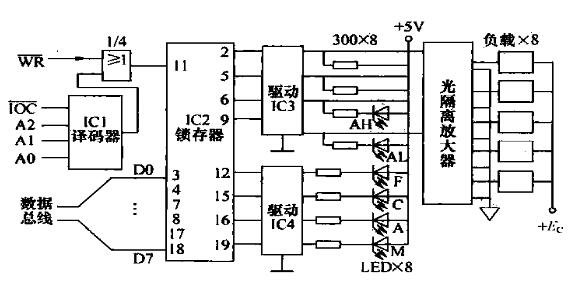

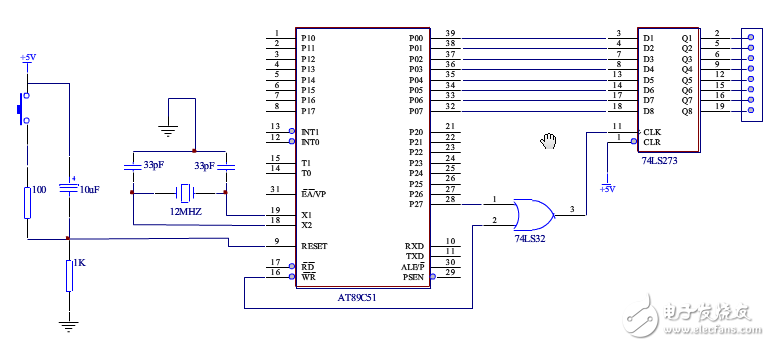

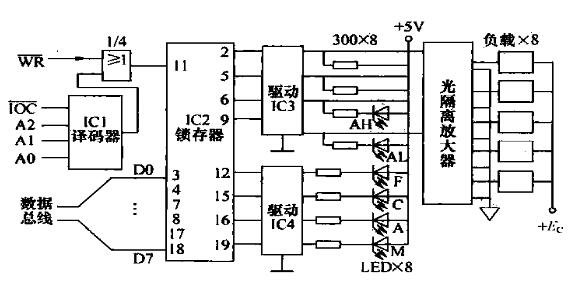

电路基于51单片机,外部已接RAM,ROM和CAN控制器,采用P2部分地址线译码线选各器件,由于I\o口有限 ,设想外接一片锁存器,模拟为单片机的外部RAM ,通过写锁存器产生8路控制信号,锁存器

2015-09-26 11:02:24

口,称地址/数据总线口。P0口用输出外部存储器的低8位地址。(高8位用P2)由于数据和地址是分时输出,故应在外部加锁存器将此地址数据锁存,地址锁存信号用ALE。P0用于读/写外部数据存储器的数据当不需要读写外部存储器时,P0口可用作普通的I/O输出端口,此时,需要上拉电阻P0口可驱动8个LST

2022-01-05 06:33:32

我用8255扩展51单片机的I/O口,A0、A1、CS分别接P2.0、P2.1、P2.7,虽然可以算出PA、PB、PC的地址,但需要对PA、PB、PC口中单独的I/O控制。能定义单独里面的I/O

2013-03-12 11:26:17

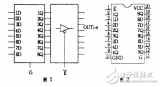

,可以把多个74HC164串联起来用。串联的方法如图2所示。 在上图的串联电路中,左边的锁存器D7与右边锁存器的串行数据输入端连接,当左边的锁存器D0~D7数据全部输出以后,再输入一个串行信号,左边锁

2018-07-19 04:24:53

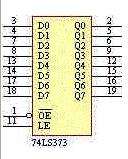

实现过程74HC138译码器(38译码器)——>74HC02或非门——>74HC573锁存器三八译码器三个输入控制八路互斥的低有效输出(三个P2口控制8个Y口,100控制Y4输出低电平)74HC573锁存器OE和LE分别是什么???如图所示:J13跳线帽的不同的引脚接法?...

2021-12-07 06:42:47

74HC573锁存器如何控制数码管静态显示?

2021-09-29 08:30:54

,丰富你的文章UML 图表FLowchart流程图导出与导入导出导入74HC573是锁存器,Y4C为高电平时锁存器Q

2022-01-17 07:54:43

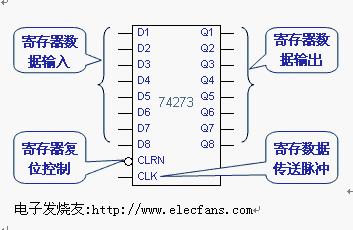

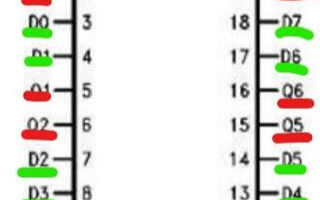

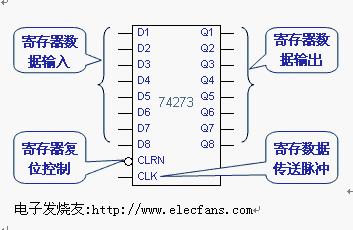

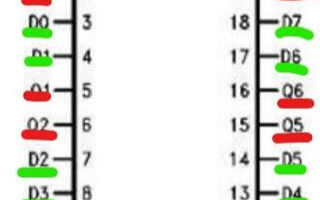

锁存器作用:可以把数据输入端与输出端进行隔离或连接。74HC573锁存器原理图见文末。图中:锁存器2-9脚为数据输入端,连接单片机数据输出引脚;12-19脚为数据输出端。GND接地,Vcc接正极

2021-11-23 06:58:06

74HC573锁存器:当N_LE引脚为高电平时,H_D0~H_D7的电平信号可以直接传到右端给到LED;如果N_LE引脚为低电平的时候,无论H_D0~H_D7的电平信号如何改变,HC573锁存器右端

2021-12-15 08:35:31

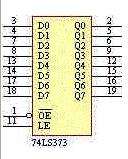

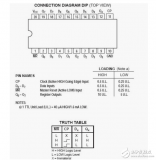

①简介74HC573是一种八进制3态非反转透明锁存器。它是高性能硅门COMS器件。②管脚定义和说明OELEGNDVCC1D-8D1Q-8Q使能端锁存控制端地电源数据输入端数据输出端③真值表(L表示

2021-11-22 06:58:35

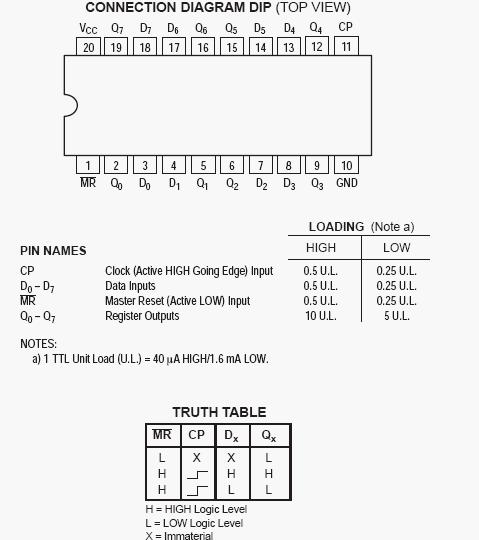

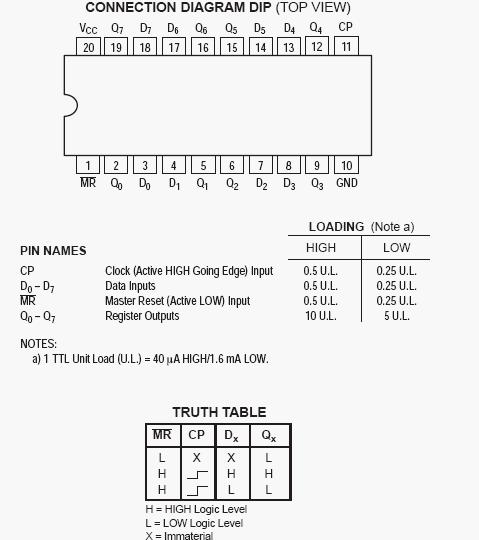

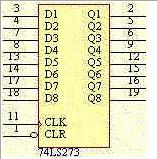

74LS273 - 8-Bit Register with Clear - National Semiconductor

2022-11-04 17:22:44

74LS273 - OCTAL D FLIP-FLOP WITH CLEAR - Motorola, Inc

2022-11-04 17:22:44

74LS273 - Octal D-type Positive-edge-triggered Flip-Flops(with Clear) - Hitachi Semiconductor

2022-11-04 17:22:44

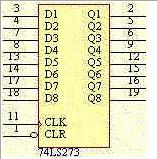

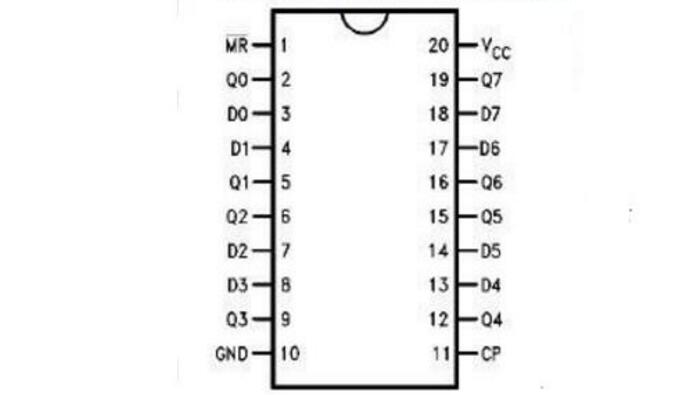

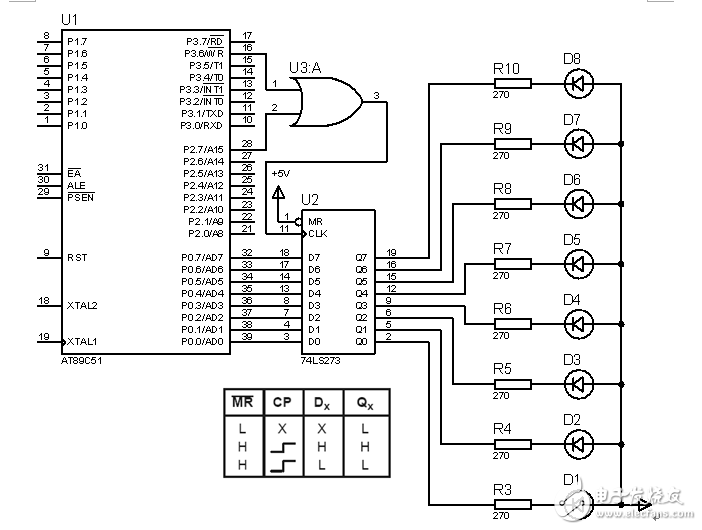

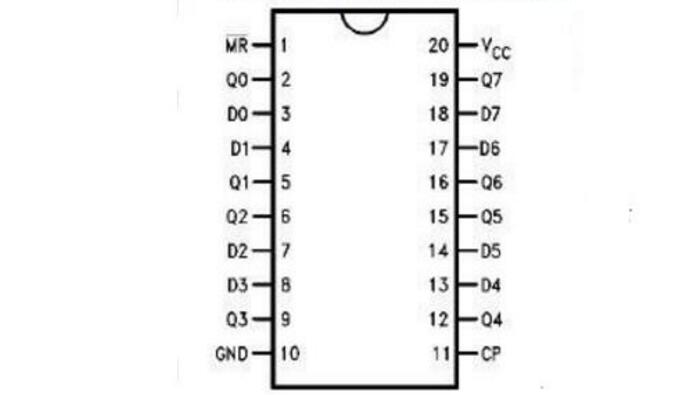

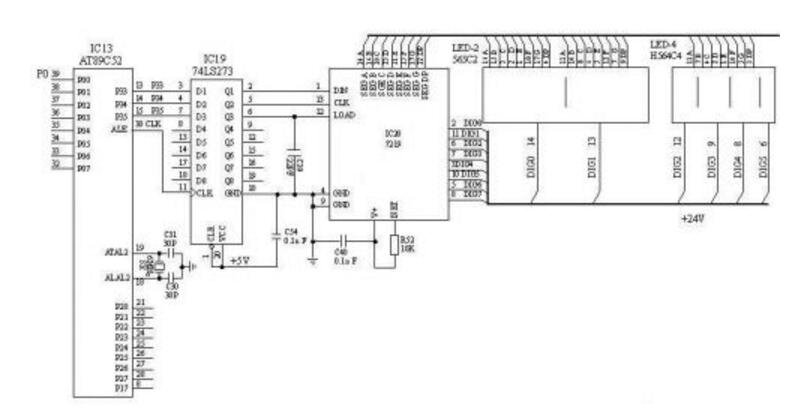

74LS273是8位数据/地址锁存器,它是一种带清除功能的8D触发器 , D0~D7为数据输入端,Q0~Q7为数据输出端,正脉冲触发,低电平清除,常用作数据锁存器,地址锁存器。(1)1脚是复位

2021-07-29 06:19:56

74LS273是什么?74LS273触发器是如何工作的?

2021-11-01 07:01:53

; 双四位可寻址锁存器 74ls257 四2选1数据选择器(三态输出

2009-08-18 17:26:31

74LS138译码器是什么?74LS138译码器的扩展方法是什么?

2022-01-19 07:14:36

74LS373_锁存器 英文资料,暂时还没发现有中文资料,如果有会及时发给大家

2013-07-22 13:03:43

,小于10μAlI/O端口输出带锁存功能,且具有较大的电流驱动能力,可直接驱动LEDl提供3个可编程地址引脚,在I2C总线上可挂接最多8个同类器件l与Philips公司的PCF8574/8574A完全

2014-05-12 13:40:47

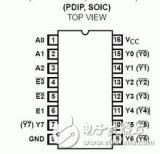

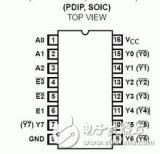

74HC138译码器的一种应用—扩展MCU的控制I/O口 1、74HC138译码器的引脚功能说明 芯片实物图 引脚功能说明 (1)地址线三根A0、A1和A2二进制码可以译出8种

2020-12-25 14:55:25

数码管的动态显示截取了部分程序,使用了74hc573锁存器,但是我觉得去掉锁存器程序照样可以执行,那么这里使用锁存器的意义是什么呢?还是说只是用一下没有什么特殊的含义? for( i=0; i

2013-03-11 16:59:52

; i<9; i++)

{

LE = 0;//输出使能,锁存器不输出数据

P0 = LedOut;

LE = 1;//输出使能,锁存器将8位数据一口吐出

P2 = dispbit;//使用查表法进行

2023-10-26 07:18:07

的处理时间,消耗了处理器的处理能力,还浪费了处理器的功耗。 锁存器的使用可以大大的缓解处理器在这方面的压力。当处理器把数据传输到锁存器并将其锁存后,锁存器的输出引脚便会一直保持数据状态直到下一次锁存

2011-03-26 20:41:22

P0口作为分时复用接口,既要作为数据总线口,又要作为地址总线口 输出的低8位地址需要用8位锁存器锁存 ALE的下降沿将P0口输出的低8位地址锁存• 对于锁存器:○ /OE为输出使能端 § /OE有效

2021-12-13 08:23:27

锁存器(latch)---对脉冲电平敏感,在时钟脉冲的电平作用下改变状态锁存器是电平触发的存储单元,数据存储的动作取决于输入时钟(或者使能)信号的电平值,仅当锁存器处于使能状态时,输出才会随着数据

2019-04-23 03:35:28

对地址进行锁存,如果P1口仅用于显示驱动,而没有与其它外设进行数据交换,可省略这个锁存器,直接或通过其他驱动电路驱动连接LED。地址线通过一片74LS138三—八译码器对8位LED进行分时选通,这样在任

2009-03-14 13:41:20

MCS-51单片机I/O端口的存取 MCS-51单片机通常有4个8位I/O端口, 向各端口的写数据均写入到对应端口的锁存器中,但对各端口的读操作却有两个方式:读锁存器和读引脚 字串61.读-修改-写

2017-08-18 10:10:27

实现,74LS273作为锁存输出接口,控制L8L1八个发光二极管的亮灭。(数据总线连接P0端口)二、仿真图三、代码C语言实现:#include***it com=P3^0;***it wr=P3^6; //74ls273-CLK***it rd=P3^7; //74ls244

2021-11-17 06:05:36

(1)I/O 口基本特性51 系列单片机有 4 个 8 位并行 I/O 接口,并行就是所有各位数据同时并排传输的方式,每一个接口都有数据输出锁存器、输入缓冲器和输出驱动器。锁存器作为特殊的寄存器属于

2021-07-21 07:14:01

未知未能而求知求能谓之学;已知已能而行之不已谓之习;温故而知新;故写而记之;锁存器74HC373:在学习和使用过程中,一般将OC直接接地,当LE为高时,此时将锁存器引脚打开;当LE为低时,此时将锁存器引脚关闭;其他引脚正常连接;//写该文章仅仅只为将学过的知识学之,习之。...

2021-12-06 07:24:22

用STM32F103RB的SPI做的扩展I/O,74HC165和595,80个输入点,然后串口输出给PC。请求帮助,QQ:292747058

2016-01-12 16:58:14

用STM32F427的FMC控制SRAM,由于端口不够用,想用FMC的数据地址总线复用功能,请问,是不是要加锁存器锁存地址,求电路

2016-09-18 11:35:51

学渣小学妹一枚,大二下学期课程设计老师给了个题目74ls273输出口控制8位led数码管滚动显示单个数字,电脑里的proteus不知道为什么没有MAKE,然后就总显示

2013-06-06 10:43:55

这是最近在做的课程设计,课题是电子密码锁,在密码经过验证后输出数据到锁存器中密码正确的情况密码错误的情况两种情况下都可以看到74ls175的D0口处于不同状态,但是输出却没有改变,导致绿灯一直亮着

2018-10-09 16:53:55

protues仿真16x16点阵字型残缺问题?用273锁存了也不行?

2014-01-12 18:03:03

P0 口,在满足总线地址读操作中,可以把输入InPORT的数据读入单片机的累加器,地址为0F8FFH 或8000H。输出口扩展电路如图11 所示。利用74LS273 数据锁存功能,在满足总线地址写操作

2018-07-28 20:56:47

P0 口,在满足总线地址读操作中,可以把输入InPORT的数据读入单片机的累加器,地址为0F8FFH 或8000H。输出口扩展电路如图11 所示。利用74LS273 数据锁存功能,在满足总线地址写操作

2018-07-24 17:02:41

)叫做输出接口(端口)。1)在输入数据时,由于外部设备处理的时间一般比 CPU 要长的多,不可能让 CPU 一直等外设传完数据再工作吧。...

2021-12-07 07:35:37

为什么配置I/O口:I/O端口寄存器复位后默认为输入(输出高阻态);为实现I/O端口功能需要先对端口进行I/O口初始化配置I/O口需要的几种寄存器:ANSELx(模拟选择寄存器):0 = 数字I/O

2021-11-24 06:19:54

光立方必须是74ALS573这种锁存器吗?我现在有这种74hc373d的锁存器能用吗?

2013-11-22 00:18:53

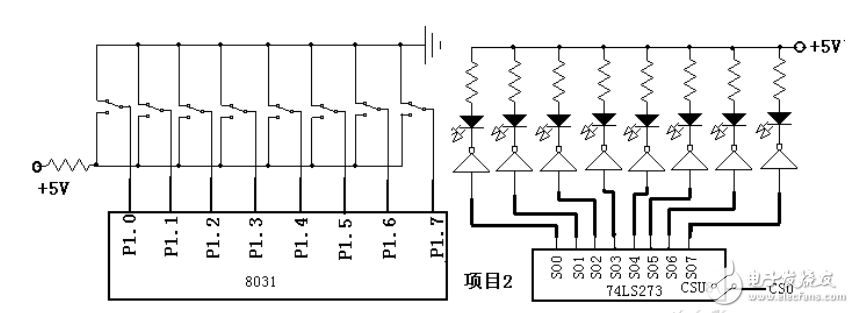

试用1片74LS244和1片74LS273为89S52扩展8位输入端口和8位输出端口,8位输入端口各接1个开关,8位输出端口各接1个发光二极管,要求按下1个开关,相对应的发光二极管发光。试画出硬件

2014-08-09 11:22:34

74HC573工作原理74HC573的八个锁存器都是透明的D型锁存器,当使能(G)为高时,Q输出将随数据(D)输入而变。当使能为低时,输出将锁存在已建立的数据电平上。输出控制不影响锁存器的内部工作

2021-12-07 08:02:02

决这个问题,可将页面地址提前从数据总线中输出并存放在锁存器中备用。将锁存器直接挂在数据总线上,并为其安排一个I/O地址,构成页面寄存器。在访问储器时,提前将页面地址作为数据写入页面寄存器中

2018-07-26 13:01:24

单片机P0口与其它端口不同,它的输出级无上拉电阻。当把它用作通用I/O口时,输出级是开漏电路,故用其输出去驱动NMOS输入时外接上拉电阻,这时每一位输出可以驱动4个LS型TTL负载。用作输入时,应先向端口锁存器写1。

2013-04-01 16:38:27

的每一条端口线也可以单独地用作位输入/输出线。各端口编址于特殊功能寄存器中,既有字节地址又有位地址。对端口锁存器的读/写操作,就可以实现端口的输入/输出操作。当不需要外部程序存储器和数据存储器扩展时,...

2021-07-30 06:53:09

地址读操作中,可以把输入InPORT的数据读入单片机的累加器,地址为0F8FFH或8000H。输出口扩展电路如图11所示。利用74LS273数据锁存功能,在满足总线地址写操作中,可以把单片机累加器里

2021-12-05 07:00:00

【单片机】简单I/O口扩展一、操作目的二、操作内容三、程序框图五、程序接线图六、程序清单七、代码详解一、操作目的(1)学习单片机系统中扩展简单I/O口的方法。(2)学习数据输入输出程序的编制方法。二

2022-01-17 06:46:45

一、设计目的� 1.了解并行口输入/输出方式的工作原理及其使用方法。�2.掌握80C51单片机扩展74LS244输入数据及扩展74LS273输出数据的方法二、设计要求1.利用单片机设计一个简单的以8

2013-12-10 17:33:57

,I / O端口,双向总线驱动器甚至是显示器时对连接电路的阻抗影响。司机。但是,单独使用一个“ 1位”数据锁存器并不是很实用,而是将市售的IC将4、8、10、16甚至32个单独的数据锁存器集成到一个IC

2021-02-03 08:00:00

三个四位比较器74LS85扩展成为8位的比较器,通过第三个74LS85与译码器74LS138相连,当两个DSWPK_8拨码相同时,74LS138的Y2输出口输出低电平通过反向器取反,使得绿光二极管

2020-12-12 15:34:11

一、设计目的1.了解并行口输入/输出方式的工作原理及其使用方法。�2.掌握80C51单片机扩展74LS244输入数据及扩展74LS273输出数据的方法二、设计要求1.利用单片机设计一个简单的以8位

2019-05-31 19:11:01

基于TPIC6B273的LED驱动控制设计TPIC6B23是美国TI公司生产的一种8通道D型触发器锁存、功率输出新型器件,该器件集8位数据锁存、驱动输出控制为一体. [/hide]

2009-12-01 10:15:12

本帖最后由 加油少年 于 2016-5-4 19:40 编辑

附件中有仿真图和程序仿真结果,有点缺陷就是做实物上可能还需要加一些三极管去驱动LED点阵,驱动是用74ls273锁存器,74hc138用于扫描。

2016-05-04 19:40:12

如何利用74LS373锁存器对LED进行控制呢?如何利用74LS373锁存器对数码管进行控制呢?

2022-01-18 07:20:46

/O的输出方向,x表示端口类别,比如TRISA就是操作A端口输出方向的,TRISx = 0,表示输出;TRISx = 1,表示输入。2.PORTx,该寄存器用于读I/O口的值,写该寄存器会输出相应的电平信号,具体是写入到数据锁存寄存器当中。3.LATx,数据所存寄存器,当TRISx为0时,写该寄存器可使相

2021-11-24 07:30:02

如果ic的io口不够了是否可以通过编码器译码器或者锁存器扩展呢,如果是输出或输入可以通过以上方法实现串行数据与并行相互转化吗?最好有具体案例列举~

2023-11-10 08:02:15

)信号的电平值,仅当锁存器处于使能状态时,输出才会随着数据输入发生变化。锁存器不同于触发器,它不在锁存数据时,输出端的信号随输入信号变化,就像信号通过一个缓冲器一样;一旦锁存信号起锁存作用,则数据被

2018-07-03 11:50:27

MCU通用I/O引脚扩展 低端MCU由于I/O口数量不足导致部分功能无法实现,用户需要使用数字集成芯片进行扩展,如74LS系列移位寄存器,但是这种集成芯片也会由于引脚数量限制而无法确保单片机端口

2024-01-08 09:35:10

对于74ls373当输入端没有接收到数据时,输出端都是输出高电平,有没有谁知道有哪种锁存器当输入端没有收到数据时,输出端是低电平的吗?急急急,求解答!!!

2013-05-03 17:13:32

LED灯,主要是想试下这个功能,我有好多I/O口要扩展,但上面电路的问题是,循环执行*(int *)0xc0002 = 0x000f;这个语句时可以正常点亮指示灯,但就是不能把状态在74CHT373中锁存

2011-03-23 14:11:14

用2片74LS273控制一个16*16点阵的列,每次把所显示的列数据发送到点阵上,用74hc154,4-16译码器选择选通的列显示。现在我想一次显示8个汉字,但是软件上有点问题想不通,希望有人给我说说思路。

2016-05-02 13:49:28

程序思路:通过74LS273驱动点阵的行,通过循环扫描不同的列来时显示汉字,显示结果如图所示,不知道出了什么问题。LZ试过把程序中显示延时改大,每列每列的显示,结果却能把图片中空缺的部分显示出来。不知道LZ出现了什么错误,就各位解答,谢谢!!!!!!!!!!!!!!

2016-04-11 15:58:13

,Y7C可以控制数码管的段选。74HC573锁存器可以通过74HC138译码器来控制;138译码器其高三位即P25,P26,P27决定八位输出。上图的元器件是逻辑或的运算,即0|1=1;因此当...

2022-01-12 06:28:34

怎样处理单片机与锁存器的关系? 为何要用串行口扩展 I/O?

2017-03-13 23:43:07

锁存器就是把当前的状态锁存起来,使CPU送出的数据在接口电路的输出端保持一段时间锁存后状态不再发生变化,直到解除锁定。还有些芯片具有锁存器,比如芯片74LS244就具有锁存的功能,它可以通过把一个

2022-03-01 07:00:42

The SN74LS273 is a high-speed 8-Bit Register. The registerconsists of eight D-Type Flip-Flops

2008-07-11 10:40:11 119

119 /O 扩展器 1 特性 • 1μA 低待机电流消耗(大值) • I 2C 至并行端口扩展器 • 开漏电路低电平有效中断输出&

2022-02-09 22:25:43

74ls273 proteus仿真(含dsn仿真文件)

2008-10-06 09:40:31 0

0 74ls273引脚图

引脚功能:

74LS273是8位数据/地址锁存器 74LS273是

2007-11-29 22:51:39 39431

39431

74ls273是什么及作用

74LS273是一种带清除功能的8D触发器, 1D~8D为数据输入端,1Q~8Q为数据输出端,正脉

2007-11-29 22:55:21 12818

12818

74ls273中文资料:是带有清除端的8D触发器,只有在清除端保持高电平时,才具有锁存功能,锁存控制端为11脚CLK,采用上升沿锁存。 CPU 的ALE信号必须经过反相器反相之后才能

2007-11-29 22:56:36 8602

8602 地址锁存器--74LS373

74LS373是带有三态门的八D锁存器,当使能信号线OE为低电平时,三态门处于导通状态,允许1Q-8Q输出到OUT1-OUT8,当OE端为高电平时,输出三态门断开,输出线

2009-03-14 15:36:48 13752

13752

地址锁存器--74LS273

74LS273是带清除端的八D触发器,只有清除端为高电平时才具有锁存功能,锁存控制端为11脚CLK,在上升沿锁存。单片机的ALE端输出的锁存控制信号必须经反

2009-03-14 15:37:57 4667

4667

在简单接口中一般使用锁存器构成输出接口。常用的有8D锁存器74HC273、74HC373、74HC377等。74HC273 是带清零端的8D锁存器。

2017-11-04 09:51:12 9210

9210

74LS273是8位数据/地址锁存器,他是一种带清除功能的8D触发器74LS273管脚图功能表等资料。1D~8D为数据输入端,74ls2731Q~8Q为数据输出端,正脉冲触发,低电平清除,常用作8位地址锁存器。

2017-11-07 17:03:04 17280

17280

74LS138 为3 线-8线译码器,其引脚图如下。 74LS138引脚功能 A0~A2:地址输入端 STA(E1):选通端 /STB(/E2)、/STC(/E3):选通端(低电平有效) /Y0

2017-11-29 19:21:48 6276

6276

74LS373是一款常用的地址锁存器芯片,由八个并行的、带三态缓冲输出的D触发器构成。在单片机系统中为了扩展外部存储器,通常需要一块74LS373芯片。

2017-12-05 17:07:44 16012

16012

本文开始介绍了74LS273引脚图及功能和工作原理,其次介绍了74ls273功能表和真值表,最后介绍了74ls273五款应用电路。

2018-04-26 16:56:25 168363

168363

本文主要介绍了七款74ls273串行显示电路、共阳LED数码显示电路和端口扩展电路等。74LS273是八D触发器。8个单边输出的触发器,缓冲时钟和直接清除输入,数据独立输入到各触发器。

2018-04-28 08:35:01 20354

20354

CPU只需执行一条输出指令,即可把逻辑数字信号写入到输出锁存器ICZ(74LS273)中,其锁存器的锁存控制信号由地址线通过IC1译码器输出与WR信号相或后得到。

2020-01-14 11:31:27 4763

4763

74LS273是8位数据/地址锁存器,它是一种带清除功能的8D触发器,D0~D7为数据输入端,Q0~Q7为数据输出端,正脉冲触发,低电平清除,常用作数据锁存器,地址锁存器。

2020-08-10 17:39:26 26142

26142

实现,74LS273作为锁存输出接口,控制L8L1八个发光二极管的亮灭。(数据总线连接P0端口)二、仿真图三、代码C语言实现:#include<reg52.h>sbit com=P3^0;sbit wr=P3^6; //74ls273-CLKsbit rd=P3^7; //74ls244

2021-11-10 19:05:59 10

10

电子发烧友App

电子发烧友App

评论