plc时序图怎么看

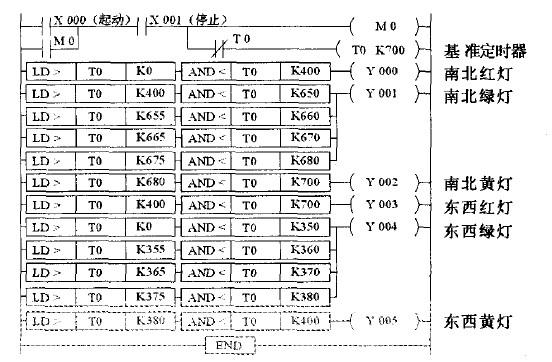

1. 用时序图分析图4-42所示梯形图的工作原理。

2. 若X0信号如图所示,请再分析该梯形图的工作原理。

例题分析

(1) X0信号使Y0及T0线圈接通。

(2) T0线圈接通1S后,T0的常开触点闭合,常闭触点断开。T0的常开触点接通Y1及T1线圈,此过程均在一个扫描周期内完成,该扫描周期直至ED结束(注意:PLC是循环扫描工作方式)。

(3) 在T0触点动作的下一个周期,T0的常闭触点使Y0失电,Y0常开触点断开使T0线圈失电,使 T0常开触点、常闭触点同时复位。

(4) T1线圈接通1S后,T1的常开、常闭触点均动作。

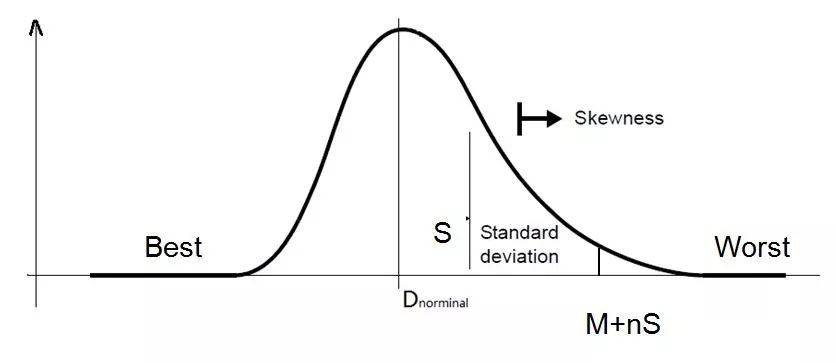

(5) 在下一个扫描周期T1的常开触点使Y0接通,Y0的常开触点又接通T0线圈。如此循环至X1信号到来使全系统复位。根据上述分析画出如图4-43所示的时序图,因梯形图中Y0、Y2、Y4、Y6、均为并联关系,时序图中只画了Y0的图形,Y1、Y3、T5、T7亦如此。

此题,是一个典型的霓虹灯控制程序,通过分析此题应更进一步理解PLC的循环扫描工作方式。

当X0为“ ”时在第③过程中只能将Y0关断一个扫描周期,实际中裸眼观察结果是Y0、Y2、Y4、Y6常亮。

PLC梯形图的分析方法和步骤

一、 总体分析

1 系统分析

依据控制系统所需完成的控制任务,对被控对象的工艺过程、工作特点以及控制系统的控制过程、控制规律、功能和特征进行详细分析,明确输入、输出物理量是开关量还是模拟量,明确划分控制的各个阶段及其特点,阶段之间的转换条件,画出完整的工作流程图和各执行元件的动作节拍表。

2 看主电路

进一步了解工艺流程及其对应的执行装置和元器件。

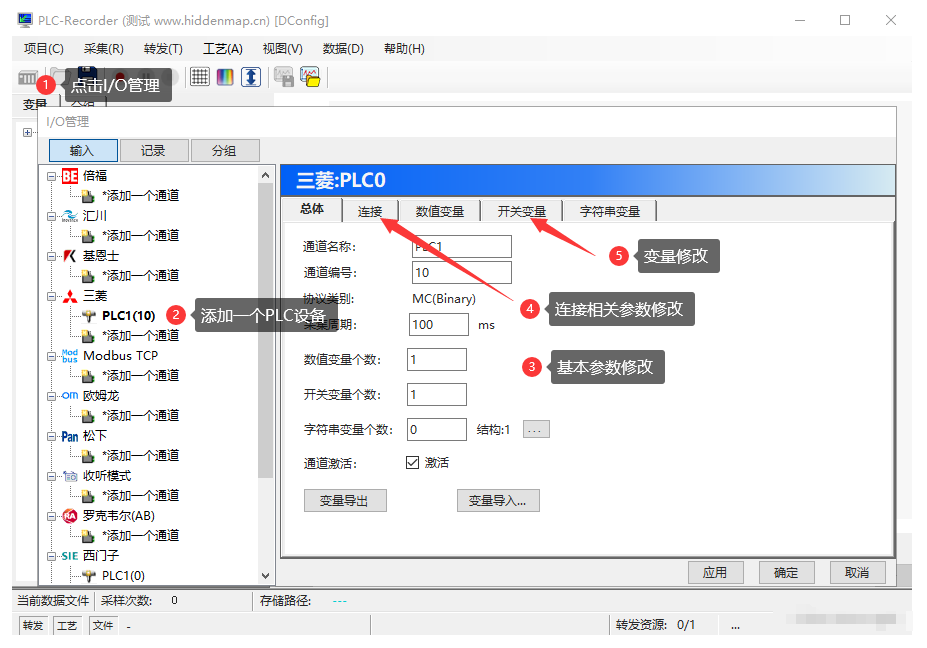

3 看PLC控制系统的I/O配置和PLC的I/O接线

了解输入信号和对应输入继电器的配置、输出继电器的配置及其所接的对应负载。

在没有给出输入/输出设备定义和PLC的I/O配置的情况下,应根据PLC的I/O接线图或梯形图和指令语句表,做出输入/输出设备定义和PLC的I/O配置。

4 通过PLC的I/O接线图了解梯形图

PLC的I/O接线是连接主电路和PLC梯形图的纽带。

1) 根据用电器(如电动机、电磁阀、电加热器等)主电路控制电器(接触器、继电器)主触点的文字符号,在PLC的I/O接线图中找出相应编程元件的线圈,便可得知控制该控制电器的输出继电器,再在梯形图或语句表中找到该输出继电器的程序段,并做出标记和说明。〖JP〗

2) 根据PLC的 I/O接线图的输入设备及其相应的输入继电器,在梯形图(或语句表)中找出输入继电器的动合触点、动断触点,并做出相应标记和说明。

二、 梯形图的结构分析

1 PLC控制系统梯形图的特点

(1) PLC控制系统的输入信号和输出负载

继电器电路图中的交流接触器和电磁阀等执行机构用PLC的输出继电器来控制,它们的线圈接在PLC的输出端。按钮、控制开关、限位开关、接近开关等用来给PLC提供控制命令和反馈信号,它们的触点接在PLC的输入端。

(2) 继电器电路图中的中间继电器和时间继电器的处理

继电器电路图中的中间继电器和时间继电器的功能用PLC内部的辅助继电器和定时器来完成,它们与PLC的输入继电器和输出继电器无关。

(3) 设置中间单元

在梯形图中,若多个线圈都受某一触点串/并联电路的控制,为了简化电路,在梯形图中可设置用该电路控制的辅助继电器,辅助继电器类似于继电器电路中的中间继电器。

(4) 时间继电器瞬动触点的处理

时间继电器除了延时动作的触点外,还有在线圈得电或失电时立即动作的瞬动触点。对于有瞬动触点的时间继电器,可以在梯形图中对应的定时器的线圈两端并联辅助继电器,后者的触点相当于时间继电器的瞬动触点。

(5) 外部联锁电路的设立

为了防止控制正/反转的两个接触器同时动作,造成三相电源短路,除了在梯形图中设置与它们对应的输出继电器的线圈串联的动断触点组成的软互锁电路外,还应在PLC外部设置硬互锁电路。

2 梯形图的结构分析

采用一般编程方法还是采用顺序功能图编程方法;采用顺序功能图的单序列结构还是选择序列结构、并行序列结构,使用启/保/停电路、步进顺控指令进行编程还是用置位/复位指令进行编程。这部分内容见第四章和第五章。

梯形图的分解由操作主令电路(如按钮)开始,查线追踪到主电路控制电器(如接触器)动作,中间要经过许多编程元件及电路,查找起来比较困难。

无论多么复杂的梯形图,都是由一些基本单元构成的。按主电路的构成情况,利用逆读溯源法,把梯形图和指令语句表分解成与主电路的用电器(如电动机)相对应的几个基本单元,然后一个环节、一个环节地分析,最后再利用顺读跟踪法把各环节串起来。

(1) 按钮、行程开关、转换开关的配置情况及作用

在PLC的I/O接线图中有许多行程开关和转换开关,以及压力继电器、温度继电器等,这些电器元件没有吸引线圈,它们的触点的动作是依靠外力或其他因素实现的,因此必须先把引起这些触点动作的外力或因素找到。其中行程开关由机械联动机构来触压或松开,(文章来源:http://www.dqjsw.com.cn)而转换开关一般由手工操作,从而使这些行程开关、转换开关的触点在设备运行过程中便处于不同的工作状态,即触点的闭合、断开情况不同,以满足不同的控制要求,这是看图过程中的一个关键。

这些行程开关、转换开关的触点的不同工作状态单凭看电路图难以搞清楚,必须结合设备说明书、电器元件明细表,明确该行程开关、转换开关的用途,操纵行程开关的机械联动机构,触点在不同的闭合或断开状态下电路的工作状态等。

(2) 采用逆读溯源法将多负载(如多电动机电路)分解为单负载(如单电动机)电路

根据主电路中控制负载的控制电器的主触点文字符号,在PLC的I/O接线图中找出控制该负载的接触器线圈的输出继电器,再在梯形图和指令语句表中找出控制该输出继电器的线圈及其相关电路,这就是控制该负载的局部电路。

在梯形图和指令语句表中,很容易找到该输出继电器的线圈电路及其得电、失电条件,但引起该线圈的得电、失电及其相关电路就不容易找到,可采用逆读溯源法去寻找:

1) 在输出继电器线圈电路中串、并联的其他编程元件触点的闭合、断开就是该输出继电器得电、失电的条件。

2) 由这些触点再找出它们的线圈电路及其相关电路,在这些线圈电路中还会有其他接触器、继电器的触点……

3) 如此找下去,直到找到输入继电器(主令电器)为止。

值得注意的是:当某编程元件得电吸合或失电释放后,应该把该编程元件的所有触点所带动的前、后级编程元件的作用状态全部找出,不得遗漏。

找出某编程元件在其他电路中的动合触点、动断触点,这些触点为其他编程元件的得电、失电提供条件或者为互锁、联锁提供条件,引起其他电器元件动作,驱动执行电器。

(3) 将单负载电路进一步分解

控制单负载的局部电路可能仍然很复杂,还需要进一步分解,直至分解为基本单元电路。

(4) 分解电路的注意事项

1) 若电动机主轴接有速度继电器,则该电动机按速度控制原则组成停车制动电路。

2) 若电动机主电路中接有整流器,表明该电动机采用能耗制动停车电路。

(5) 集零为整,综合分析

把基本单元电路串起来,采用顺读跟踪法分析整个电路。

三、 识读梯形图的具体方法

识读PLC梯形图和语句表的过程同PLC扫描用户过程一样,从左到右、自上而下,按程序段的顺序逐段识图。

值得指出的是:在程序的执行过程中,在同一周期内,前面的逻辑运算结果影响后面的触点,即执行的程序用到前面的最新中间运算结果。但在同一周其内,后面的逻辑运算结果不影响前面的逻辑关系。该扫描周期内除输入继电器以外的所有内部继电器的最终状态(线圈导通与否、触点通断与否)将影响下一个扫描周期各触点的通与断。

由于许多读者对继电器接触器控制电路比较熟悉,因此建议沿用识读继电器接触器控制电路查线读图法,按下列步骤来看梯形图:

1) 根据I/O设备及PLC的I/O分配表和梯形图,找出输入、输出继电器,并给出与继电器接触器控制电路相对应的文字代号。

2) 将相应输入设备、输出设备的文字代号标注在梯形图编程元件线圈及其触点旁。

3) 将梯形图分解成若干基本单元,每一个基本单元可以是梯形图的一个程序段(包含一个输出元件)或几个程序段(包含几个输出元件),而每个基本单元相当于继电器接触器控制电路的一个分支电路。

4) 可对每一梯级画出其对应的继电器接触器控制电路。

5) 某编程元件得电,其所有动合触点均闭合、动断触点均断开。某编程元件失电,其所有已闭合的动合触点均断开(复位),所有已断开的动断触点均闭合(复位)。因此编程元件得电、失电后,要找出其所有的动合触点、动断触点,分析其对相应编程元件的影响。

6) 一般来说,可从第一个程序段的第一自然行开始识读梯形图。第一自然行为程序启动行。按启动按钮,接通某输入继电器,该输入继电器的所有动合触点均闭合,动断触点均断开。

再找出受该输入继电器动合触点闭合、动断触点断开影响的编程元件,并分析使这些编程元件产生什么动作,进而确定这些编程元件的功能。值得注意的是:这些编程元件有的可能立即得电动作,有的并不立即动作而只是为其得电动作做准备。

由PLC的工作原理可知,当输入端接动合触点,在PLC工作时,若输入端的动合触点闭合,则对应于该输入端子的输入继电器线圈得电,它的动合触点闭合、动断触点断开;当输入端接动断触点且在PLC工作时,若输入端的动断触点未动作,(文章来源:http://www.dqjsw.com.cn)则对应于该输入端的输入继电器线圈得电,它的动合触点闭合、动断触点断开。如果该动断触点与输出继电器线圈串联,则输出继电器线圈不能得电。因而,用PLC控制电动机的启停,如果停止按钮用动断触点,则与控制电动机的接触器相接的PLC输出继电器线圈应与停止按钮相接的输入端子相对应的动合触点串联。在继电接触控制中,停止按钮和热继电器均用动断触点,为了与继电接触控制的控制电路相一致,在PLC梯形图中,同样也用动断触点,这样一来,与输入端相接的停止按钮和热继电器触点就必须用动合触点。在识读程序时必须注意这一点。

四、 识读PLC梯形图的示例

在分析PLC控制系统的功能时,可以将它想象成一个继电器控制系统中的控制箱,其外部接线图描述了这个控制箱的外部接线,梯形图或语句表是这个控制箱的内部“线路图”,梯形图中的输入继电器和输出继电器是这个控制箱与外部世界联系的“接口继电器”,这样就可以用分析继电器电路图的方法来分析PLC控制系统。在分析时可以将梯形图中输入继电器的触点想象成对应的外部输入器件的触点或电路,将输出继电器的线圈想象成对应的外部负载的线圈。外部负载的线圈除了受梯形图的控制外,还可能受外部触点的控制。

电子发烧友App

电子发烧友App

评论