Silicon Laboratories (芯科实验室有限公司, NASDAQ: SLAB)今日宣布推出业界首款通用时钟缓冲器(clock buffer),可以用单颗IC替代多颗LVPECL、LVDS、CML、HCSL和LVCMOS缓冲器,而无需多个不同格式缓冲器

2012-11-06 09:08:20 2237

2237 概述:MAX3625B是MAXIM公司生产的一款提供三路输出的低抖动,高精度时钟发生器。该MAX3625B是为网络应用而优化的低抖动,高精度时钟发生器。该器件集成一个晶体振荡器和锁相环(PLL)时钟

2021-05-18 07:39:05

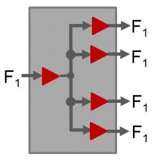

的不确定性,导致抖动增加。在实际系统中,一个时钟源要驱动多个器件,因此可使用时钟缓冲器(通常称为扇出缓冲器)来复制信号源,提供更高的激励电平。图 1. 使用扇出缓冲器创建大量单输入频率副本LMK00304

2018-09-13 10:11:44

》,掌握更多时钟技巧,如如何测量抖动以及如何使用分数 PLL 创建调制波形等;观看《如何测量扇出缓冲器中的附加抖动》视频;进一步了解我们面向无线及有线通信、工业以及汽车应用的时钟产品系列。

2018-09-13 14:18:06

ADCLK846 / PCBZ,ADCLK846评估板是一款高性能时钟扇出缓冲器。评估板采用高品质Rogers介电材料制造。传输线路径尽可能差分地保持接近100欧姆

2019-02-21 09:54:43

2.5 V/3.3 V, 4个LVPECL输出,SiGe时钟扇出缓冲器

2023-03-28 15:01:21

AKD8181D,AK8181时钟扇出缓冲器评估板。因此,很容易评估DC / AC特性并确认产品功能

2020-08-25 15:26:54

CDCLVC1102 低抖动 1:2 LVCMOS 扇出时钟缓冲器

2023-03-28 18:26:07

CDCLVP1204是一个低附加抖动的LVPECL扇出缓冲器,它可以生成两个可选的LVPECL、LVDS或LVCMOS输入的四个副本。CDCLVP1204可以接受高达2ghz的基准时钟频率,同时提供低输出

2020-07-09 10:05:06

本文为高速数据转换器提供了一个低抖动时钟源的参考设计,目标是在时钟频率高达2GHz时,边沿间抖动《 100fs。对于1GHz模拟输出频率,所产生的抖动信噪比SNR为:-20 × log(2 × π × f × tj) = -64dB。

2021-04-15 06:28:19

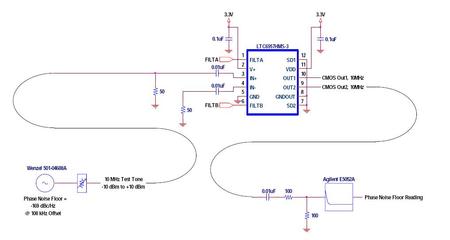

使用,DC1795A安装了100MHz基准电压源和1GHz VCSO,电压控制SAW振荡器,具有正弦波输出。所有差分输入和输出都有0.5个间隔的SMA连接器。 DC1795A具有四个交流耦合LVPECL输出,具有50条传输线,适合驱动50个阻抗仪器。 LVDS / CMOS输出是直流耦合的

2019-02-25 09:55:24

用它。时钟连接到Artix-7上HR bank中的CC引脚,VCCO = 1.8V。由于HR bank仅支持LVDS_25,需要VCCO为2.5V,因此我增加了一个外部终端电阻。问题:可以直接将时钟缓冲器的输出连接到HR库吗?我需要在FPGA的输入端添加交流耦合电容和直流偏置电阻吗?谢谢

2020-07-24 15:16:28

:

由于不希望增加时钟管理芯片增加成本,可否直接使用低抖动的有源晶振 2v5/3v3的输出如图连接?

或者 ,可否直接使用LVPECL输出的有源晶振交流耦合至AD的时钟引脚?

2023-12-22 06:29:38

高端时钟缓冲器用户不再需要面对抖动与电流的折衷

2021-04-06 06:24:31

中,一个时钟源要驱动多个器件,因此可使用时钟缓冲器(通常称为扇出缓冲器)来复制信号源,提供更高的激励电平。图 1. 使用扇出缓冲器创建大量单输入频率副本LMK00304 扇出缓冲器就是一个很好的例子

2022-11-21 07:25:28

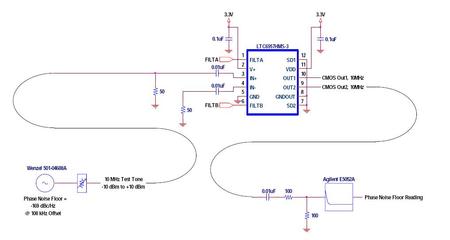

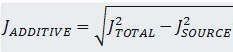

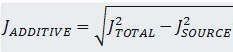

分配网络上分配低抖动时钟源。随着系统要求的不断提升,问题也随之而来:时钟线路上添加的简单缓冲器会不会让时钟抖动变得更差?如果会,在添加简单缓冲器之前应该考虑什么问题?图 1:系统级说明 附加抖动定义

2022-11-22 07:13:40

测量扇出缓冲器中的附加抖动怎么计算?

2021-05-06 07:02:23

达到所需的系统抖动性能,一定要保持尽可能低的时钟抖动,并在整个分配网络上分配低抖动时钟源。随着系统要求的不断提升,问题也随之而来:时钟线路上添加的简单缓冲器会不会让时钟抖动变得更差?如果会,在添加简单

2018-09-13 14:38:43

时钟信号衰减会增加抖动,因此对驱动器输出的端接很重要。为了避免抖动和时钟质量降低的不利影响,需要使用恰当的信号端接方法。4种端接方法分享给你们。· Z0是传输线的阻抗;· ZOUT 是驱动器

2019-09-27 07:30:00

电路串联在一起,可减少放大器输出端的过冲。有没有可能使用可变电压控制的电流源来抑制放大器的过冲倾向。这是创建这种放大器以驱动开关电容负载的一种创新方法。好消息是,基于比较器的缓冲器通常是一种功耗比运

2021-04-02 07:32:16

怎么设计一种用于多路输出时钟缓冲器中的锁相环?锁相环主要结构包括哪些?

2021-04-20 06:27:26

与传统的时钟缓冲器相比,高速运算放大器有哪些优势?怎样去设计一个灵活的时钟缓冲器?

2021-04-14 06:35:37

增加时钟管理芯片增加成本,可否直接使用低抖动的有源晶振 2v5/3v3的输出如图连接? 或者 ,可否直接使用LVPECL输出的有源晶振交流耦合至AD的时钟引脚?

2018-11-02 09:25:09

我们的设计利用了PCIe内核,该内核遇到了一些时序错误。为了确保设计得到适当的约束,我一直在审查所有输入/输出延迟,输入抖动和系统抖动限制。在我们的设计中,PCIe时钟源是125MHz振荡器。我无法

2020-08-04 10:31:33

ADCLK948 / PCBZ,ADCLK948评估板是一款性能非常高的时钟扇出缓冲器。评估板采用高品质Rogers介电材料制造。传输线路径尽可能保持接近50欧姆

2019-02-21 09:54:06

(假定扇出数为140),为了减少扇出,用系统时钟采样,将M1信号驱动7个D触发器, 然后将7个D触发器的输出端分给7个模块,这样每个复制点(DUP0~DUP6)平均扇出变为20, M1的信号扇出变为7

2012-01-12 10:40:20

了就是下雨了。今天咱们来看看零延时缓冲器吧。也是由缓冲一词想到的。它是指一种可以将一个时钟信号扇出成多个时钟信号,并使这些输出之间有零延时和很低的偏斜的器件。此器件很适合用于要求输入到输出和输出到输入

2014-05-20 17:32:38

ADCLK946 / PCBZ,ADCLK946评估板是一款性能非常高的时钟扇出缓冲器。评估板采用高品质Rogers介电材料制造。传输线路径尽可能保持接近50欧姆

2019-02-21 09:55:44

时 ADCLK954 时 钟缓冲器的输出波形输出端接时钟信号衰减会增加抖动,因此对驱动器输出的端接很重要,这可以避免信号反射,并可通过相对较大的带宽实现最大能量传输。确实,反射可以造成下冲和过冲,严重降低信号

2018-10-17 15:12:30

US5S110A是一款高性能、低偏斜时钟扇出缓冲器,此缓冲器可将一路单端输入分配到两组10路低抖动LVCMOS时钟输出。上电后,输出默认状态为低。当控制引脚(1G或者2G)保持低电平并且在CLK输入

2021-11-15 11:23:54

US5S106一款高性能、低偏斜时钟扇出缓冲器,此缓冲器可将一路单端输入分配到6路低抖动LVCMOS时钟输出。上电后,输出默认状态为低。当控制引脚(1G)保持低电平并且在CLK输入上检测到负时钟边沿

2021-11-15 13:28:23

US5S108是一款高性能、低偏斜时钟扇出缓冲器,此缓冲器可将一路单端输入分配到8路低抖动LVCMOS时钟输出。上电后,输出默认状态为低。当控制引脚(1G)保持低电平并且在CLK输入上检测到负时钟

2021-11-15 14:16:54

US5S110B是一款高性能、低偏斜时钟扇出缓冲器,此缓冲器可将一路单端输入分配到10路低抖动LVCMOS时钟输出。上电后,输出默认状态为低。当控制引脚(1G)保持低电平并且在CLK输入上检测到负

2021-11-15 15:00:27

S5S112是一款高性能、低偏斜时钟扇出缓冲器,此缓冲器可将一路单端输入分配到12路低抖动LVCMOS时钟输出。上电后,输出默认状态为低。当控制引脚(1G)保持低电平并且在CLK输入上检测到负时钟

2021-11-15 15:06:14

US5S110是一款高性能、低偏斜时钟扇出缓冲器,此缓冲器可将一路单端输入分配到两组10路低抖动LVCMOS时钟输出。

2022-06-21 15:45:45

低偏移、1 至 5、差动至 3.3V LVPECL 扇出缓冲器 Function Differential, Fanout Additive RMS jitter (Typ) (fs

2022-11-30 16:58:58

低抖动 1:2 LVCMOS 扇出时钟缓冲器 Function Single-ended Additive RMS jitter (Typ) (fs) 70 Output

2022-11-30 16:59:14

低抖动 1:3 LVCMOS 扇出时钟缓冲器 Function Single-ended Additive RMS jitter (Typ) (fs) 70 Output

2022-11-30 16:59:16

低抖动 1:6 LVCMOS 扇出时钟缓冲器 Function Single-ended Additive RMS jitter (Typ) (fs) 70 Output

2022-11-30 16:59:16

低抖动 1:8 LVCMOS 扇出时钟缓冲器 Function Single-ended Additive RMS jitter (Typ) (fs) 70 Output

2022-11-30 16:59:17

低抖动 1:10 LVCMOS 扇出时钟缓冲器 Function Single-ended Additive RMS jitter (Typ) (fs) 70 Output

2022-11-30 16:59:18

低抖动 1:4 LVCMOS 扇出时钟缓冲器 Function Single-ended Additive RMS jitter (Typ) (fs) 70 Output

2022-11-30 16:59:18

低抖动 1:12 LVCMOS 扇出时钟缓冲器 Function Single-ended Additive RMS jitter (Typ) (fs) 70 Output

2022-11-30 16:59:19

ADCLK944是一款超快型时钟扇出缓冲器,采用ADI公司专有的XFCB3硅锗(SiGe)双极性工艺制造。这款器件设计用于要求低抖动性能的高速应用。 该器件具有一路配中心抽头、差分、100

2023-02-13 15:10:44

摘要:DS34T10x和DS34S10x系列TDM-over-Packet (TDMoP)芯片采用抖动缓冲器来补偿包网络中存在的报文时延差异。本应用笔记将解释PDV的含义以及它如何影响通信质量,讨论抖动缓冲器的作用

2009-04-20 10:51:32 517

517

TI推出正弦至正弦波时钟缓冲器

日前,德州仪器 (TI) 宣布推出业界最小型 4 通道、低功耗、低抖动正弦至正弦波时钟缓冲器。作为正弦波时钟缓冲器系列产品中的首款

2009-11-30 10:53:51 815

815 TI新推高集成正弦波时钟缓冲器可显著降低成本,节省板级空间

日前,德州仪器 (TI) 宣布推出业界最小型 4 通道、低功耗、低抖动正弦至正弦波时钟缓冲器。作为正弦

2009-12-01 08:43:11 1112

1112 日前,德州仪器 (TI) 宣布推出 2 款最新通用时钟缓冲器系列,进一步壮大其高性能时钟缓冲器产品阵营。CDCLVC1310 LVCMOS 时钟缓冲器可在晶振模式下实现 –169 dBc/Hz 的业界领先相位噪声

2012-04-05 08:47:28 1062

1062 IDT最新的差分扇出缓冲器系列运行于1.8V,拥有堪比3.3V版本的AC性能,适用于高性能通信、计算和网络应用。

2014-01-22 14:34:18 1926

1926 如果您在通信行业工作,那么您可能很熟悉抖动对系统性能的影响。抖动不仅会降低数据转换器的性能,而且还可在高速数字系统中产生误码。凭直觉判断,给时钟增加噪声会增大系统其它部分的噪声。因此我总是试图通过选择可带来最小附加抖动的组件来最大限度地降低总体抖动。

2017-04-08 04:19:11 2643

2643

LMK0033x是德州仪器(TI)推出的业界最低抖动的PCIe时钟扇形缓冲器。现在就让德仪的工程师向你介绍它的具体情况吧!

2018-06-13 11:52:00 4883

4883 EngineerIt-测量时钟扇出缓冲器的残余噪声

2018-08-13 00:23:00 3233

3233 您正在寻找低附加相位噪声(抖动)缓冲器,以将10MHz正弦波源作为参考时钟分配到您的系统中。在查看来自不同供应商的几个数据表之后,您意识到在这个相对较低的频率下给出的性能信息不多。市场上大多数高性能

2019-04-16 08:18:00 2816

2816

时钟信号衰减会增加抖动,因此对驱动器输出的端接很重要。为了避免抖动和时钟质量降低的不利影响,需要使用恰当的信号端接方法。4种端接方法分享给你们。 Z0是传输线的阻抗; ZOUT是驱动器的输出

2019-11-11 15:55:08 7113

7113

ADCLK846:1.8 V、6 LVDS/12 CMOS输出低功耗时钟扇出缓冲器

2021-03-20 11:31:10 9

9 AD9523-1:低抖动时钟发生器,14路LVPECL/LVDS/HSTL输出或29路LVCMOS输出 数据手册

2021-03-21 14:28:08 1

1 AD9525: 8路LVPECL输出低抖动时钟发生器

2021-03-21 15:00:20 0

0 AD9508:1.65 GHz时钟扇出缓冲器,集成输出分频器和延迟调整

2021-03-21 15:45:30 2

2 自适应抖动缓冲器-下载产生码

2021-04-12 16:47:30 3

3 ADCLK950:两个可选输入、10个LVPECL输出、SiGe时钟扇出缓冲器数据表

2021-04-19 16:40:05 7

7 ADCLK946:六路LVPECL输出,SiGe时钟扇出缓冲器数据表

2021-04-19 21:21:44 7

7 UG-942:HMC6832 3.5 GHz、低噪声、2:8差分扇出缓冲器评估板

2021-04-24 10:05:17 9

9 ADCLK954:两个可选输入、12个LVPECL输出、SiGe时钟扇出缓冲器数据表

2021-04-25 16:26:36 7

7 ADCLK948:两个可选输入、8个LVPECL输出、SiGe时钟扇出缓冲器数据表

2021-04-25 16:29:54 7

7 UG-892:评估HMC7043高性能、3.2 GHz、14输出扇出缓冲器

2021-04-27 21:57:28 11

11 HMC7043:高性能、3.2 GHz、14输出扇出缓冲器数据表

2021-04-28 18:55:11 13

13 ADH987S:3.3V低噪声1:9扇出缓冲器DC-4.5 GHz数据表

2021-05-22 19:21:46 1

1 HMC6832:低噪声、2:8差分扇出缓冲器数据表

2021-05-25 09:34:37 4

4 LTC6955:超低抖动、7.5 GHz、11输出扇出缓冲器系列数据表

2021-05-27 20:57:08 9

9 差分输出提供多达八路差分、低电压正射极耦合逻辑(LVPECL)输出。 图1. 连接至ADCLK948扇出缓冲器的ADF4351 PLL(原理示意图:未显示所有连接和去耦) 现代数字系统经常要求使用

2021-06-05 21:37:12 1

1 自适应抖动缓冲器-下载产生码

2021-06-16 11:08:38 4

4 的不确定性,导致抖动增加。

在实际系统中,一个时钟源要驱动多个器件,因此可使用时钟缓冲器(通常称为扇出缓冲器)来复制信号源,提供更高的激励电平。

图 1. 使用扇出缓冲器创建大量单输入频率副本

2021-11-23 17:45:07 1769

1769

IDT 还提供另一个更简单的 CMOS 缓冲器系列,即5PB11xx系列,由五个时钟扇出缓冲器成员组成,其中最后两位数字代表输出数量。这些缓冲器是非常高性能、低抖动、低偏移和传播延迟、非常低功耗的直接 CMOS 扇出缓冲器。

2022-05-05 15:41:13 1500

1500

KOYUELEC光与电子提供技术支持有容微电子GM50301:超低附加抖动差分输出时钟缓冲器

2022-05-07 11:38:45 2271

2271 KOYUELEC光与电子提供技术支持,有容微电子GM50101:超低附加抖动时钟缓冲器。

2022-05-07 11:40:15 1071

1071 的扇出型缓冲器,是一种将一路时钟源信号通过频率复制生成多路时钟信号的器件,通常时钟缓冲器还兼具有时钟分配,格式转换和电平转换的功能。 对于需要多路时钟信号的电子系统来说,时钟源加时钟缓冲器的方案可以有效降低系统成本,简化电路设计,为系统多个组件提供多路参

2022-10-18 18:36:54 18409

18409

测量扇出缓冲器中的附加抖动

2022-11-04 09:52:08 0

0 ADCLK944是一款超快型时钟扇出缓冲器,采用ADI公司专有的XFCB3硅锗(SiGe)双极性工艺制造。这款器件设计用于要求低抖动性能的高速应用。 该器件具有一路配中心抽头、差分、100

2023-01-04 17:07:41 805

805 1 到 4 扇出缓冲器-74AVC1T1004

2023-02-16 21:16:26 0

0 1 到 4 扇出缓冲器-74AVC9112

2023-02-21 19:33:20 0

0 GRANDMICRO有容微电子GM50101:超低附加抖动时钟缓冲器

2023-03-02 11:06:16 661

661

1 到 4 扇出缓冲器-74AVC1T1022

2023-03-03 19:53:47 0

0 DS34T10x和DS34S10x TDM分组(TDMoP)器件利用抖动缓冲器来补偿分组网络中存在的分组延迟变化(PDV)。本应用笔记解释了PDV及其对通信质量的影响。讨论了抖动缓冲器的功能和类型。本文还介绍了如何在TDMoP器件中设置抖动缓冲控制器的参数,以最大程度地减少PDV的影响。

2023-03-08 18:20:00 649

649

时钟缓冲器选型目录

2021-11-19 16:38:53 789

789

Diodes(达尔科技)是全球主要的差分时钟IC供应商。Diodes的差分时钟讯号缓冲器产品组合涵盖了多种不同输出讯号(LVPECL,LVDS,HCSL,LowpowerHCSL)与输出端口数

2022-10-19 11:08:24 350

350

三态输出的缓冲器有哪些用途? 三态输出缓冲器是一种电子元件,其主要作用是将一个输入信号转换成一个可以控制多个输出设备的信号。这种缓冲器可以被用于一系列的应用,包括数码电路、计算机、消费电子设备、通信

2023-09-21 15:55:36 1607

1607 等应用已集成越来越多的PCIe终端,矽力杰新一代高性能PCIe时钟缓冲器SQ82100可以为系统提供20路超低附加抖动的LP-HCSL参考时钟,能够简化系统布局,进一步提高

2023-12-20 08:19:38 240

240

电子发烧友App

电子发烧友App

评论