你好我在做FPGA向FX3写数据的过程中遇到了一些问题想要明确一下:

(缓冲区的大小设置为16kB,数据总线位宽为32位,水印值为6)

1、如果以16kB为单位写,这时候pktend_n信号是否可以

2024-02-28 07:45:10

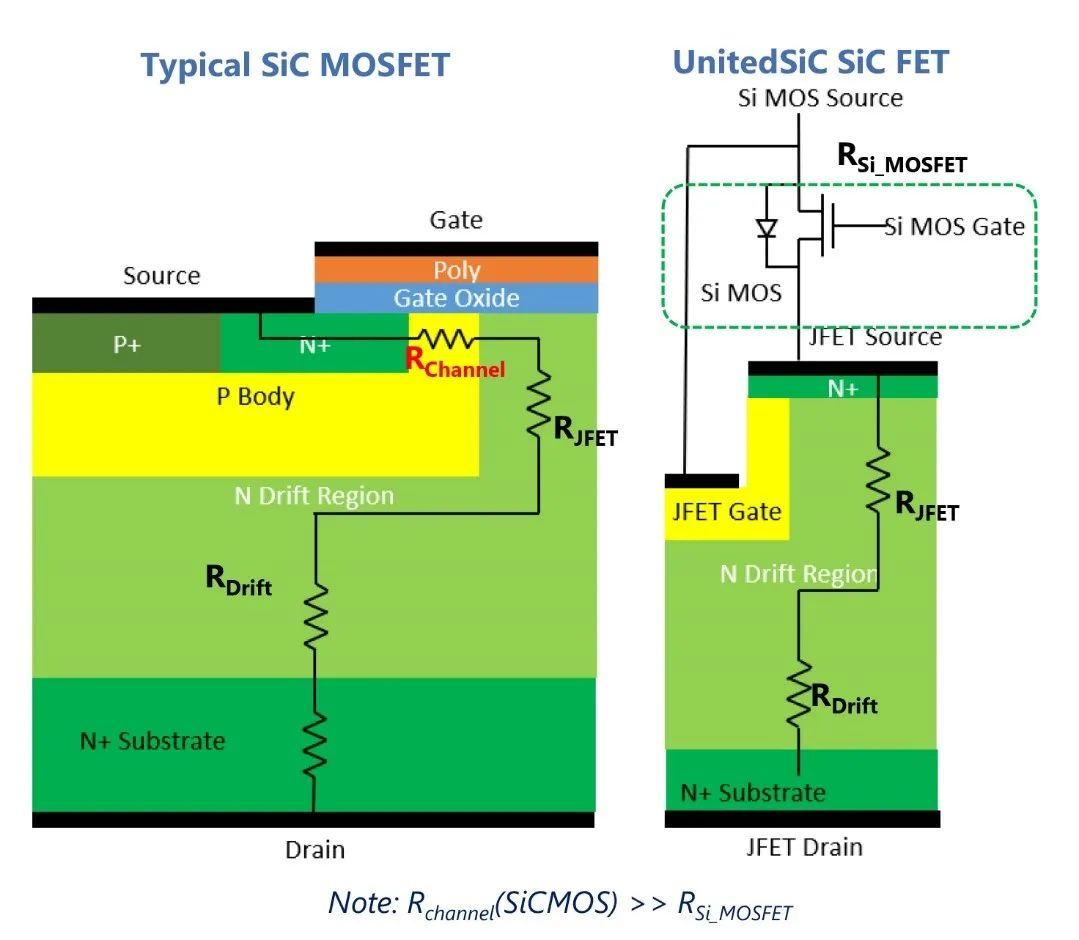

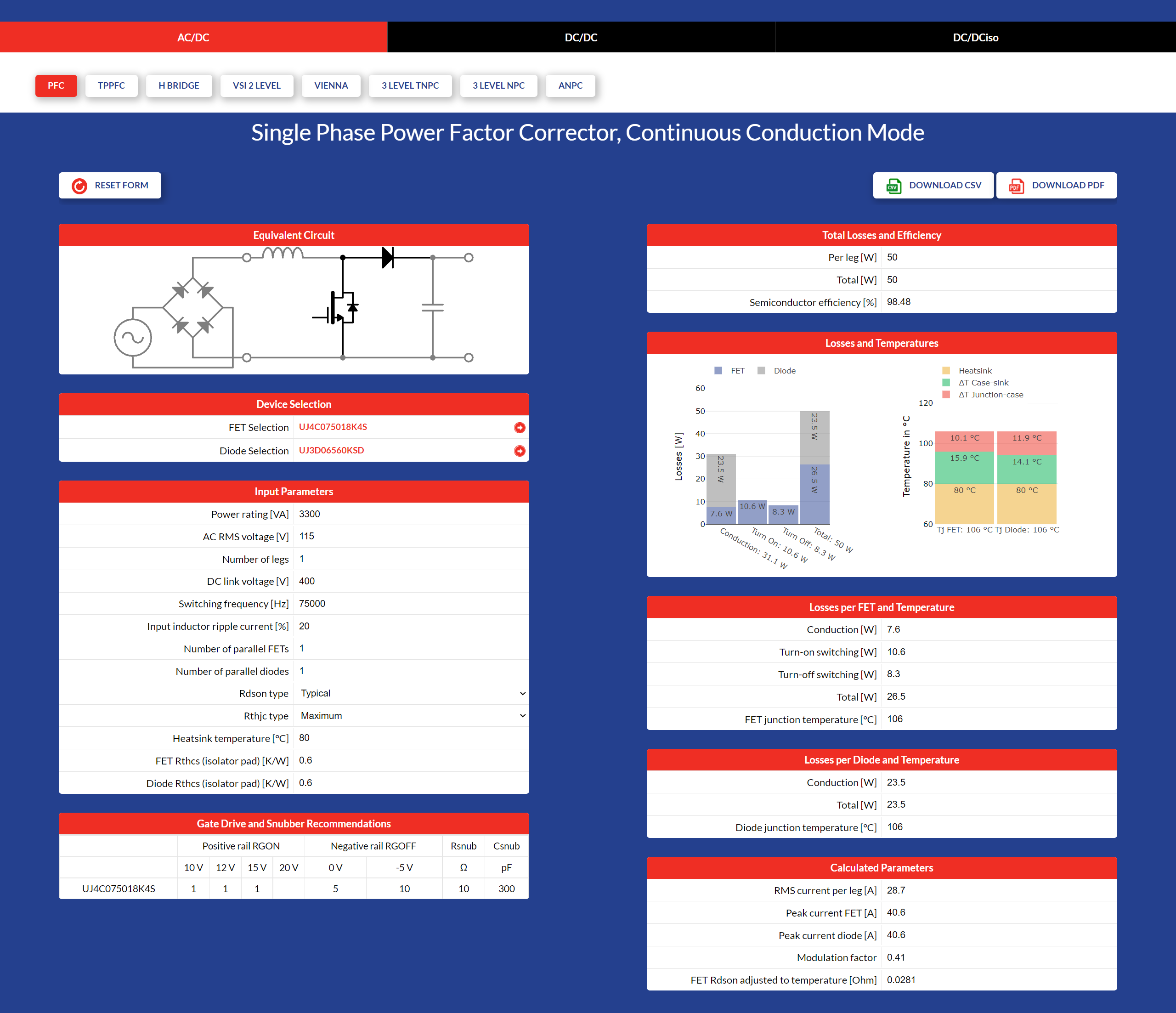

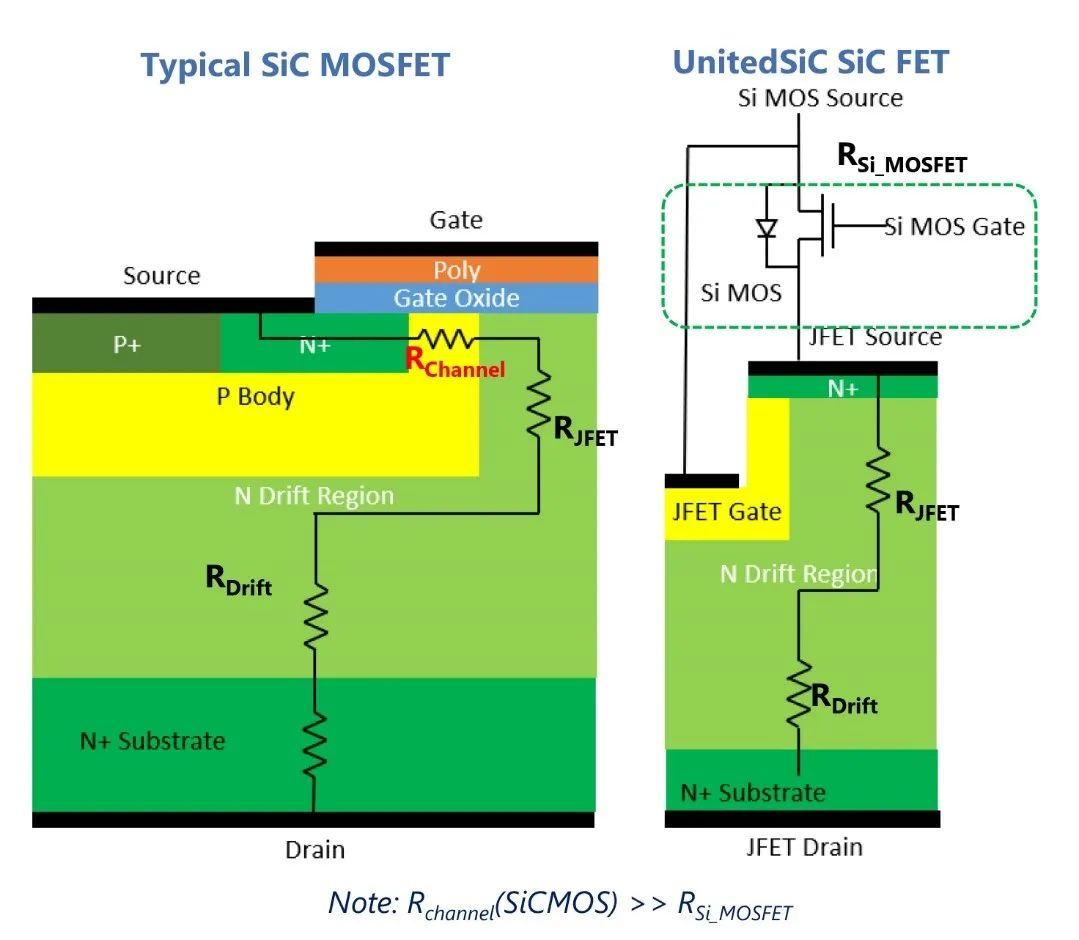

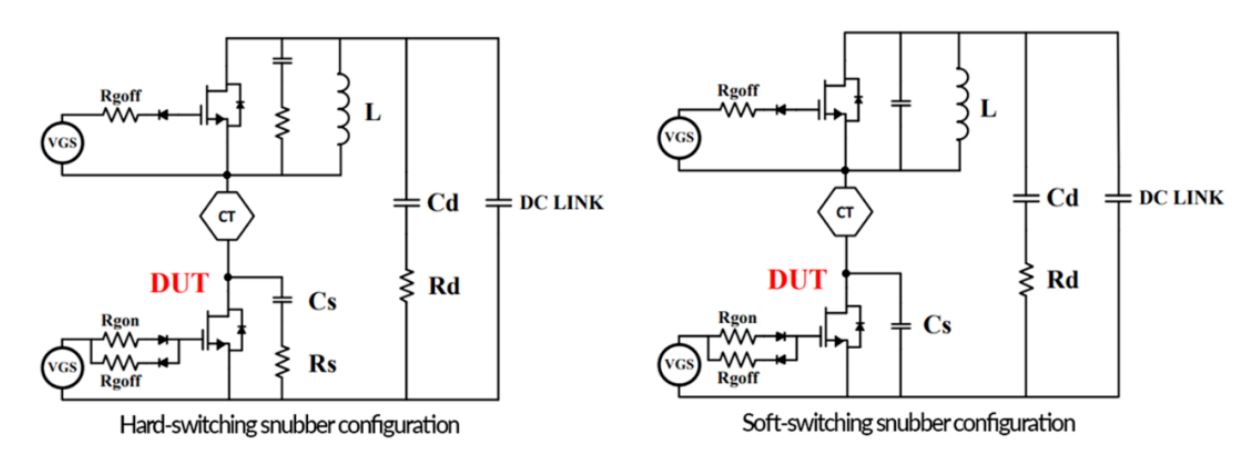

基于独特的共源共栅电路配置,具有出色的反向恢复功能。在共源共栅电路配置中,一个常开SiC JFET与一个Si MOSFET封装在一起,形成一个常闭SiC FET器件

2024-02-26 19:57:09

电子发烧友网站提供《热敏FET使用指南.pdf》资料免费下载

2024-02-22 09:35:30 0

0 TLE9855QX 过流定义。 CAN有人向我指出如何测量Fet的过电流的方向。 我理解高级功能。 我想要一些东西来详细定义如何感知过流。 Fet 的过流是用栅极电流还是温度来感应?

2024-01-31 06:17:41

我们使用恩智浦的以下微控制器(LPC3250FET296/01)已经有一段时间了。我们目前在70°C的热测试中出现故障,有时在环境温度下也会失败。有人对为什么控制器会在特定温度下自行重启有任何建议吗?控制器重新启动/重置的潜在原因是什么?任何建议将不胜感激。

2024-01-31 06:10:08

准备设计一款输入48V,输出12V/20A有源钳位正激电源,在使用ADP1051时,遇到了一些问题,烦请帮忙解答。

1.ADP1051与PC机无法连接。ADP1051外围电路参考数据手册及应用手

2024-01-08 07:38:51

1概述 PC9511/21系列电子保险丝的设计目的是保护输出(OUT)上的电路免受瞬态影响在电源总线(IN)上和大的浪涌电流。同时保护电源总线不受不希望的输出短路的影响以及意外的过载情况。当输出斜坡

2023-12-25 18:50:25

本人刚接触关于CCD的知识,正在利用AD9923A调试ICX209AK,但在配置寄存器时遇到了一些问题,想问问各位做过类似项目的:

1.对于CCD所需的H1、H2、RG等信号,怎么确定它的上升沿

2023-12-22 07:58:47

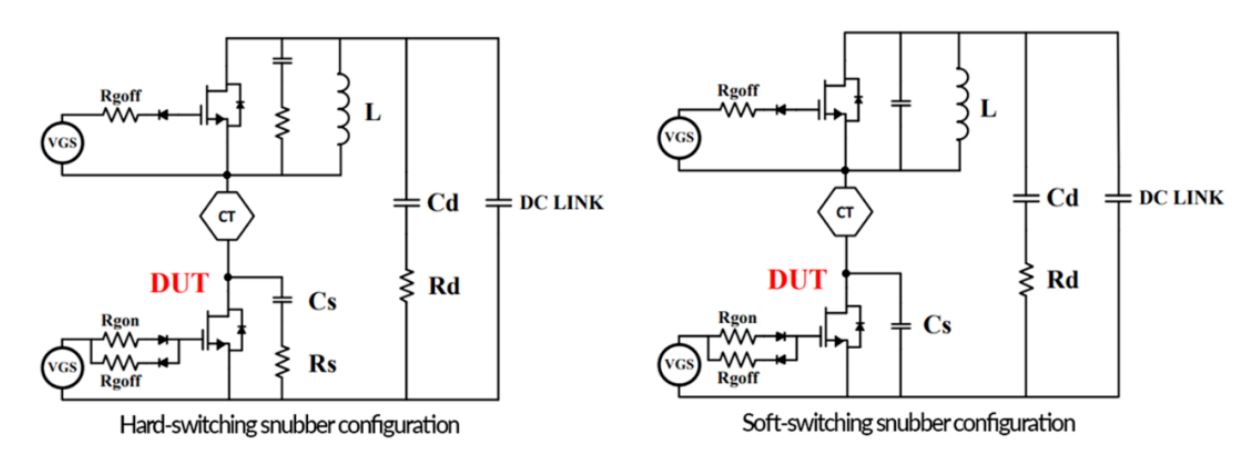

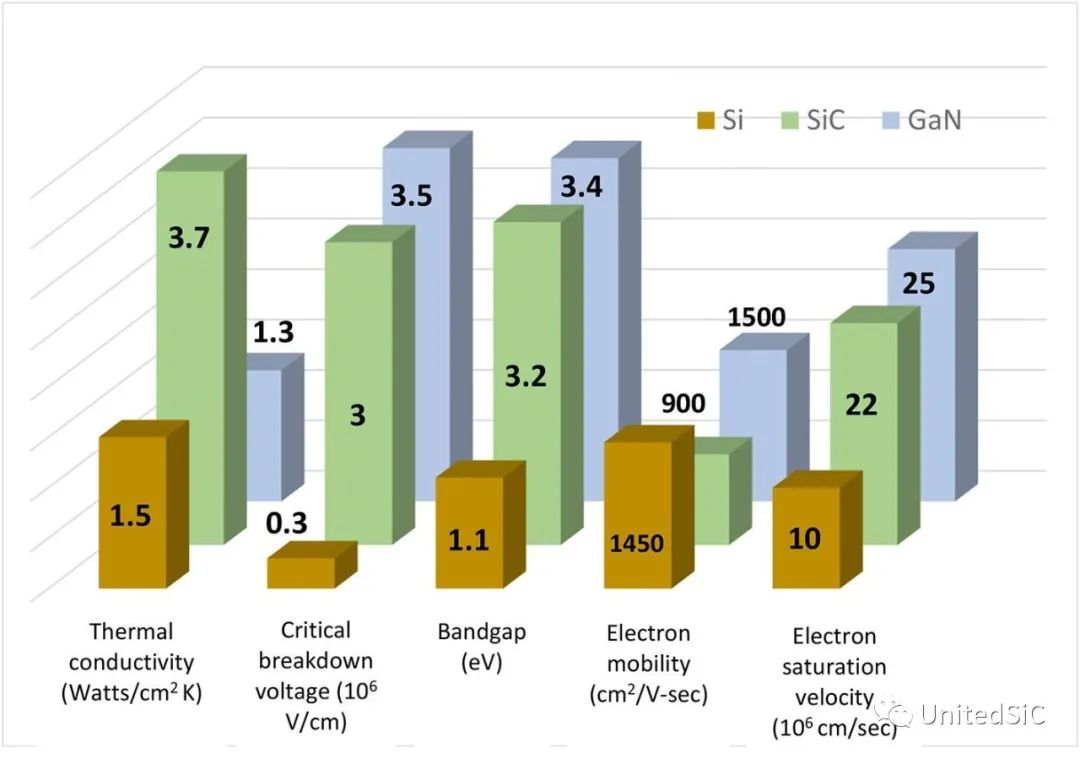

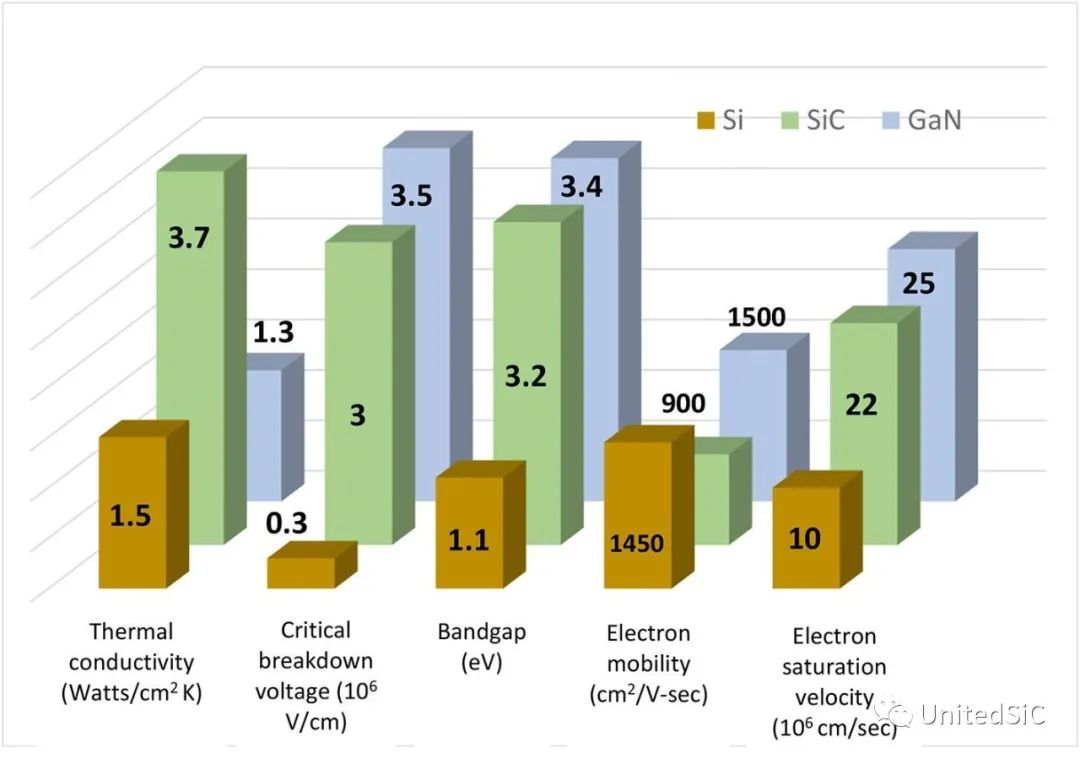

充分挖掘SiC FET的性能

2023-12-07 09:30:21 152

152

UnitedSiC SiC FET用户指南

2023-12-06 15:32:24 171

171

还没使用SiC FET?快来看看本文,秒懂SiC FET性能和优势!

2023-11-29 16:49:23 273

273

现在正在做一个项目,需要做4-20ma的标准输出,

数据手册上有一个地方没有理解透彻,导致我一接电,直接把我的CPU烧了!

AD421内置一个可选稳压器,用于为自身及发射器中的其

它器件供电

2023-11-24 07:39:18

手册的图49以及图33进行更改画出的电路图,请问精通该芯片的工程师,上面的电路能实现我前面所说的5点要求吗?如果有问题的话,需要如何修改才能实现要求?

小弟还有一些关于AD603的一些问题想让相应

2023-11-20 07:19:44

请问哪位大神知道AD8436的内部FET的10K的电阻的温度系列是多少呢?

2023-11-20 06:57:03

极少的微妙之处或细节会使开发者们疏忽大意,从而在代码中引入严重的安全漏洞。 在这篇博文中,我们将分享在实际 Python 项目中遇到的 10 个安全陷阱。我们选择了一些在技术圈中不太为人所知的陷阱。通过介绍每个问题及其造成的影响,我们希望提高人们对

2023-10-30 10:34:49 205

205 fet430uif的仿真器 的驱动装不上

2023-10-27 06:55:04

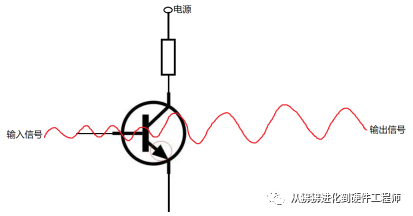

晶体管和FET给人的印象是具有信号放大的功能,即当输入信号通过晶体管或者FET后,输出信号被直接放大。

2023-10-21 10:23:07 598

598

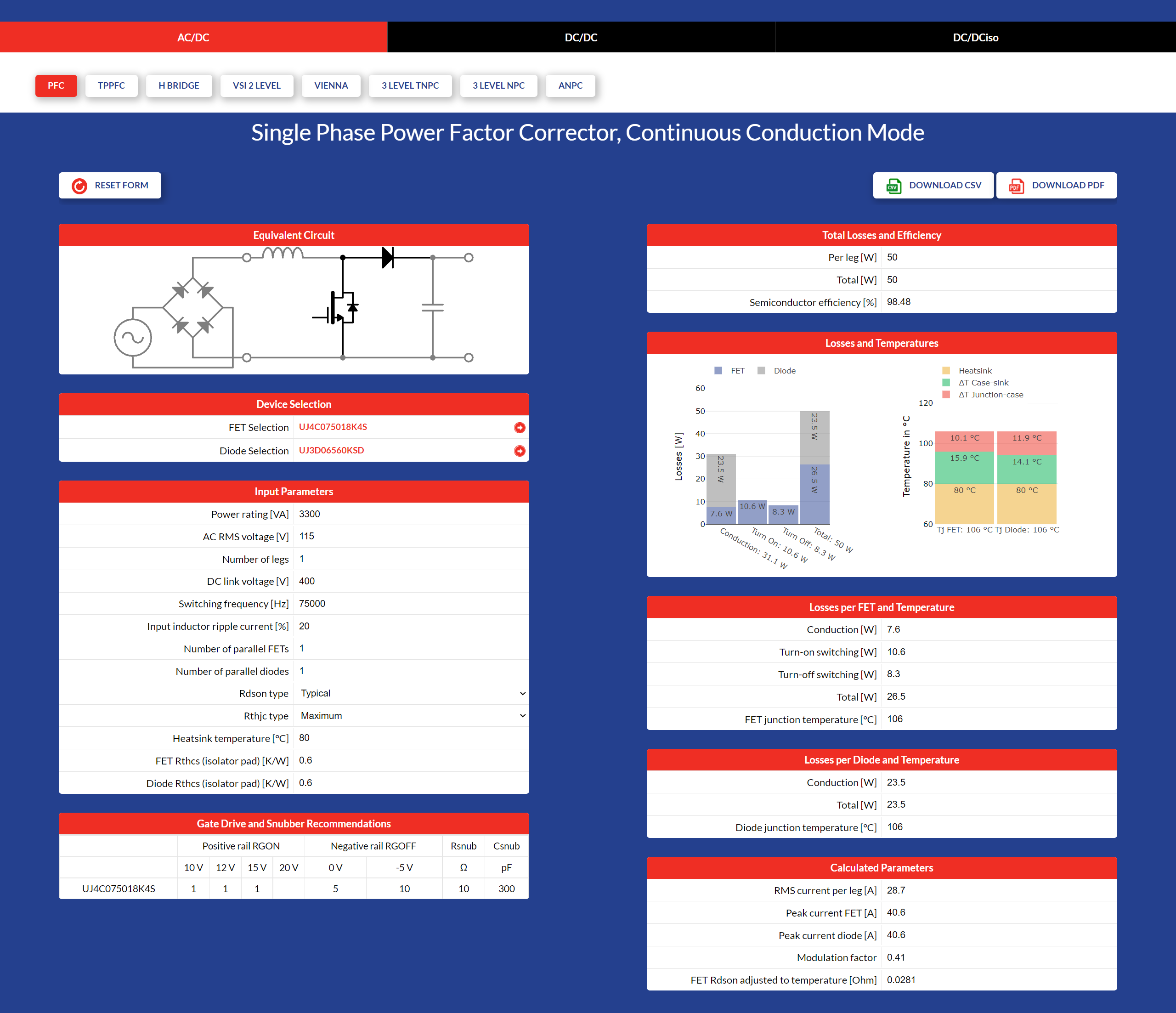

联合SiC的FET-Jet计算器 — — 从SIC FET选择中得出猜算结果

2023-09-27 15:15:17 499

499

要Vue3 目前已经趋于稳定,不少代码库都已经开始使用它,很多项目未来也必然要迁移至 Vue3。本文记录我在使用 Vue3 时遇到的一些问题,希望能为其他开发者提供帮助。

2023-09-13 10:16:15 487

487

基于FET的实用级联放大电路,电阻R4和R5构成FET Q2的分压器偏置网络。R3是Q2的漏极电阻,用于限制漏极电流。R2是Q1的源极电阻,C1是其旁路电容。R1确保在零信号条件下Q1栅极的零电压。

2023-08-01 16:49:20

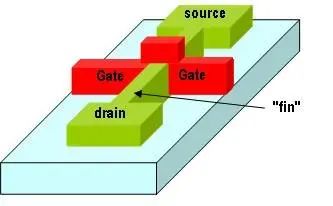

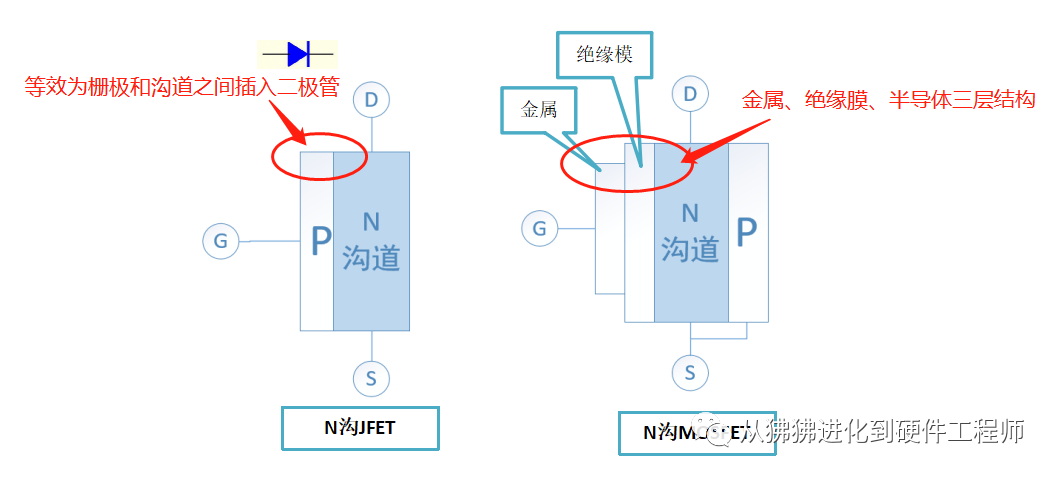

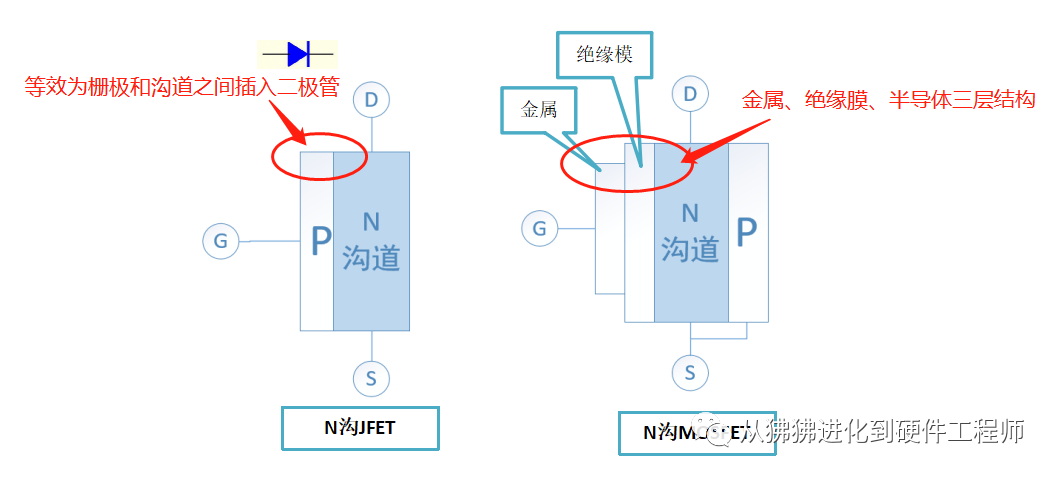

FET 的全名是“场效电晶体(Field Effect Transistor,FET)”,先从大家较耳熟能详的“MOS”来说明。

2023-07-12 17:24:29 1034

1034

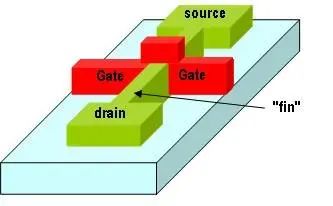

下图是N型FET的结构图,左边是JFET,右边是MOSFET。电流流过漏极和源极之间的部分称为沟道。JFET的栅极和沟道之间有等效二极管(PN结),所以称为结型FET。

2023-06-23 17:09:00 2805

2805

使用 Simulink 中的 Scope 功能可视化一些输出。

我使用的是 S32K144EVB 和 MATLAB R2017a。

有谁知道我如何设置 PIL 模拟的环境以及在哪里包含我的 C 代码项目?

2023-06-08 08:47:27

我们目前正在为我们的汽车项目使用 Layerscape 处理器LS1043A和 PMICMC33PF8200A0ES。我们有一个参考设计,它使用 CPLD 来实现处理器复位。但是我们没有在我们

2023-06-07 06:53:46

毫秒的延迟内上升:

在 PCB 启动期间,CPU_VDD 曾在短时间内高达 11V(11 伏)

一些问题:

我可以完全通过 UBOOT 调试该问题吗?或者需要一个 linux 层来正确设置

有没有

2023-06-06 09:03:09

个板在“欢迎使用 LS1046 BL31 阶段”后停止。

设计中是否需要做一些事情,或者是由于组装不当(因为 4 个中有 2 个可以完美启动)。同样的问题也出现在 6 张卡片中的 2 张原型模型中。

2023-06-05 07:21:17

数据并执行转发特定数据等任务。

我们已经在LS1046A上成功启动了Linux,并且PCIe和以太网通信已经建立。

请允许我确认以下内容:

是否有任何参考项目可用于在主机端通过 PCIe 驱动

2023-06-02 10:26:17

我们有一个带有 Marvell 88E2180 PHY 的定制 LS1043A 板,我们使用配置为 SGMII 的两个端口连接到 SerDes 通道 A 和 B。(SerDec 配置 = 3355

2023-06-01 08:04:20

最近在研究一个无人机电池管理系统,RDDRONE-BMS772。文档中关于电池平衡的内容不清楚——芯片组是内置 FET 还是只是驱动器?

2023-06-01 07:23:40

我们有两个关于 ls1046a usb 的问题:

1、我们将fsl-ls1046a.dtsi中的“dr_mode”改为“peripheral”,用USB线(Type-A to Type-A)连接我们

2023-05-31 08:14:08

我有一个 LS1043A RDB。它的 SD 插槽有一个包含默认 BSP 映像的可引导 SD卡。启动时,u-boot 报告 SoC 的四核频率为 1.6 GHz。

启动过程完成后,我使用以下命令检查

2023-05-30 07:55:43

大家好..我们在我们的项目中使用 LS1043ARDB..我们订购了 codewarrior 网络应用程序许可版本。目前我正在使用 Evalutin Codewarrior IDE。如何在

2023-05-30 06:05:49

我对内核恐慌有一些疑问。我使用 LS1046A 作为服务器端,我的 PC 作为客户端。

PC通过telnet输入命令:iperf3 -c 192.168.1.254 -t 600 -R

经过

2023-05-29 08:35:23

我遇到了 NXP LS1046A RDB 的问题。它运行良好,但突然无法连接到主机。当我尝试使用 minicom 将它连接到 Linux 主机时,它没有连接到 ttyACM0。它抛出“没有这样的文件

2023-05-24 13:20:37

我在使用 CSEc 模块时遇到了一些问题。

我在初始化期间使用 setAuthKey 设置授权密钥,并使用 loadKey 加载和更新 key1。重新上下电后如何管理setAuthKey

2023-05-18 10:24:37

在我定制的LS1046A板上,我们只使用了一个QSPI Flash S25FS512SDSMFI011,通过QSPI_A_CS0/QSPI_A_SCK/QSPI_A

2023-05-18 07:56:21

谁能给我一些关于 MPC5777C 的 MTBF 或 FIT 的信息?

2023-05-18 07:08:47

我想确认此 SODIMM 是否与 LS1046A 兼容

- CT8G4SFRA266.C8FP

我从 LS1046APB.pdf 中了解到 LS1046A 支持的速度高达 2100 MT/s,但我

2023-05-17 13:26:06

我们想在 16 位模式下使用带 DDR4 的 LS1043A 定制板。关于这一点,请按照附件文档确认 LS1043A 和 DDR4 之间的接口连接。

16位模式下MA14\\\\MBG1有什么用。

2023-05-17 11:21:19

UF4C120070K4S 产品简介Qorvo 的 UF4C120070K4S 是一款 1200 V、72 mohm RDS(on) Gen 4 SiC FET。它基于独特的共源共栅电路

2023-05-12 15:34:44

UF4C120070K3S产品简介Qorvo 的 UF4C120070K3S 是一款 1200 V、72 mohm RDS(on) Gen 4 SiC FET。它基于独特的共源共栅电路配置,其中

2023-05-12 15:29:06

UF4C120053K4S产品简介Qorvo 的 UF4C120053K4S 是一款 1200 V、53 mohm RDS(on) Gen 4 SiC FET。它基于独特的共源共栅电路配置,其中

2023-05-12 15:22:37

UF4C120053K3S 产品简介Qorvo 的 UF4C120053K3S 是一款 1200 V、53 mohm RDS(on) Gen 4 SiC FET。它基于独特的共源共栅电路

2023-05-12 15:16:27

UF3C170400K3S产品简介Qorvo 的 UF3C170400K3S 1700 V、410 mohm SiC FET 器件基于独特的级联电路配置,其中常开 SiC JFET 与 Si

2023-05-12 14:20:38

UF3C120150B7S 产品简介Qorvo 的 UF3C120150B7S 1200 V、150 mohm SiC FET 器件基于独特的共源共栅电路配置,其中常开 SiC JFET

2023-05-12 12:44:42

UF3C120080B7S产品简介Qorvo 的 UF3C120080B7S 1200 V、85 mohm SiC FET 器件基于独特的级联电路配置,其中常开 SiC JFET 与 Si

2023-05-12 11:54:23

我试图在我的自定义 #ls1043a 板# 上以 u-boot 级别访问 EEPROM,似乎我只能读取前 16 个字节的#EEPROM#,之后,所有读取都返回 0xFF。请参阅来自 conso

2023-05-12 07:05:44

我正在搜索有关 LS1043A 的信息。

是否有任何关于 LS1043A 及时失效的信息?

或者我应该为 FIT 计算?我正在尝试计算它,但没有足够的信息。

#ls1043a

#ls1023a

#ls1046a

2023-05-06 08:49:13

/MCK0_B) 感到有点困惑。

在上一代相同的主板上,启动并运行不同的 DDR4 内存,我们可以按预期测量 DDR 时钟。

我们了解 NXP 是否无法支持特定的内存配置,但我们想知道在 LS1046A

2023-05-06 08:20:49

我想在我的项目中使用 PCA6416A(带 I2C 接口的 GPIO 扩展器)。然而,因为它是一个安全项目,我需要知道 I²C-BUS CONTROL 组件内部的内容(数据表第 3 页,在框图

2023-05-04 08:51:31

使用 1G hugepage 大小,它是有效的,所以这部分有任何限制或我们需要修改的一些配置这个案例? 顺便说一句,LS1046A 是否支持 512M 大页面大小?

2023-04-20 09:35:12

我们在项目中使用 LS1043A 处理器。我想知道如何启动处理器以及需要哪些软件包。连接闪存和 DDR 的软件是什么?需要所有与 LS1043A 相关的软件程序。您的帮助使我了解处理器并为它编写代码。

2023-04-18 07:33:22

带 2GB DDR3 的定制 LS1043A 板。我们在 PCIe 通道和 2 GbE RGMII 端口上有一个 M.2 WiFi 卡。他们中的任何一个都会使用 iPerf 自行完成一个 Gb

2023-04-18 07:30:13

SFP SRKHR6 = d38a9478 SFP SRKHR7 = 0360f66fbl2 被编程到 qspi 中,而 srkh 寄存器在引导延迟期间被编程,其值如附图所示:启动被释放,但是一旦启动

2023-04-07 09:24:50

。如果我在 OCRAM 中进一步移动 CSF 标头,例如 @0x19000。(为了释放 OCRAM 中的一些空间),ISCB 发出错误信号 ESBC_HDR_LOC:ESCB 标头位置不在 3.5G

2023-04-07 08:56:35

我想为我的 LS1046A FRWY 板启用一些包含在 u-boot 中的 POST 功能。有人可以指出我如何实现这一目标的正确方向吗?

2023-04-07 07:33:59

社会:ls1043aDDR:MT40A2G8VA-062E:B,x5,4 个用于 8GB,1 个用于 ECC。我使用 CW 获取配置文件: 我尝试了两个文件来生成 img他们都在 BL2 运行时遇到问题:使用 (0-2GB) DDR 数据显示不正确:(写入≠读取) 我该如何解决?谢谢

2023-04-07 06:44:48

我们正在开展一个在 LS1043A 板上使用 QSPI 闪存的项目。我们选择的flash来自两个供应商:Macronix和ISSI,我们在每块板上使用2个来自同一供应商的spi flash,一个作为

2023-04-06 07:37:15

我有一个 ls1046a 载板,想使用 QSPI_B(用作 SPI,即仅使用 QSPI_B_SCK、QSPI_B_DATA0 和 QSPI_B_DATA1) 来连接 mcp2518fd(spi 到

2023-04-06 07:29:27

我是一名学生,我有初级水平的编码经验。我有一个 C 项目,我想用 MCUxpresso 导入和编译。为此,我在选择目标设备的 IDE 中创建了一个新的 C 项目然后我将现有项目的所有文件夹导入到这个

2023-04-06 07:23:57

我对第 3 代存储进行了测试。但是 LS1046A RDB 指示此存储是 Gen2。那么,我的问题是:LS1046ARDB 是否支持 PCIE 3.0?

2023-04-06 06:30:54

我在配置 S32K144 的窗口模式时遇到了一些问题,CMP 模块。附件是我的测试演示。我使用了 CMP_0 模块,正输入是 DAC,负输入是输入 0,(逻辑分析仪通道 1,蓝线,设置频率

2023-04-03 09:05:43

我的项目编译了1046,生成的qspi fw完好无损。另外,我试过1043编译:1.找不到qspi的固件。2、如何修改“mkfw”打包的物品?我的qspi芯片是16MB,我只想存rcw和uboot谢谢。

2023-04-03 06:42:09

ADP1046是一款灵活的数字副边控制器,设计用于AC-DC和隔离DC-DC副边应用。ADP1046与ADP1043A引脚兼容,具有一些性能改进和新特性,包括电压前馈、改进环路响应,以及可编程死区

2023-03-31 10:06:59

PN5180A0HN/C2E 版本 3.5PN5180A0HN/C3E 版本 4您好,请问C3e 4版本的产品是否可以直接替代3.5版本的产品? 如果它不起作用,请向我们推荐一些建议等待答案。您好,我想知道c3e version 4的产品不能直接替代version 3.5的产品使用吗?

2023-03-30 08:58:54

我对 TWR-LS1021A 板还很陌生,但我已经遇到了一些问题。我正在尝试启动 OpenWRTLINK,但我完全不知道如何,我用 SD 卡尝试了一些东西但它没有用。有人能帮我理解如何让电路板从出厂默认 yocto 图像以外的任何图像启动的逻辑吗?

2023-03-30 08:13:38

00000000 00238805 00000030: 20104400 00023100 00000096 00000001Model: LS1046A RDB BoardBoard

2023-03-30 07:28:24

我正在使用 LS1043A 处理器,我想执行模拟器。我正在运行命令 ./qemu-system-aarch64 它给出了一个错误显示 aarch64-binfmt-P: 无法打开 '/lib/ld-linux-aarch64.so.1': 没有那个文件或目录请帮助我如何使用 qemu

2023-03-30 07:12:27

我的 cpu 是 ls1046,所有以太网都在 DPAA1 上工作。当MAC10 收到UDP 数据包时,它有一些无法纠正的乱序数据包。我们的板子用MAC10跑10G,集成了FMC工具,运行FMC工具

2023-03-30 07:07:16

MSP FET Tools FLASH Emulation Tool (FET) Debugger

2023-03-29 22:46:22

我们的平台是LS1046A,使用LSDK20.12。我们在“arch/arm64/config/defconfig”中启用了几个选项,如下所示

2023-03-29 09:04:45

我想在实时边缘 yocto 项目中为监狱牢房重新分配资源(can1)。我使用修改后的文件 fsl-ok1028a-rdb-jailhouse.dtb、inmate-ls1028a

2023-03-28 08:26:51

目标:使用 menuconfig 中的一些自定义选项构建 linux 内核,并使用 LSDK 拥有一个 ubuntu:main userland下载 flexbuild_lsdk2108.tgz

2023-03-24 07:33:30

我们有一个使用 LS1046a 的定制板。我们有几个设备连接到专用 IRQ 线路,这些设备是电平触发的,低电平有效。我们使用的是 Linux 5.4 版本的 LSDK。问题是当我尝试启用 IRQ

2023-03-24 06:45:09

我将 VSC8531 和 VSC8575 PHY 连接到 LS1043A 芯片,以创建在 OpenWRT 上运行的 6 端口媒体服务器。我尝试将一个端口配置为 WAN,将其余端口配置为 5 端口交换机。你有关于如何实现这一目标的指南吗?目前,每个端口都是独立配置的,就像 PC 上的单独网卡一样。

2023-03-23 09:13:52

你好呀,使用外设工具,我只想向我的项目添加一个“通用 i2c 驱动程序”(即,基于 CMSIS 的驱动程序):但是,在我进入“选择配置组件”的窗口中,我看到一条警告

2023-03-23 08:15:07

:09:02 +0900)SoC:LS1046AE Rev1.0 (0x87070010)时钟配置:CPU0(A72):1600 MHz CPU1(A72):1600 MHz CPU2(A

2023-03-23 08:10:52

绿色:SDHC_DATA0 蓝色:SDHC_CLK) 参考 JEDEC 标准对于卡识别模式,主机应在 CMD1 参数中发送正确的访问模式在空闲状态之后,但在我的板上没有发送 CMD1 命令。我想知道这是否是问题所在。 我对eMMC不太熟悉,你能给我一些建议吗?

2023-03-23 07:42:33

电子发烧友App

电子发烧友App

评论