完善资料让更多小伙伴认识你,还能领取20积分哦,立即完善>

电子发烧友网技术文库为您提供最新技术文章,最实用的电子技术文章,是您了解电子技术动态的最佳平台。

在编写完HDL代码后,往往需要通过仿真软件Modelsim或者Vivadao自带的仿真功能对HDL代码功能进行验证,此时我们需要编写Testbench文件对HDL功能进行测试验证。...

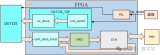

FPGA元器件在高速并行处理和数据传输中有独特优势,FPGA正在前端信号处理中越来越多地代替ASIC和DSP。我们需要的就是这种设计周期短,功能密度高,重组时间短的元器件。...

LOC约束是FPGA设计中最基本的布局约束和综合约束,能够定义基本设计单元在FPGA芯片中的位置,可实现绝对定位、范围定位以及区域定位。...

注意这里的A是double类型的,直接进行imshow会全白,要转化到0-1:A=A./255,或者把double类型转化为整形。...

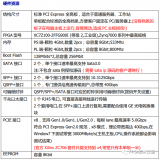

Zynq-7000可扩展处理平台是采用赛灵思新一代FPGA(Artix-7与Kintex-7FPGA)所采用的同一28nm可编程技术的最新产品系列。...

LVDS是一种低压低功耗的高速串行差分数据传输标准,在高速数据互联和数据通信领域得到广泛的应用,主流的FPGA器件都集成了高速的LVDS收发器。...

FPGA 中包含一些全局时钟资源。以AMD公司近年的主流FPGA为例,这些时钟资源由CMT(时钟管理器)产生,包括DCM、PLL和MMCM等。...

AMD FPGA在配置了适当的启动模式后,上电即会按该模式去加载配置文件。以7系列FPGA为例,假设设置模式引脚M[2:0]=3’b001,上电后FPGA会以Master SPI方式尝试从FLASH加载配置文件,其与工程是否含有MicroBlaze IP无关。...

再看末级触发器对BRAM时序性能的影响,下图依次展示了7系列FPGA、UltraScale+和Versal芯片在未使用和使用末级触发器两种情形下时钟到输出的延迟。...

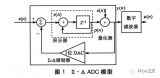

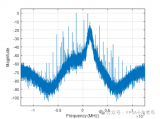

必须将GPS模拟器的数据通过FPGA开发板进行短时间的采集,至少能用于matlab算法上的捕获验证,这个采集时间至少要几ms。...

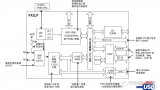

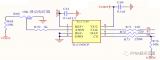

本次设计我们选择一款开发设备,一块廉价的开发板,其中的USB芯片是Cypress的FX2LP系列中的CY7C68013A代,详细的介绍大家可以去Cypress的官网查询。下面简述一下设计思路。...

各行各业纷纷采用FPGA芯片是源于FPGA融合了ASIC和基于处理器的系统的最大优势。 FPGA能够提供硬件定时的速度和稳定性,且无需类似自定制ASIC设计的巨额前期费用的大规模投入。...

ASK即“幅移键控”又称为“振幅键控”,也有称为“开关键控”(通断键控)的,所以又记作OOK信号。ASK是一种相对简单的调制方式。...

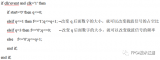

TLC549是一个8位的串行模数转换器,A/D转换时间最大为17us,最大转换速率为4MHz。下图为TLC549的访问时序,从图中可以看出,TLC549的使用只需对外接输入输出时钟(I/O CLK)和芯片选择(/CS)、输入的模拟信号(ANALOG IN)的控制。...

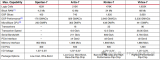

Xilinx7系列FPGA由四个FPGA系列组成,可满足一系列系统需求,从低成本、小尺寸、成本敏感的大容量应用到最苛刻的高性能应用的超高端连接带宽、逻辑容量和信号处理能力。...

首先通过图像采集设备来获取手势图像,通过手势建模将获取的手势图像用数学模型描述出来,最后根据得到的手势识别所需要的模型参量判别出具体的手势形态。...

图像的采集使用的是 NUOXI ZL-008 型号USB 摄像头,该摄像头支持分辨率640*480,帧率 30 帧/秒,增强像素数1200 万,可以满足本文研究中对 图像的清晰度和实时性的要求。...

Xilinx建议使用非阻焊定义的(NSMD)铜材BGA焊盘,以实现最佳板设计。NSMD焊盘是不被任何焊料掩模覆盖的焊盘,而阻焊定义的(SMD)焊盘中有少量阻焊层盖住焊盘平台。...

这款flash芯片的的存储是一个扇区4KB,一个扇区可以存256个字,一个字是8位,一个块是64KB,一共有256个块组成一个存储flash内存。...

上位机才能够在接收数据后正确显示图像。所以每帧图像的开始需要多传输8字节数据,一般规定每次传输一行数据,由于OV7725一行有640个像素,每个像素16位,而以太网每个时钟传输8位数据,因此需要1280个时钟才能传输完一次数据。...