)、锁相环频率合成技术(PLL)、直接数字频率合成技术(DDS)、混合频率合成技术四种实现方式,其中锁相环频率合成器是射频电路中最常使用的一种结构,相比于其他几种结构,PLL结构能够在有限的功耗限制下合成高性能的载波信号。

2015-10-17 11:24:00 1656

1656

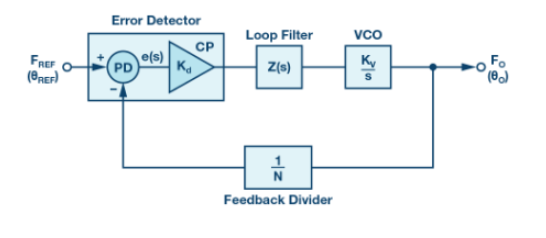

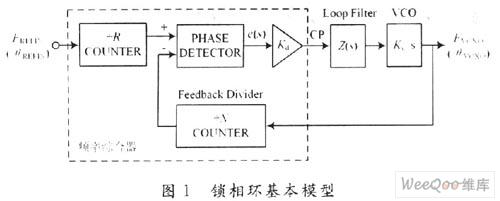

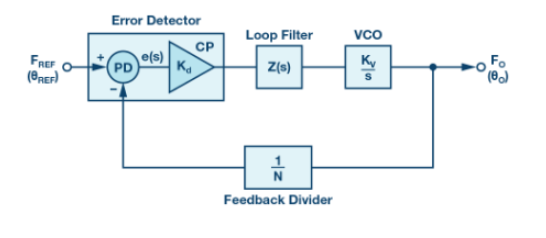

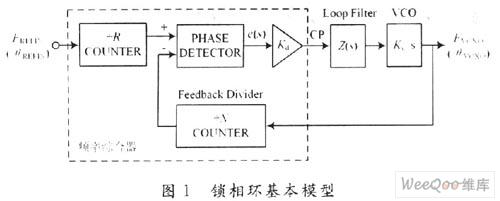

。当比较结果处于稳态,即输出频率和相位与误差检测器的输入频率和相位匹配时,我们说PLL被锁定。就本文而言,我们仅考虑ADI ADF4xxx系列PLL所实现的经典数字PLL架构。 该电路的第一个基本元件是鉴频鉴相器(PFD)。PFD将输入到REFIN的频率和相位与反馈到RFIN的频率和相位进

2021-03-02 16:34:02 3806

3806

ADF4111 - 400 MHz to 6 GHz Broadband Quadrature Modulator - Analog Devices

2022-11-04 17:22:44

ADF4111BCP - RF PLL Frequency Synthesizers - Analog Devices

2022-11-04 17:22:44

最近在调试锁相芯片ADF4001,问题是这样的:我计划用锁相调频,设置载波频率为34.7Mhz,参考频率REFin是用的是有源晶振24Mhz,鉴相频率设为100kHZ,调试好VCO后发现根本无法锁相

2019-03-12 14:43:36

;无线电台基站。 一般说明 ADF4108频率合成器可用于实现上转换和下转换部分的本地振荡器无线接收器和发射器。它由低噪音组成数字鉴频器,精密电荷泵可编程参考分压器,可编程A和B计数器,以及一个双模

2020-07-17 15:17:58

想用ADF4110做锁相环,并实现雷达传感器的LFMCW,雷达传感器自带VCO。采用1MHZ晶振作为参考频率REFIN,雷达反馈信号为分频后信号,范围是2~3Mhz方波,作为RFINA的输入。但是

2018-08-24 11:28:57

(小数 N 模式),可实现更高的相位噪声和杂散性能。使用 49 位分值时,可变模数 Δ-Σ 调制器可以实现极精细的分辨率。ADF41513 可用作整数 N 锁相环 (PLL) 或小数 N PLL,可使

2019-07-09 13:46:26

求一ADF5355_锁相环相关资料,最好中文版,详细点

2017-03-06 23:32:13

数字可调恒压源是用什么方式实现多点电压/电流校准?请具体点,是写一个软件。还是开发另外一套校准硬件设备?

2016-01-12 21:02:40

mA,频率范围为0~1 MHz.详细讲述了该调频电流源实现的重要技术以及相应的公式推导.对所设计的调频电流源电路的性能进行了仿真,仿真结果表明,其输出频率0~1 MHz.幅度0~20 mA内可调,符合

2018-11-29 17:06:14

随着现代电子技术的发展,具有高稳定性和准确度的频率源已经成为通信、雷达、仪器仪表、高速计算机及导航系统的主要组成部分。高性能的频率源可通过频率合成技术获得。随着大规模集成电路的发展,锁相式频率合成

2019-06-20 06:24:14

频率合成技术实现的频率源已经在雷达、通信、电子等领域得到了广泛应用。 本文以GPS信号源设计为参考,介绍ADI公司的频率合成器ADF4360-4在GPS信号源设计中的典型应用。

2019-06-25 07:07:32

1.AD4111与主机通讯的SCLK频率怎么设置?

2.AD4111的内部校准和系统校准有什么区别,一般选哪个,是否一定需要校准?

3.CHANNEL REGISTER中的INPUT[9:0]的输入

2023-12-07 06:22:49

EVAL-ADF4351EB1Z,该板设计用于允许用户评估ADF4351频率合成器的性能,以实现锁相环(PLL)。它显示了该板,其中包含ADF4351集成合成器和VCO,用于输出信号的SMA连接器

2019-03-01 08:03:03

由锁相环构成的间接式频率合成器在无线通信领域发挥着非常重要的作用。通常采用锁相频率合成器的输出信号来作为无线接收机中的本振信号,以使直接频率调制器、频率解调器能够从输入信号中再生载波。如果用MB1504/MAX2620的话怎么能够实现锁相时钟频率源?

2021-04-14 06:47:07

频域中工作的负反馈控制环路。当比较结果处于稳态,即输出频率和相位与误差检测器的输入频率和相位匹配时,我们说PLL被锁定。就本文而言,我们仅考虑ADI公司ADF4xxx系列PLL所实现的经典数字PLL架构

2019-10-02 08:30:00

。图2中有一个在频域中工作的负反馈控制环路。当比较结果处于稳态,即输出频率和相位与误差检测器的输入频率和相位匹配时,我们说PLL被锁定。就本文而言,我们仅考虑ADI公司ADF4xxx系列PLL所实现

2019-01-28 16:02:54

介绍了锁相环路的基本原理,分析了集成锁相环芯片ADF4106的工作特性,给出了集成锁相环芯片ADF4106的一个应用实例,为高频频率合成器的设计提供了很好的思路。 关键词:ADF4106,锁相环,频率合成器,环路滤波器

2019-07-04 07:01:10

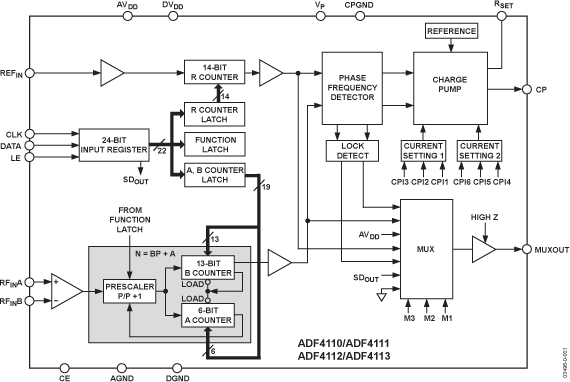

求大婶指导ADF4111频率合成器的编程啊。明明只有四个寄存器却要编写那么多控制字。新人晕了{:10:}

2014-04-27 14:46:03

的频率切换。 频率合成技术是利用参考频率源来产生具有一系列离散的、高准确度、高稳定度频率信号的一项技术。锁相式频率合成器是利用锁相环(PLL)将压控振荡器(VCO)的频率锁定在某一个频率点上,由压控振荡器

2019-06-25 05:00:05

ADF4351锁相环介绍及相关硬件设计ADF4351是ADI公司推出的一款集成VCO的锁相环芯片。其输出频率范围可配置为35MHZ到4400MHZ,这取决于参考频率和寄存器配置。其内部包括整数N

2022-01-11 07:28:51

(DS)、锁相环频率合成技术(PLL)、直接数字频率合成技术(DDS)、混合频率合成技术四种实现方式,其中锁相环频率合成器是射频电路中最常使用的一种结构,相比于其他几种结构,PLL结构能够在有限的功耗限制

2018-09-06 14:32:13

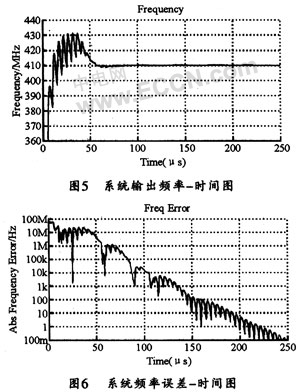

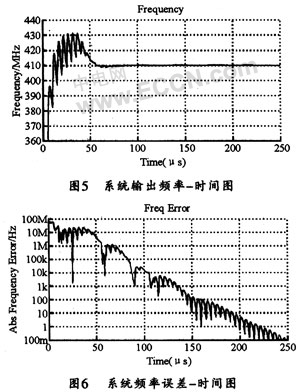

摘要:ADI提供了一套FMCW民用雷达方案,其中推荐的锁相环就是ADF4159。本文着重于采用ADISimPLL用于辅助设计环路滤波器、产生调频波的仿真。(据悉ADISimPLL并不是基于仿真器计算

2019-02-18 13:27:35

如何用集成电路MAX2620和集总LC元件构成窄带VCO电路模块,然后同集成锁相频率合成器芯片MB1504一起构成锁相环式低噪声、高稳定性的锁相频率源电路?

2021-04-07 06:33:42

锁相环是什么工作原理?如何采用FPGA与频率综合器ADF4111相结合的方法实现数字锁相式频率源的设计?

2021-04-14 07:00:20

全数字锁相环由那几部分组成?数字锁相环的原理是什么?如何采用VHDL实现全数字锁相环电路的设计?

2021-05-07 06:14:44

很多开关稳压器都具有外部频率可调(在外电路串接一个电阻即可调频),或者直接给一个同步时钟来设置自己想要的工作频率,它的内部电路设计原理是什么样的呢?跟普通的振荡器有什么不一样的地方?它是通过什么电路来实现这个可调或者同步的功能呢?

2017-05-08 10:34:09

到限制。而锁相频率合成主要是通过晶体振荡器提供的标准频率,在给定的频率范围内产生与该晶体振荡器稳定度相同的大量离散频率信号。 本文介绍用集成电路MAX2620和集总LC元件构成窄带VCO电路模块,然后同集成锁相频率合成器芯片MB1504一起构成锁相环式低噪声、高稳定性的锁相频率源电路的设计方法。

2019-07-09 08:12:36

最近使用ADF5356 | 小数N分频锁相环 (PLL)实现信号源,FPGA控话制SPI,始终不能锁定,初始化配置899MHZ没问题,但是更改N,F值不能锁定,按照手册更改各种参数和配置顺序,硬是

2018-11-18 20:47:39

或射频信号提供本振。频率合成的基本方法有三种:直接频率合成、锁相式频率合成以及直接数字频率合成。锁相式频率综合器是现今应用最为广泛的一种频率综合器,它具有输出频率范围大,杂散抑制特性好的特点。

2019-08-16 06:27:57

或射频信号提供本振。频率合成的基本方法有三种:直接频率合成、锁相式频率合成以及直接数字频率合成。锁相式频率综合器是现今应用最为广泛的一种频率综合器,它具有输出频率范围大,杂散抑制特性好的特点。

2019-08-19 06:40:49

文末下载完整资料 数字式调频收音机设计摘要:本文利用数字锁相频率合成技术构成收音机的电调谐部分,完成收音机的调台、选台、搜索与存储等功能。本文着重介绍了SONY公司生产

2021-12-07 08:50:47

数字锁相环频率合成系统的工作原理CPU控制数字锁相环频率合成系统FPGA实现

2021-04-09 06:20:37

想要实现一个900MHz左右的锁相频率源,不知道用什么芯片好,上网找了一些,但没用过不知道是否好用,求推荐~!

2013-04-16 13:26:18

EV-ADF41020EB1Z,用于ADF41020 PLL频率合成器评估板的评估板。评估用于锁相环(PLL)的ADF41020频率合成器。它包含ADF41020合成器,100 MHz TCXO,电源,USB接口和RF输出。板载有一个有源环路滤波器和一个13 GHz VCO

2019-02-28 07:23:02

评估板EVAL-ADF4152HVEB1Z旨在让用户评估ADF4152HV频率合成器的性能,以实现锁相环(PLL)。该板包含ADF4152HV合成器,环路滤波器,1GHz至2GHz倍频程的压控振荡器

2019-03-01 10:17:42

EV-ADF4153ASD1Z评估板旨在让用户评估ADF4153A频率合成器的性能,以实现锁相环(PLL)。它显示了包含ADF4153A合成器的板,用于RF输出信号的边缘安装SMA连接器,电源连接器

2019-02-27 11:21:47

的频率是由ADF4159设置还是由ADF5901设置?我们的理解是:ADF5901先设置一个初步的频率例如为24GHZ,然后再设置ADF4159产生连续的调频三角波,ADF4159输出的三角波控制ADF5901的输出频率。不知道这样理解可以么?

2018-08-13 06:39:56

工程师您好:ADF4351内部集成VCO振荡器,如果结合外部环路滤波器和外部参考时钟频率能构成数字锁相环吗?如果不能是不是因为ADF4351内部没有鉴相器,如果我想做数字锁相环还要和ADF4002合用吗?能实现位同步吗?期待您们的答复!

2018-09-14 14:23:29

您好,我们目前在做一个调频连续波的雷达,DDS输出50~60MHz,使用ADI的锁相环ADF4108 96倍频至4.8GHz~5.8GHz,扫频周期4ms,点频测试时锁相环的相位噪声还可

2018-08-16 07:18:19

我用信号源作为ADF4350的参考源,寄存器设置时以20M为参考频率,鉴相器频率为20M,环路带宽设为100K,输出频率设为2G,信号源输出20M时,ADF4350能够锁定,输出频率为2G,然后我

2018-10-25 09:19:11

文中在简要叙述锁相环的基本原理的基础上,介绍了 ADF4218L 的主要特点及基于ADF4218L 锁相频率合成器硬件电路的设计和实现。在此基础上讨论了实际电路调试中应该注意的问

2009-08-13 09:59:45 41

41 The ADF4110 family of frequency synthesizers can be used to implement local oscillators

2009-09-16 08:31:00 54

54 介绍了锁相频率合成器的基本原理,分析了高集成N分频的锁相频率合成器ADF4360-4的工作特性,介绍了ADF4360-4在WLAN混频电路中应用实例,并给出了设计方法、控制流程以及程序代码

2010-12-11 15:57:28 22

22 锁相环的研究和频率合成一、实验目的:1. 振荡器(VCO)的V—f 特性的研究2. 对称波锁相环基本特性的研究3. 利用锁相环实现频率合成二、锁相环原理:

2009-03-06 20:02:52 1939

1939

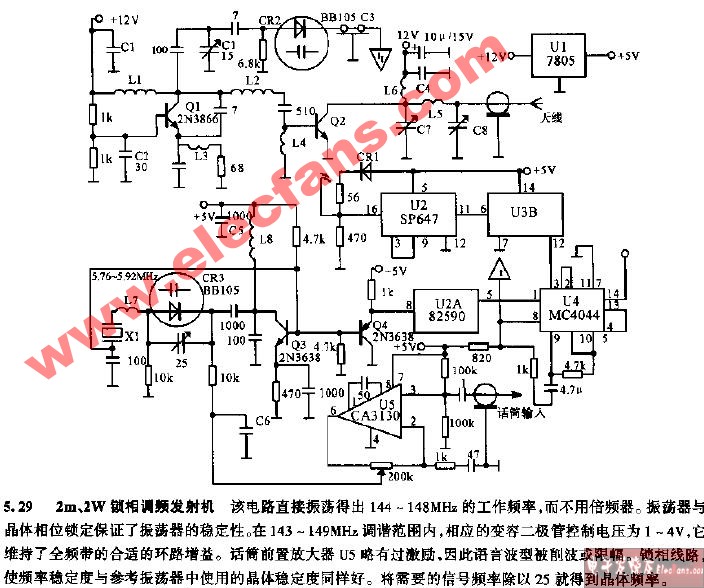

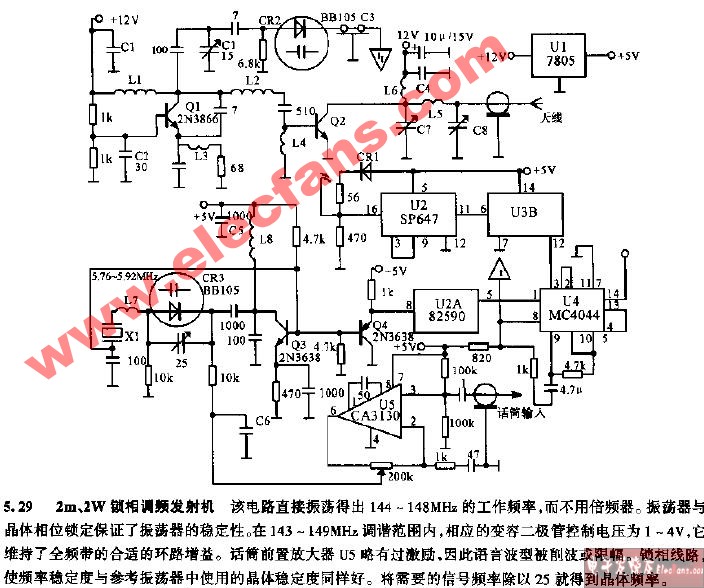

2m,2W锁相调频发射机

2009-03-15 13:31:28 1262

1262

介绍了锁相环路的基本原理,分析了集成锁相环芯片ADF4106的工作特性,给出了集成锁相环芯片ADF4106的一个应用实例,为高频频率合成器的设计提供了很好的思路。

2009-05-05 19:57:57 2585

2585

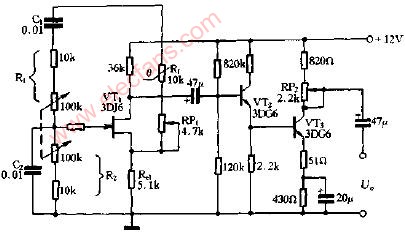

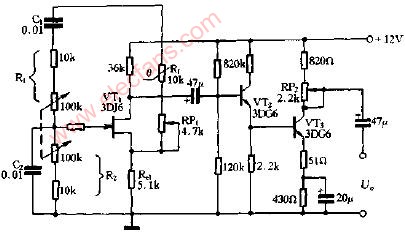

可调频率的文氏电桥振荡电路图

2009-05-07 13:24:46 2771

2771

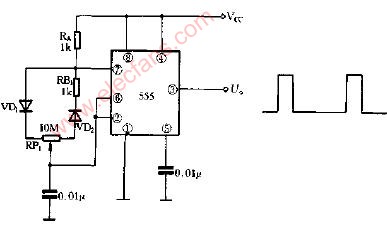

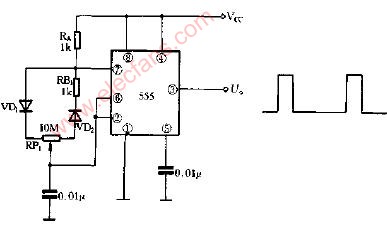

占空比可调频率不变的多谐振荡器电路图

2009-05-08 14:58:53 5274

5274

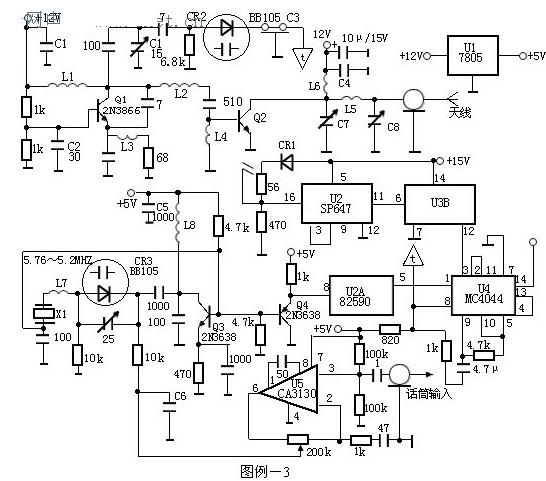

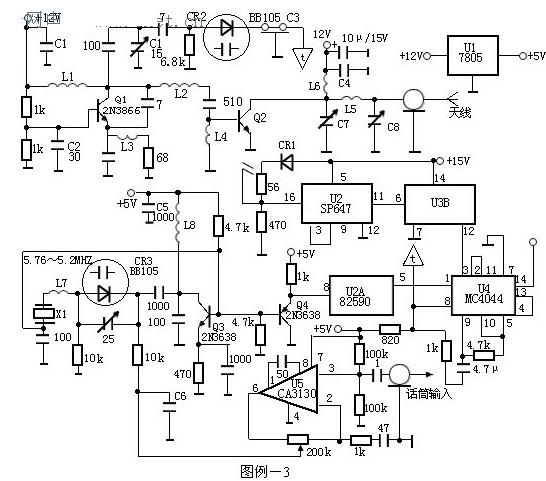

DMR终端锁相调频接收机设计

2004年,欧洲电信标准协会(ETSI)提出新型数字集群通信系统DMR(Digital Mobile Radio),DMR系统与TETRA和iDEN系统相比具有易于实现、成本低廉等优势,已经

2009-12-05 18:02:15 1581

1581 2m,2w锁相调频发射机

2009-12-22 11:38:35 1764

1764

单片机控制的ADF4106锁相频率合成器设计

本文提出了一种基于单片机AT89C2051控制的、利用锁相技术、以ADI公司生产的频率合成器芯片AD4106为核心,来

2010-05-06 10:38:47 2982

2982

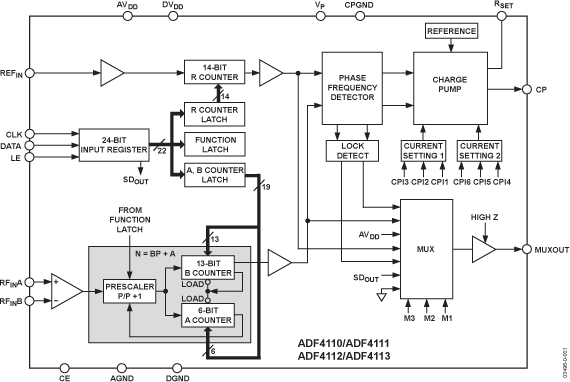

频率合成器可以提供大量精确、稳定的频率作为无线通信设备的本振信号。简要介绍了锁相环频率合成器的基本原理,并利用整数N锁相芯片ADF4112设计了一个宽波段的频率合成器。讨论

2011-05-03 18:20:24 101

101 本文介绍了一种通过快速改变锁相环分频器分频比,来产生线性调频信号的频率综合器,并对影响其扫描线性度的因素进行了分析。此方法拥有频率精度高、易于调试以及线性度好等特

2011-06-20 09:58:54 4065

4065

运用数字锁相频率合成的思想,以ADI公司生产的数字分频器和鉴相器ADF4113为核心,设计了频率范围在1.58 GHz一1.78 GHz的本振扫频源。重点阐述了系统的硬件实现,包括系统设计方案、

2011-09-29 17:04:47 36

36 为得到性能优良、符合实际工程的锁相环频率合成器,提出了一种以ADI的仿真工具ADIsimPLL为基础,运用ADS(Advanced Design System 2009)软件的快速设计方法。采用此方法设计了频率输出为

2013-01-10 16:50:36 81

81 基于FPGA的数字锁相环设计与实现技术论文

2015-10-30 10:38:35 9

9 Xilinx FPGA工程例子源码:用FPGA实现数字锁相环

2016-06-07 15:07:45 37

37 以数字锁相环ADF4351和Xilinx公司的Spartan-6系FPGA为主要元件设计了一个合成频率源。重点讨论了ADF4351的工作原理、两者之间的SPI通信过程、电路板的设计过程,并给出了关键

2017-11-15 11:27:20 32073

32073

公司的频率综合器ADF4111和Altera公司的FLEXlOKE系列FPGA实现频率稳定,精度高,范围为70~90 MHz,步进间隔1 MHz的数字锁相式频率源本振。

2019-02-06 09:20:00 1813

1813

电子发烧友网为你提供ADI(ti)ADF4111相关产品参数、数据手册,更有ADF4111的引脚图、接线图、封装手册、中文资料、英文资料,ADF4111真值表,ADF4111管脚等资料,希望可以帮助到广大的电子工程师们。

2019-02-22 15:20:34

STM32如何实现可调频率、占空比的PWM波形,且可指定输出脉冲个数?

2020-03-12 11:04:06 24012

24012 STM32F4_TIM输出PWM波形(可调频率、占空比)

2020-03-24 11:26:07 13069

13069 模块提供5.4 GHz 的单音本振信号并且利用数控衰减器和放大器实现了输出功率可调,同时也利用ADF5355 的锁相环(PLL)和倍频器为射频模块提供8.4~11.2 GHz 宽频带宽、步进为100 MHz 的可调频本振信号,最终通过硬件电路的设计与调试,以及单片机(SCM)控制程序的编写

2020-11-11 10:39:00 4

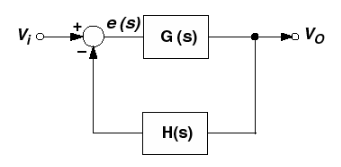

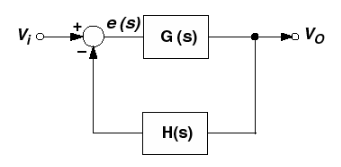

4 锁相环路是一种反馈控制电路,简称锁相环( PLL)。锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。因锁相环可以实现输出信号频率对输入信号频率的自动跟踪, 所以锁相环通常

2020-08-06 17:58:25 24

24 本文档的主要内容详细介绍的是使用MC145170锁相环实现调频锁相环收音机的PCB原理图免费下载。

2020-11-02 17:15:00 77

77 UG-369:ADF4151锁相环频率合成器评估板

2021-04-19 20:14:47 6

6 UG-802:用于锁相环的ADF5355频率合成器评估

2021-04-25 12:23:05 3

3 UG-873:评估ADF4355-3小数/整数N锁相环频率合成器

2021-04-28 14:35:35 5

5 ADF4110/ADF4111/ADF4112/ADF4113:RF PLL频率合成器数据表

2021-04-29 12:21:34 9

9 UG-804:评估ADF4355-2小数/整数N锁相环频率合成器

2021-05-10 08:26:33 8

8 UG-383:用于锁相环的ADF4159频率合成器评估

2021-05-10 13:26:06 1

1 UG-485:ADF4153A小数N锁相环频率合成器评估板

2021-05-16 13:22:43 8

8 UG-1087:用于锁相环的ADF5356频率合成器评估

2021-05-17 09:38:07 4

4 ADF4217:双射频锁相环频率合成器过时数据表

2021-05-17 11:55:55 2

2 用锁相环实现超快频率切换

2021-05-18 20:29:01 9

9 LTC3805-5:可调频率电流模式反激/升压/SEPIC DC/DC控制器数据表

2021-05-23 20:30:21 6

6 UG-389:ADF4xxx锁相环频率合成器的USB转并行转接板

2021-05-24 11:46:02 6

6 UG-686:ADF4155锁相环频率合成器评估板

2021-05-25 16:46:51 4

4 ADF4150HV锁相环频率合成器UG-406评估板

2021-06-03 11:16:33 7

7 电子发烧友网为你提供ADI(ti)EVAL-ADF4111相关产品参数、数据手册,更有EVAL-ADF4111的引脚图、接线图、封装手册、中文资料、英文资料,EVAL-ADF4111真值表,EVAL-ADF4111管脚等资料,希望可以帮助到广大的电子工程师们。

2021-07-25 09:00:02

文末下载完整资料 数字式调频收音机设计摘要:本文利用数字锁相频率合成技术构成收音机的电调谐部分,完成收音机的调台、选台、搜索与存储等功能。本文着重介绍了SONY公司生产

2021-11-24 13:36:10 39

39 ADF435x微波宽带频率合成器搭配外部环路滤波器和外部基准频率使用时,可实现小数N分频或整数N分频锁相环 (PLL) 频率合成器。ADF435x使用一系列分频器,可以在35MHz到 6800MHz范围内运行。

2022-07-23 09:30:42 2

2 锁相环是一种反馈系统,结合了压控振荡器和相位比较器,其连接方式使振荡器频率(或相位)精确跟踪施加的频率或相位调制信号的频率(或相位)。例如,锁相环可用于从固定的低频信号生成稳定的输出频率信号。第一个

2023-01-30 09:50:10 1232

1232

第一部分将重点介绍有关PLL的基本概念,同时描述基本PLL 架构和工作原理,另外,我们还将举例说明PLL在通信系统 中的用途。最后,我们将展示一种运用ADF4111频率合成器 和VCO190-902T电压控制振荡器的实用PLL电路。

2023-06-17 14:47:10 666

666

电子发烧友网站提供《基于ADF4111的锁相环频率合成器设计.pdf》资料免费下载

2023-10-20 14:45:29 0

0 数字锁相环(DigitalPhase-LockedLoop,简称DPLL)是一种基于反馈控制的技术,用于实现精确的时序控制和相位同步。通过相位比较、频率差计算、频率控制、滤波和循环控制,它能够完成

2024-01-02 17:20:25 701

701

电子发烧友App

电子发烧友App

评论