摘要:“VCXO” (压控晶体振荡器)是由晶体决定振荡频率的振荡器,可用控制电压在小范围内进行频率调整。VCXO时钟(CLK)发生器已在多种系统中得到应用,如数字电视,数字音频,ADSL和STB。此应用笔记介绍VCXO CLK发生器的结构,关键参数测量,PCB设计指南,以及对一个应用于MPEG2和AC-3音频设备的VCXO CLK发生器MAX9485的测试结果。

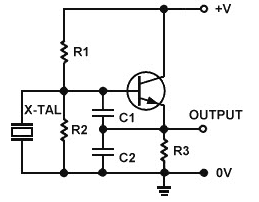

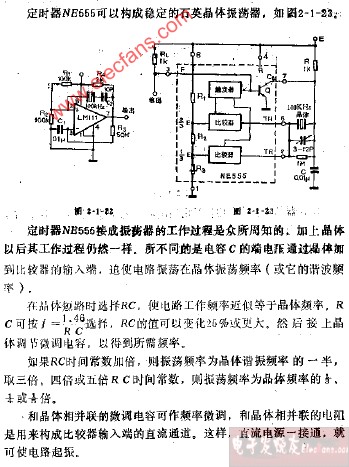

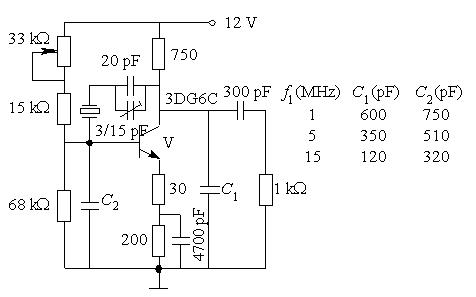

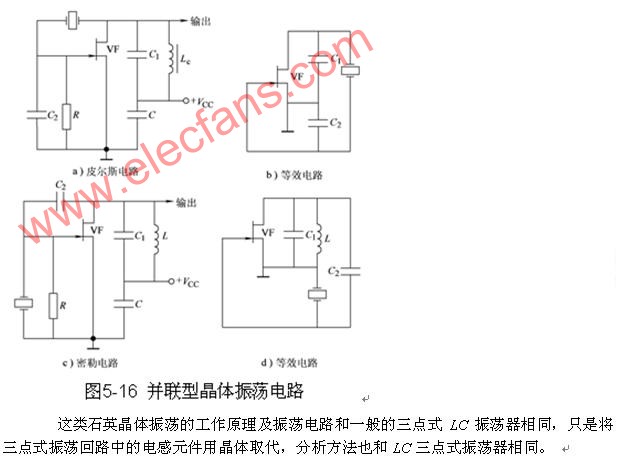

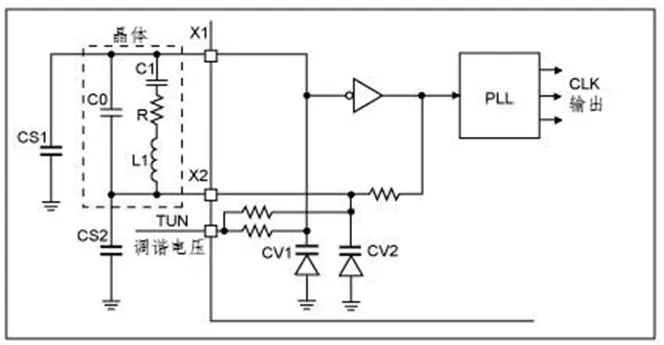

图1. 典型VCXO CLK发生器的结构图

变容二极管CV1和CV2的容值变化会影响到晶振模型,从而改变振荡频率。两个外接并联电容CS1和CS2用来调整谐振范围和中心频率的偏移。按照图1所示的晶振电路,谐振频率可用下式表示:

其中CL是由CV1,2和CS1,2决定的等效负载电容。可准确地表示为:CL = (CV1+CS1) || (CV2 + CS2)。取一阶近似并考虑到C1 << C0和CL,可得到fC的频率增量。

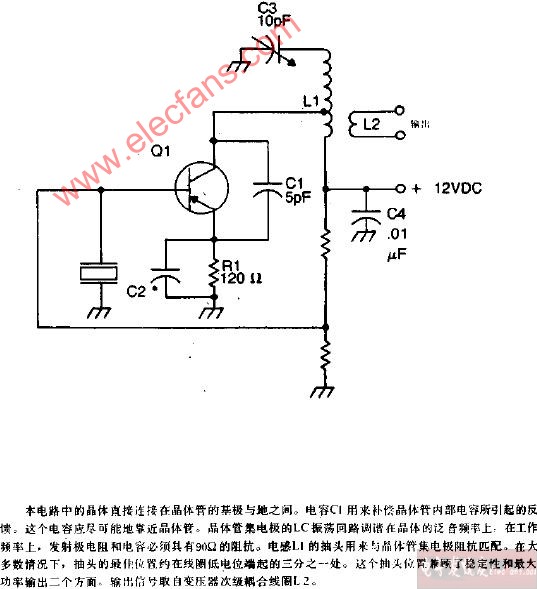

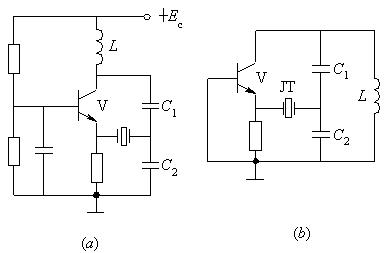

图2为CS1 = CS2时,fC随CS1值变化的典型曲线图。

图2. VCXO频率与并联电容CS1 (CS1=CS2)

利用这一微调特性,可使用VCXO和PLL构成一个具有微调特性的CLK发生器。

VCXO CLK已经在多种系统中得到应用,如数字电视,数字音频,ADSL和STB。Maxim的MAX9485就是这样一款CLK发生器芯片,专为MPEG-2和杜比数字音频(AC-3)应用设计[1],它几乎可以提供数字音频到模拟转换所采用的所有频率,支持从12kHz到96kHz的采样频率。 Maxim还为其它应用设计了各种VCXO CLK发生器。

调谐电压范围为VCXO控制电压的变化范围,此电压控制变容二极管的电容。通常为0V至2V或3V。中心频率为VCXO输出频率范围的中点。牵引范围为变化频率(增大或减少)与中心频率的比值。此比值一般用ppm表示(百万分之一),代表VCXO的相对频率牵引范围。通常牵引范围大约为100ppm至200ppm,取决于VCXO的结构和所选择的晶体。

时钟抖动是CLK发生器的一个重要参数,有多种关于抖动的定义。两个最常用的抖动参数称为“周期”抖动和“周期间”抖动,我们将在第四节详细讨论这些问题。抖动取决于CLK发生器的结构,芯片之间会有差异,不同的应用对抖动的要求也不相同。

图3.

图4.

为了限制VCXO的调谐范围,可通过改变外部并联电容设置向上的调节范围。并联电容取值范围为4ps至7ps,取决于电路板寄生电容。另一方面,向下的调节范围取决于内部变容二极管值,不能由外部改变。为了降低寄生电容对向上频率调节范围的影响,在电路板布局中应尽可能的减少晶体引脚对地的寄生电容,保证引脚与地层和电源层之间的清洁。详细的电路板布局,请参考MAX9485评估板[4]。

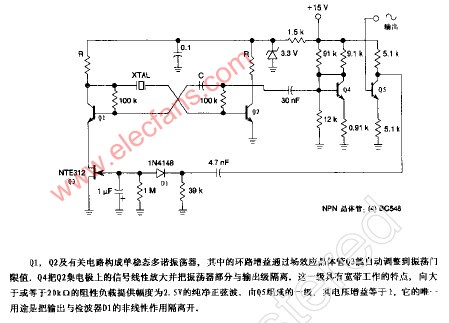

图5. 输出抖动测量

图6. 自触发抖动测量装置

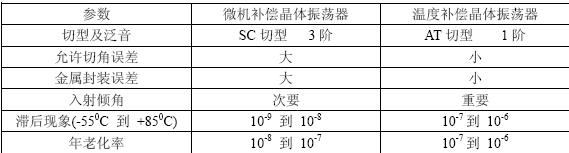

表1. 周期抖动与输出频率

从表中可以看出,一般情况下,频率越高、抖动越低。但如果我们用相对参数描述抖动,如单位间隔(UI),见表的最后一列,则抖动是可比拟的。此外,可以注意到输出频率36.864MHz、33.8688MHz、24.5760MHz和12.288MHz可通过不同的采样频率和比例因数实现,这导致了不同的抖动值。因此,当使用这些频率时,用户可通过选择不同的Fs和比例因数获得最低抖动。

VCXO CLK发生器的结构和应用

“VCXO”,即压控晶体振荡器,其振荡频率由晶体决定,但可用控制电压在小范围内对频率进行调整,控制电压范围一般为0V至2V或0V至3V。VCXO的调谐范围为±100ppm至±200ppm。图1为一个典型VCXO CLK发生器的结构和晶振电路模型。

图1. 典型VCXO CLK发生器的结构图

变容二极管CV1和CV2的容值变化会影响到晶振模型,从而改变振荡频率。两个外接并联电容CS1和CS2用来调整谐振范围和中心频率的偏移。按照图1所示的晶振电路,谐振频率可用下式表示:

其中CL是由CV1,2和CS1,2决定的等效负载电容。可准确地表示为:CL = (CV1+CS1) || (CV2 + CS2)。取一阶近似并考虑到C1 << C0和CL,可得到fC的频率增量。

图2为CS1 = CS2时,fC随CS1值变化的典型曲线图。

图2. VCXO频率与并联电容CS1 (CS1=CS2)

利用这一微调特性,可使用VCXO和PLL构成一个具有微调特性的CLK发生器。

VCXO CLK已经在多种系统中得到应用,如数字电视,数字音频,ADSL和STB。Maxim的MAX9485就是这样一款CLK发生器芯片,专为MPEG-2和杜比数字音频(AC-3)应用设计[1],它几乎可以提供数字音频到模拟转换所采用的所有频率,支持从12kHz到96kHz的采样频率。 Maxim还为其它应用设计了各种VCXO CLK发生器。

VCXO CLK发生器的关键参数

有许多参数用来描述VCXO CLK发生器。其中最重要的是调谐电压范围、中心频率、牵引范围以及时钟输出抖动。调谐电压范围为VCXO控制电压的变化范围,此电压控制变容二极管的电容。通常为0V至2V或3V。中心频率为VCXO输出频率范围的中点。牵引范围为变化频率(增大或减少)与中心频率的比值。此比值一般用ppm表示(百万分之一),代表VCXO的相对频率牵引范围。通常牵引范围大约为100ppm至200ppm,取决于VCXO的结构和所选择的晶体。

时钟抖动是CLK发生器的一个重要参数,有多种关于抖动的定义。两个最常用的抖动参数称为“周期”抖动和“周期间”抖动,我们将在第四节详细讨论这些问题。抖动取决于CLK发生器的结构,芯片之间会有差异,不同的应用对抖动的要求也不相同。

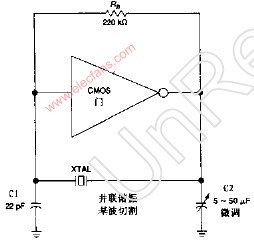

晶体选择和电路板设计

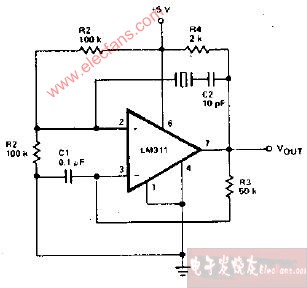

晶体的选择和PCB布局会对VCXO CLK发生器的性能参数产生一定的影响。选择晶体时,除了频率、封装、精度和工作温度范围,在VCXO应用中还应注意等效串联电阻和负载电容。串联电阻导致晶体的功耗增大。阻值越低,振荡器越容易起振。负载电容是晶体的一个重要参数,首先,它决定了晶体的谐振频率。一般晶体的标称频率指的是其并联指定负载电容后的谐振频率。应当指出,此处的标称频率是当CL等于指定负载电容时利用公式(1)计算出的值,但不是利用计算出的值1/(2 π √L1C1)。因此,VCXO的调谐范围与CL的值紧密相关。当负载电容值较小时,VCXO的调谐范围限制在上端;同样,电容值较大时,调谐范围将限制在下端。负载电容的适当取值取决于VCXO的特性。例如,MAX9485设计中,为了均衡调谐范围、调谐曲线中点、同时简化电路板设计,我们选择Ecliptek (ECX-5527-27) [2]具有14pf负载电容的27MHz晶体。使用这样的晶体时,MAX9485具有±200ppm的牵引范围,见图3。应该指出,封装会导致晶体牵引范围的差异。一般金属壳封装比表贴器件(SMD)的牵引范围更大。但是最近DAISHINKU Corp. [5]生产的一款新SMD晶体可达到与金属壳晶体近似的牵引范围。我们测试了这款SMD晶体(DSX530GA),发现外接两个4pf的并联电容时可以实现±200ppm频率牵引范围,见图4。

图3.

图4.

为了限制VCXO的调谐范围,可通过改变外部并联电容设置向上的调节范围。并联电容取值范围为4ps至7ps,取决于电路板寄生电容。另一方面,向下的调节范围取决于内部变容二极管值,不能由外部改变。为了降低寄生电容对向上频率调节范围的影响,在电路板布局中应尽可能的减少晶体引脚对地的寄生电容,保证引脚与地层和电源层之间的清洁。详细的电路板布局,请参考MAX9485评估板[4]。

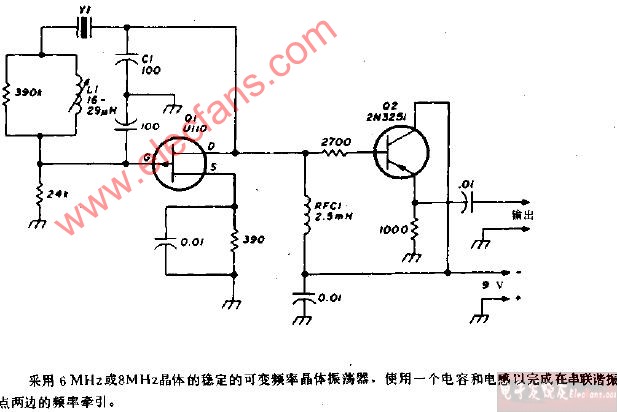

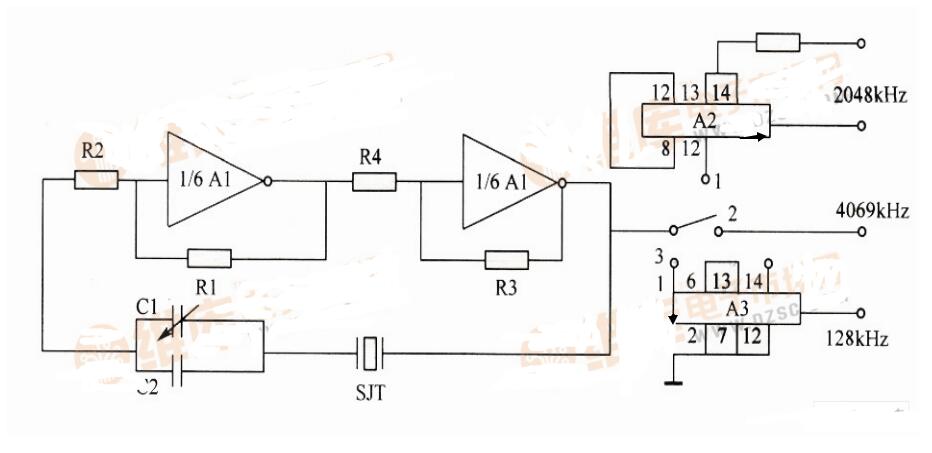

测量输出时钟抖动的设备

对振荡器而言,抖动是一个重要的性能参数。有两个最常用的抖动定义:周期抖动和周期间抖动,详细信息见图5。为了测量抖动,可用高速数字示波器采样一批数据,按照定义计算抖动。Tektronix公司的示波器(TDS 7254)或Lecroy公司的示波器(Wavepro 960)都提供了这类测量软件。我们还可使用高速数字示波器在时域测量周期抖动[3]。图5为装置图。在时域中无法测量周期间抖动。但是,如果每个周期的抖动噪声相互独立并均匀分布,则周期间抖动是周期抖动的1.414倍。MAX9485能产生21种不同的输出频率,取决于不同的音频采样频率和频率比例因数。我们使用图6所示设备测量了各种可能输出的时钟频率的周期抖动,表1为测量结果。

图5. 输出抖动测量

图6. 自触发抖动测量装置

表1. 周期抖动与输出频率

| FOUT | Scaling Factor |

Fs | JP (RMS) | |

| (MHz) | (kHz) | (ps) | (UI) | |

| 73.728 | 768 | 96 | 21 | 0.00155 |

| 67.7376 | 768 | 88.2 | 23.2 | 0.00157 |

| 49.152 | 768 | 64 | 42.6 | 0.00209 |

| 36.864 | 768 | 48 | 40 | 0.00147 |

| 36.864 | 384 | 96 | 37 | 0.00136 |

| 33.8688 | 768 | 44.1 | 44 | 0.00149 |

| 33.8688 | 384 | 88.2 | 41.3 | 0.00140 |

| 24.5760 | 768 | 32 | 66 | 0.00162 |

| 24.5760 | 384 | 64 | 92 | 0.00226 |

| 24.5760 | 256 | 96 | 50 | 0.00123 |

| 22.5792 | 256 | 88.2 | 55.1 | 0.00124 |

| 18.4320 | 384 | 48 | 59 | 0.00109 |

| 16.9344 | 384 | 44.1 | 69 | 0.00117 |

| 16.3840 | 256 | 64 | 134 | 0.00220 |

| 12.2880 | 256 | 48 | 84.8 | 0.00104 |

| 12.2880 | 384 | 32 | 170 | 0.00209 |

| 11.2896 | 256 | 44.1 | 100 | 0.00113 |

| 9.126 | 768 | 12 | 106 | 0.00097 |

| 8.1920 | 256 | 32 | 250 | 0.00205 |

| 4.608 | 384 | 12 | 198 | 0.00091 |

| 3.072 | 256 | 12 | 324 | 0.00100 |

从表中可以看出,一般情况下,频率越高、抖动越低。但如果我们用相对参数描述抖动,如单位间隔(UI),见表的最后一列,则抖动是可比拟的。此外,可以注意到输出频率36.864MHz、33.8688MHz、24.5760MHz和12.288MHz可通过不同的采样频率和比例因数实现,这导致了不同的抖动值。因此,当使用这些频率时,用户可通过选择不同的Fs和比例因数获得最低抖动。

电子发烧友App

电子发烧友App

评论