Si8220,Si8233,Si8234,Si8235 ISOdriver 接口 评估板

2024-03-14 22:30:47

Si5350,Si5351 时钟发生器 计时 评估板

2024-03-14 22:30:46

Si5344 时钟乘法器 计时 评估板

2024-03-14 22:30:44

Si5348 时钟发生器 计时 评估板

2024-03-14 22:30:44

SI5010 时钟和数据恢复(CDR) 计时 评估板

2024-03-14 22:30:31

Si50122-A5 时钟发生器 计时 评估板

2024-03-14 22:30:31

SI5013 时钟和数据恢复(CDR) 计时 评估板

2024-03-14 22:30:31

SI5020 时钟和数据恢复(CDR) 计时 评估板

2024-03-14 22:30:31

新一代FLIR Si2系列声学成像仪共有三个型号,Si2-PD——适用于局部放电检测,Si2-LD——适用于压缩气体泄漏和机械故障检测,Si2-Pro——综合二者的功能点,均可检测!

2024-03-13 18:08:18 397

397 电子发烧友网站提供《Si24R03数据手册.pdf》资料免费下载

2024-03-01 15:44:53 0

0 Si二极管,即硅二极管,是利用硅半导体材料制成的二极管,广泛应用于各种电子设备中。根据不同的功能和用途,Si二极管可以分为以下几类: 整流二极管主要用于将交流电(AC)转换为直流电(DC)。 这类

2024-02-23 11:01:13 146

146

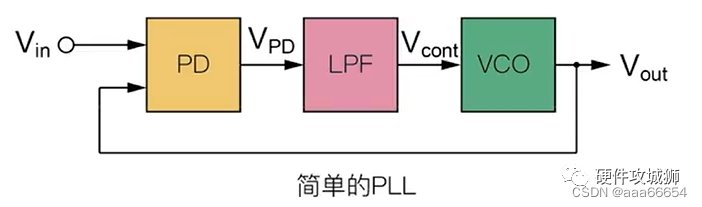

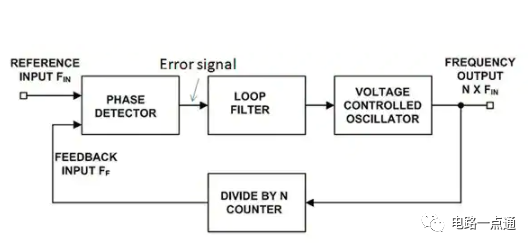

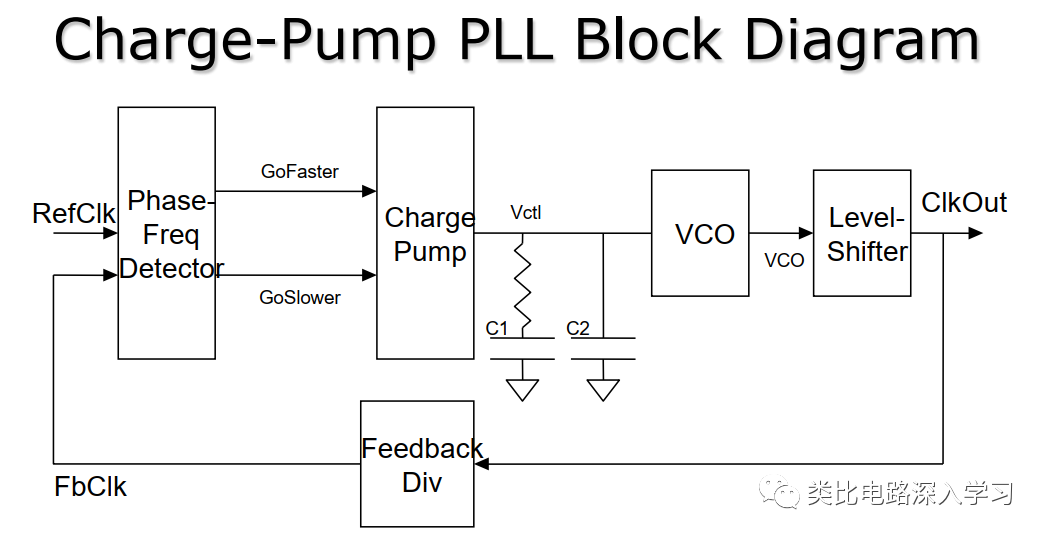

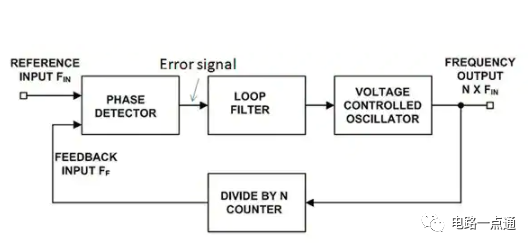

锁相环 (PLL) 是电子系统中最通用、最灵活和最有价值的电路配置之一,因此在许多应用中都有使用。它用于时钟重定时和恢复,作为频率合成器和可调谐振荡器,仅举几个例子。

2024-02-17 14:07:00 161

161

时钟发生器芯片厂家 时钟芯片是一种基于PLL的时钟发生器,采用ADPLL(全数字锁相环)技术,以实现的高频低相噪性能,并具备低功耗和高PSNR能力,可实现小于0.3ps RMS的相位抖动性能

2024-02-04 11:41:14

的灵敏度可调,从而实现更长的通信距离,并且适应噪声环境下工作。Si3933 具有内部时钟产生器,可选择使用晶体振荡器或者 RC 振荡器。用户也可以选择使用外部时钟。

Si3933 支持可编程的数据速率

2024-01-30 16:10:55

Si512 NFC 前端芯片PN532/PN5121. 介绍 Si512 是一款高度集成的 NFC 前端,支持 13.56MHz 下的多种主动/被动模 式非接触式通信方法和协议,支持自动载波侦测功能

2024-01-24 13:51:11 0

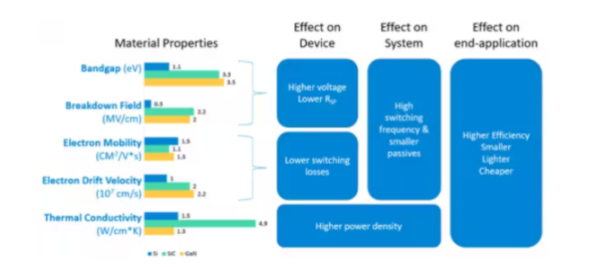

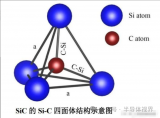

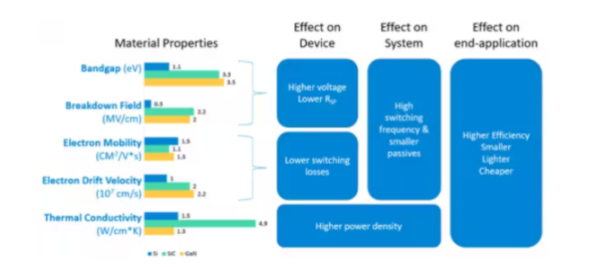

0 SiC是一种Si元素和C元素以1:1比例形成的二元化合物,即百分之五十的硅(Si)和百分之五十的碳(C),其基本结构单元为 Si-C 四面体。

2024-01-18 09:42:01 520

520

14通道自动灵敏度校准低功耗电容触摸传感器动能世纪芯片Si314

2024-01-05 14:32:51 0

0 电子发烧友网站提供《SI4606集成电路IC电压低压英文资料.pdf》资料免费下载

2023-12-29 11:09:55 0

0 时钟发生器芯片厂家 时钟芯片是一种基于PLL的时钟发生器,采用ADPLL(全数字锁相环)技术,以实现的高频低相噪性能,并具备低功耗和高PSNR能力,可实现小于0.3ps RMS的相位抖动性能

2023-12-29 09:29:50

时钟缓冲器芯片时钟芯片是一种基于PLL的时钟发生器,采用ADPLL(全数字锁相环)技术,以实现的高频低相噪性能,并具备低功耗和高PSNR能力,可实现小于0.3ps RMS的相位抖动性能。可输出差分

2023-12-28 13:46:09

如题,目前项目要做一个100m16bit的数据采集卡,看了下贵公司的AD9460,但是差分参考时钟无法选择?

需不需要加一个时钟综合芯片比如Si5324?但类似的这种芯片市场上很不好买到。

如果用elcosc能否推荐个厂家和芯片?还有ad9460能否申请样品?谢谢

2023-12-25 07:44:39

高性能20路PCIe时钟缓冲器新品推介SQ82100PCI-Express(PCIe)是一种高速串行计算机扩展总线标准,主要用于扩充计算机系统总线数据吞吐量以及提高设备通信速度。目前服务器

2023-12-20 08:19:38 240

240

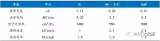

碳化硅(SiC)是一种由硅(Si)和碳(C)组成的半导体化合物,属于宽带隙(WBG)材料系列。它的物理结合力非常强,使半导体具有很高的机械、化学和热稳定性。

2023-12-11 11:29:35 196

196

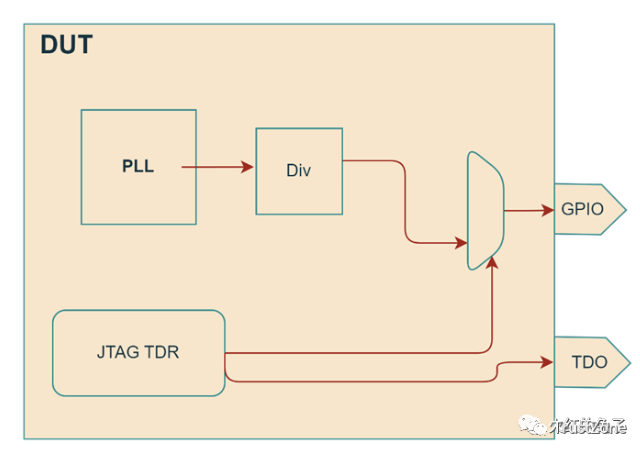

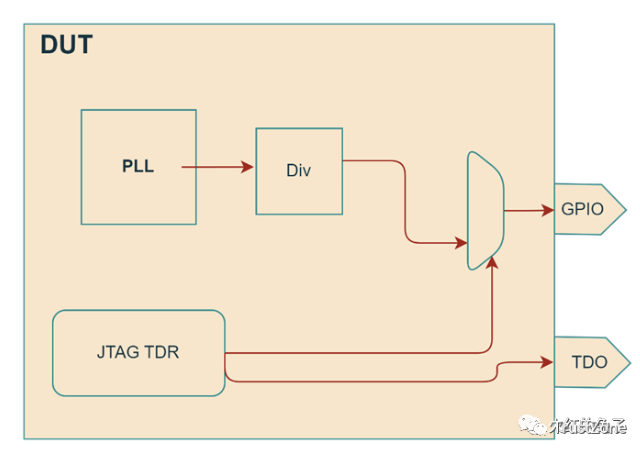

今天想来聊一下芯片设计中的一个重要macro——PLL,全称Phase lock loop,锁相环。我主要就介绍一下它是什么以及它是如何工作的。

2023-12-06 15:21:13 386

386 今天想来聊一聊芯片设计中的一个非常基础的概念——时钟。对于外行来说听到这个词可能会感觉迷茫,猜一个大概意思吧可能也不太准。

2023-12-06 14:41:00 303

303 中的Tick数就是基于模块时钟的)。本系列文章就来详细介绍TC3xx芯片的时钟系统及其具体配置。本文为TC3xx芯片时钟系统的锁相环PLL详解。

2023-12-01 09:37:22 545

545

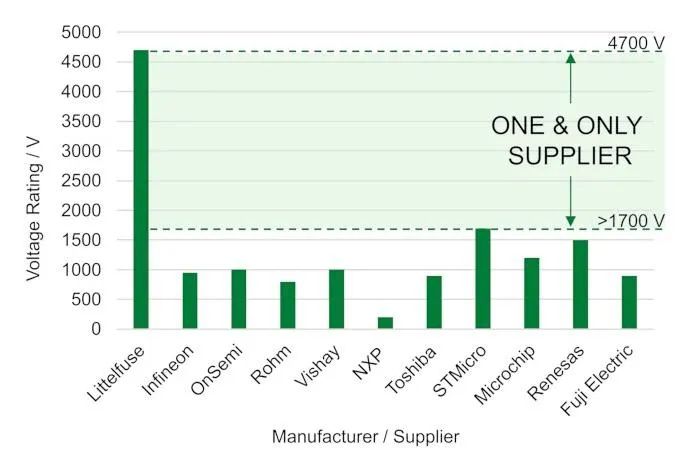

Si对比SiC MOSFET 改变技术—是正确的做法

2023-11-29 16:16:06 149

149

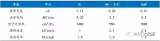

高压分立Si MOSFET (≥ 2 kV)及其应用

2023-11-24 14:57:39 195

195

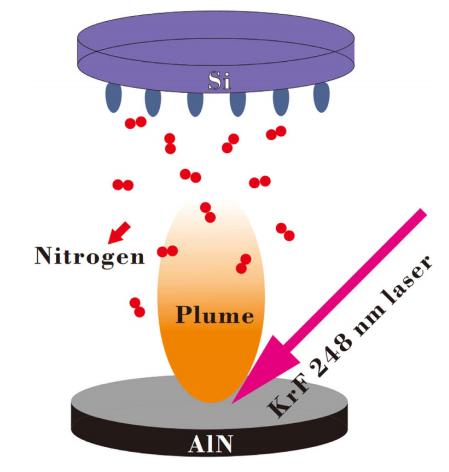

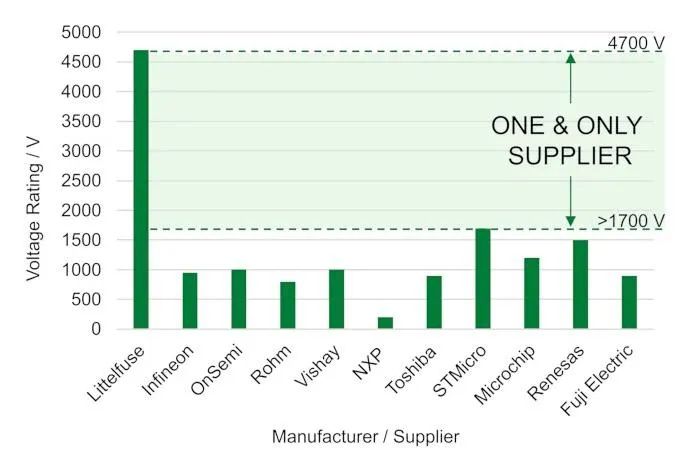

通过有效控制AlN薄膜与Si衬底之间的界面反应,利用脉冲激光沉积(PLD)在Si衬底上生长高质量的AlN外延薄膜。英思特对PLD生长的AlN/Si异质界面的表面形貌、晶体质量和界面性能进行了系统研究。

2023-11-23 15:14:40 232

232

SiC的导热性大约是Si的三倍,并且将其他特性的所有优点结合在一起。导热率是指热量从半导体结传递到外部环境的速度。这意味着SiC器件可以在高达200°C的温度下工作,而Si的典型工作温度限制为150°C。

2023-11-23 15:08:11 486

486

现想用Cadence做PCB的的SI仿真,但是AD8139没有IBIS仿真模型,只有SPICE模型,请问利用SPICE模型能不能进行PCB的SI仿真?谢谢

2023-11-22 08:11:44

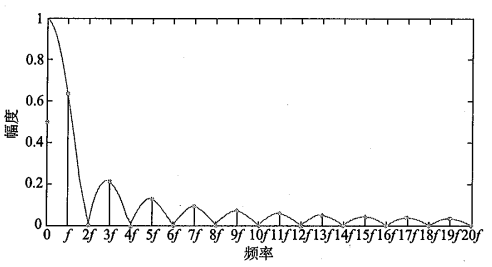

V CO 输出本地参考频率。由于V CO 采用模拟电路, 这将带来元件 饱和、直流漂移、非线性等问题。因此, 全数字锁相环得到了越来越广泛的应用。

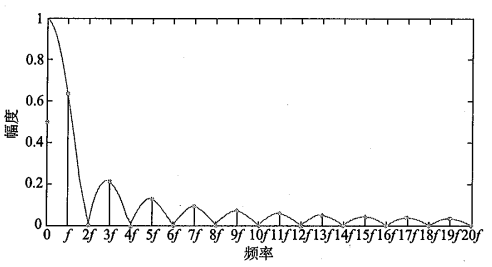

本文介绍一种 DD S(D irect D igital Syn thesizer) 与 PLL (Phase L ocked L oop ) 技术

2023-11-09 08:31:40 1

1 一、友商的nRF24L01+不要求芯片底部的金属焊盘接地,Si24R1规格书上也没要求接地,这是因为发射功率较低只有0dbm的情况,当芯片发射功率大于0dbm以后,芯片底部的金属焊盘会有很多白噪声

2023-11-06 10:27:02

自动测试设备 (ATE)对PLL(锁相环)进行测试时,我们首先要明白PLL在系统级芯片(SoC)中的重要性。

2023-11-01 15:43:10 683

683

为何不用一根导线代替锁相环? 锁相环(PLL)是一种广泛使用的电路,用于同步和追踪时钟和数据信号。它通常由一个锁相环振荡器(VCO)、一个相锁环(PLL)和一个数字控制器(DCO)组成。 PLL

2023-10-31 10:33:15 191

191 DFT PLL向量,ATE怎么用? 自动测试设备(ATE)对PLL(锁相环)进行测试时,我们首先要明白PLL在系统级芯片(SoC)中的重要性。它是SoC中关键的时钟或信号同步部件,其性能直接影响

2023-10-30 11:44:17 662

662

PLL芯片对电源的要求有哪些? PLL芯片是广泛应用于电子电路中的一种重要的芯片,它主要用于频率合成、时钟信号的处理和数据传输等方面。在应用中,PLL芯片对电源的要求非常高,以确保系统的稳定、精度

2023-10-30 10:46:54 510

510 控制多片PLL芯片时,串行控制线是否可以复用? 当需要控制多片PLL芯片时,使用复杂电路来进行控制并非理想方案,因为使用多个电路芯片会导致整个系统变得复杂且难以处理。因此,确定一个适当的解决方案

2023-10-30 10:16:42 149

149 频繁地开关锁相环芯片的电源会对锁相环有何影响? 锁相环(PLL)是一种被广泛应用在现代电子技术中的集成电路,它是一种反馈控制系统,可以将输入信号和本地参考信号同步。锁相环可用于电子时钟、数字信号处理

2023-10-30 10:16:40 267

267 Si314是一款具有自动灵敏度校准功能的14通道电容传感器,其工作电压范围为1.8~5.5V。

Si314设置休眠模式来节省功耗,此时,功耗电流为10uA@3.3V。

Si314各个感应通道可实现

2023-10-29 23:38:49

Silicon Labs无线接收器Si4355可以同时支持传输速率为2.4/9.6Kbps的数据吗?

2023-10-28 08:25:24

Silicon Labs时钟芯片Si5332如何更改时钟输出频率?

2023-10-28 07:28:03

Si1102检测频率最高可到多少Hz?

2023-10-27 07:09:26

芯片时钟不稳定会怎么样?芯片内部时钟紊乱的原因 芯片是电子设备中最重要的组成部分之一,因为它们负责控制电子设备的整个操作,并保证设备的稳定运行。在芯片中,时钟是一个非常重要的元素,因为它控制整个

2023-10-25 15:07:59 1145

1145 了解锁相环(PLL)瞬态响应 如何优化锁相环(PLL)的瞬态响应? 锁相环(PLL)是一种广泛应用于数字通信、计算机网络、无线传输等领域的重要电路。PLL主要用于时钟恢复、频率合成、时钟同步等领域

2023-10-23 10:10:20 869

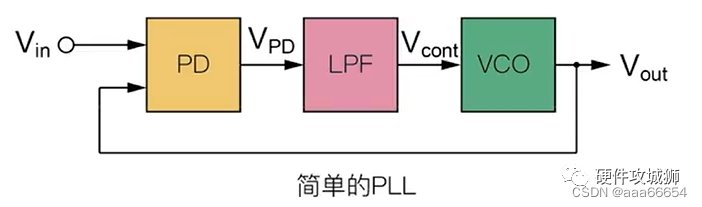

869 锁相环(PLL)基本原理 当锁相环无法锁定时该怎么处理的呢? 锁相环(Phase Locked Loop, PLL)是一种电路系统,它可以将输入信号的相位锁定到参考信号的相位。在锁相环中,反馈回路

2023-10-23 10:10:15 1352

1352 ;SI5338Q-B-GMSi5338是一款高性能、低抖动的时钟发生器,能够在设备的四个输出驱动器中的每一个上合成任何频率。这个时间IC能够更换多达四个不同频率的

2023-10-17 17:02:33

Altera的FPGA中,只有从专用时钟管脚(Dedicated clock)进去的信号,才能接片内锁相环(PLL)吗? 在Altera的FPGA中,专用时钟管脚是经过特殊处理的单独管脚,其用途

2023-10-13 17:40:00 297

297 siumlink中三相锁相环PLL的输入怎么实现? siumlink中三相锁相环PLL的输入是通过输入三相交流电压来实现的。在交流电力系统中,多数情况下使用的是三相电压,因此三相锁相环(PLL

2023-10-13 17:39:56 482

482 什么是锁相环?PLL和DLL都是锁相环区别在哪里? 锁相环(Phase Locked Loop,PLL)是一种基于反馈的控制系统,用于提供稳定的时钟信号。它可以将参考信号的相位与输出信号的相位进行

2023-10-13 17:39:53 665

665 时钟发生器由哪些部分组成?锁相环pll的特点是什么?如何用硬件配置pll 时钟发生器是指通过特定的电路设计产生适合各种电子设备使用的时钟信号的器件。时钟发生器由多个部分组成,其中最核心的是锁相

2023-10-13 17:39:50 443

443 pll锁相环的作用 pll锁相环的三种配置模式 PLL锁相环是现代电子技术中广泛应用的一种电路,它的作用是将一个特定频率的输入信号转换为固定频率的输出信号。PLL锁相环的三种配置模式分别为

2023-10-13 17:39:48 1098

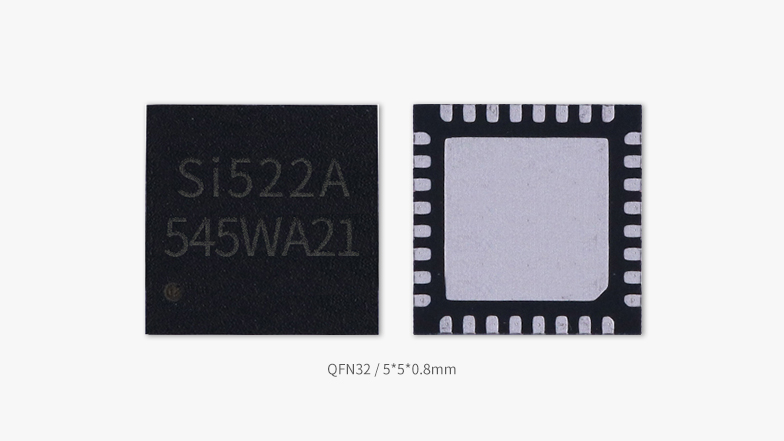

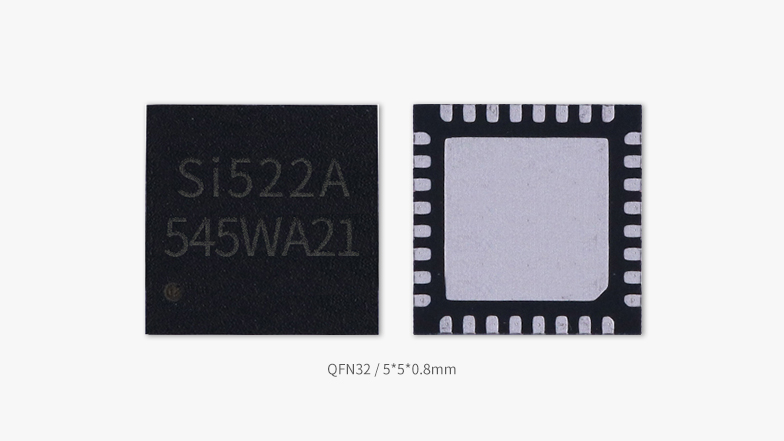

1098 Si522A是一个高度集成的,工作在13.56MHz的非接触式读写器芯片,阅读器支持ISO/IEC 14443 A/MIFARE,支持自动载波侦测功能(ACD)。 无需外围其他电路,Si

2023-10-08 17:06:44 287

287

,该模式下功耗低至4.5UA。

相比国产芯片,其他国产芯片虽然也能兼容rc522,但是其整体功耗高于si522,同时有部分国产芯片并没有加入低功耗自动寻卡功能,产品待机时间远远低于si

2023-10-08 09:28:53

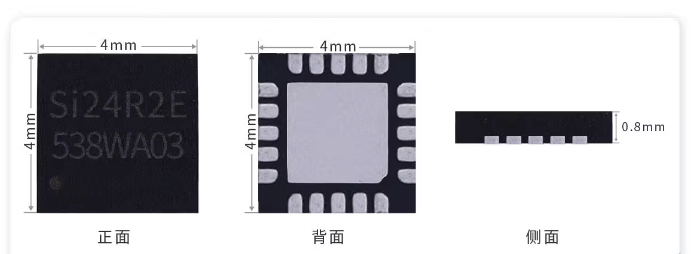

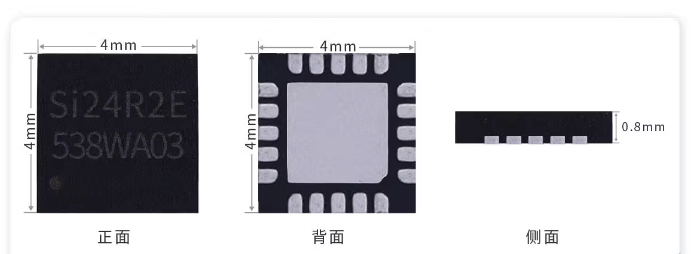

Si24R2E是国内一款针对有源RFID市场设计的低功耗、高性能的2.4GHz标签系统的SoC单芯片,集成嵌入式2.45GHz无线射频发射器模块、128次可编程NVM存储器模块以及自动发射控制器模块等。

2023-09-28 11:19:27 377

377

信号的上升时间越短,信号包含的高频成分就越多,高频分量和通道之间的相互作用就越可能导致信号畸变,从而产生SI问题。

2023-09-21 15:13:26 637

637

Si24R2F+是针对IOT应用领域推出的新款超低功耗2.4G内置NVM单发射芯片。广泛应用于2.4G有源活体动物耳标,带实时测温+计步功能。相较于Si24R2E,Si24R2F+增加了温度监控

2023-09-05 14:48:00

NRF24L01P芯片兼容通信。从而被打上了国产NRF24L01P的标签,更有甚者居然磨掉芯片原本的SI24R1的LOGO打成NRF24L01P,给很多客户产生了很多不必要的损失。大家定向的理解

2023-09-05 14:35:21

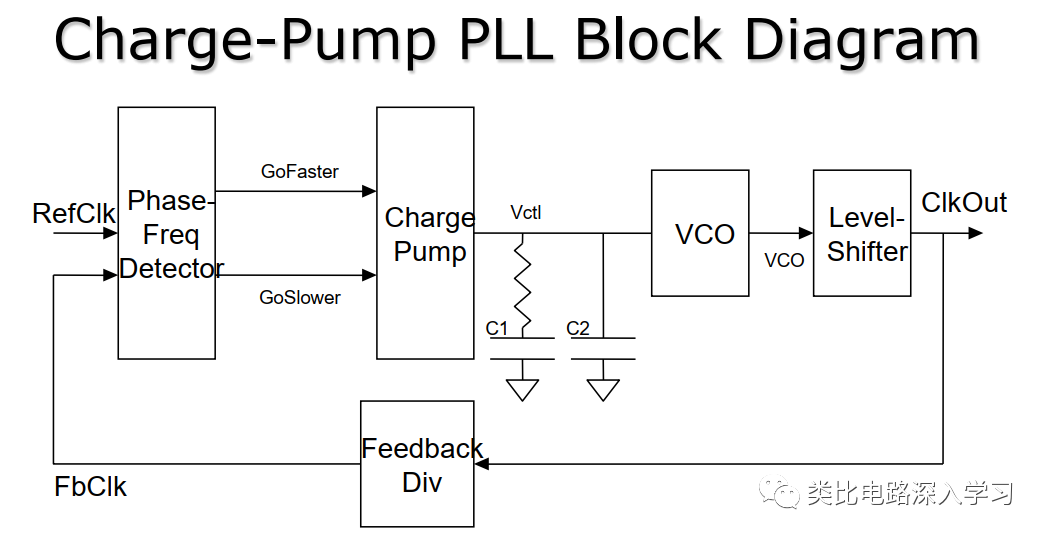

景下的时序要求。尤其对于需要高速数据传输、信号采集处理等场景的数字信号处理系统而言,FPGA PLL的应用更是至关重要。本文将介绍FPGA锁相环PLL的基本原理、设计流程、常见问题及解决方法,以及该技术在外围芯片时钟提供方面的应用实例。 一、FPGA锁相环PLL基本原理 1.时钟频率的调

2023-09-02 15:12:34 1319

1319 锁相环PLL和锁频环FLL的区别 锁相环(PLL,Phase Locked Loop)和锁频环(FLL,Frequency Locked Loop)是两种常用于信号调节和数据传输的控制回路。虽然它们

2023-09-02 15:06:39 4147

4147 PLL和DLL都是锁相环,区别在哪里? PLL和DLL都是常用的锁相环(Phase Locked Loop)结构,在电路设计中具有广泛的应用。它们的共同作用是将输入信号和参考信号的相位差控制在一定

2023-09-02 15:06:31 1522

1522 pll锁相环倍频的原理 PLL锁相环倍频是一种重要的时钟信号处理技术,广泛应用于数字系统、通信系统、计算机等领域,具有高可靠性、高精度、快速跟踪等优点。PLL锁相环倍频的原理涉及到锁相环,倍频器

2023-09-02 14:59:24 1503

1503 业界高端FPGA的卓越性能和高口碑声誉都有哪些因素了?其中很重要的一个因素就是FPGA内部丰富的时钟资源使得FPGA在处理复杂时钟结构和时序要求的设计中具有很大优势。设计师可以更好地控制和管理时钟信号,提高时序性能、减少时钟相关问题,并满足设计的高性能和稳定性要求。

2023-08-31 10:44:01 530

530

I2CON |= STA;

I2CON |= SI;

while ((I2CONSI) != SI);

I2CON= ((~STA)(~SI)); //请问这是i2c清零的动作吗??但是I2C清零不是要写

2023-08-24 06:03:19

电子发烧友网站提供《SI Logic Scientific-Linux 5.5驱动程序.zip》资料免费下载

2023-08-11 09:52:53 0

0 电子发烧友网为你提供Maxim(Maxim)SI7661DJ相关产品参数、数据手册,更有SI7661DJ的引脚图、接线图、封装手册、中文资料、英文资料,SI7661DJ真值表,SI7661DJ管脚等资料,希望可以帮助到广大的电子工程师们。

2023-07-12 18:45:05

电子发烧友网为你提供Maxim(Maxim)SI7661CSA+相关产品参数、数据手册,更有SI7661CSA+的引脚图、接线图、封装手册、中文资料、英文资料,SI7661CSA+真值表,SI7661CSA+管脚等资料,希望可以帮助到广大的电子工程师们。

2023-07-10 18:36:26

本实验活动介绍锁相环(PLL)。PLL电路有一些重要的应用,例如信号调制/解调(主要是频率和相位调制)、同步、时钟和数据恢复,以及倍频和频率合成。在这项实验中,您将建立一个简单的PLL电路,让您对PLL操作有基本的了解。

2023-07-10 10:22:24 789

789

锁相环 (PLL) 是电子系统中最通用、最灵活和最有价值的电路配置之一,因此在许多应用中都有使用。它用于时钟重定时和恢复,作为频率合成器和可调谐振荡器,仅举几个例子。因此,在包括无线电接收器和测试

2023-07-10 09:57:19 4206

4206

Si24R1

超低功耗高性能 2.4GHz GFSK 无线收发芯片

Si24R1是一颗工作在2.4GHz ISM频段,专为低功耗无线场合设计,集成嵌入式ARQ基带协议引擎的无线收发器芯片。工作频率

2023-06-27 17:48:23

使用M031来驱动SI4463

2023-06-27 06:49:16

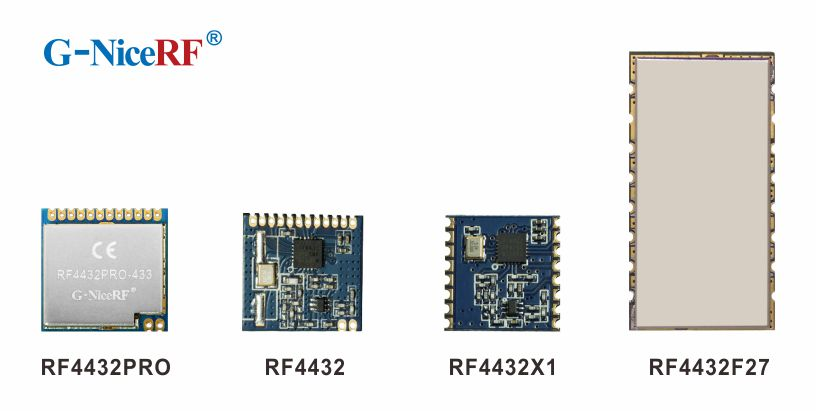

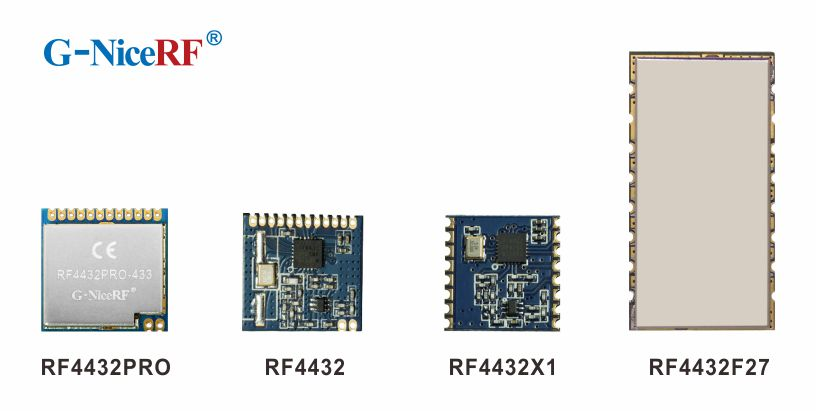

思为无线基于Silicon Lab的Si4432芯片开发出四款不同封装尺寸的射频模块:RF4432PRO、RF4432、RF4432X1和RF4432F27,以便满足不同客户的需求。

2023-06-12 16:09:16 301

301

它是RC振荡器,频率可以达到8MHZ,可作为系统时钟和PLL锁相环的输入。

2023-06-07 10:28:21 2593

2593

锁相环(PLL),作为Analog基础IP、混合信号IP、数字系统必备IP,广泛存在于各类电子产品中。

2023-06-02 15:25:14 3548

3548

1.基本参数对比 以上图片是成都亿佰特科技有限公司基于SI4463、SI4438和SI4432三款芯片设计的相关产品,上述列表是基于三款产品的测试据。 2.功能简述 SI4432 : SI

2023-05-31 15:54:43 0

0 Si4432是Silicon labs公司的射频芯片,是一款高集成度、低功耗、多频段的EZRadioPRO系列无线收发芯片。其工作电压为1.9~3.6V,可工作

在315/433/868

2023-05-31 15:27:42 1

1 GaAs的灵敏度比Si材料高1个数量级、温漂小1个数量级,是优异的线性磁传感霍尔材料。芯片特征:● 砷化镓+ Si混合可编程线性霍尔效应IC● 单电源:VDD 3

2023-05-31 10:02:47

PLL(Phase Locked Loop):为锁相回路或锁相环,用来统一整合时脉讯号,使内存能正确的存取资料。PLL用于振荡器中的反馈技术。许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步,利用锁相环路就可以实现这个目的。

2023-05-29 09:51:32 442

442

它是RC振荡器,频率可以达到8MHZ,可作为系统时钟和PLL锁相环的输入。

2023-04-28 11:32:00 1734

1734

锁相环英文名称PLL(Phase Locked Loop),中文名称相位锁栓回路,现在简单介绍一下锁相环的工作原理。

2023-04-28 09:57:31 4374

4374

R1LV0816ABG-5SI 7SI 数据表

2023-04-20 18:42:21 0

0 碳化硅(SiC)器件是一种新兴的技术,具有传统硅所缺乏的多种特性。SiC具有比Si更宽的带隙,允许更高的电压阻断,并使其适用于高功率和高电压应用。此外,SiC还具有比Si更低的热阻,这意味着它可以更有效地散热,具有更高的可靠性。

2023-04-13 11:01:16 1468

1468 适用于 S32G 的可用 IBIS 具有归类为 NC 的所有 RGMII 信号。请与 RGMII 信号共享用于系统级 SI 仿真的 S32G IC 的更新或任何等效 IBIS。此外

2023-04-12 07:00:55

和其他的电子应用中。可以使用PLL产生稳定频率的时钟,从高噪声的通信信道中恢复信号或者在设计中产生各种时钟信号。锁相环包括前置分频模块(N counter),鉴频鉴相器(PFD),电荷泵(Charge

2023-04-06 16:04:21

SI5375 - Timing, Clock Buffer / Driver / Receiver / Translator Evaluation Board

2023-03-30 11:42:23

Si8220, Si8233, Si8234, Si8235 - Interface, ISOdriver Evaluation Board

2023-03-29 22:54:44

Si8600, Si8605, Si8621, Si8655, Si8663 - Interface, Digital Isolator Evaluation Board

2023-03-29 22:54:23

Si51210, Si51211, Si51214 - Timing, Clock Generator Evaluation Board

2023-03-29 22:52:08

Si510/511, Si512/513, Si515/516, Si530/531, Si532/533, Si550/552, Si590/591 - Timing, Clock Oscillation Evaluation Board

2023-03-29 22:51:33

BOARD EVAL FOR SI5374

2023-03-29 22:50:38

SI24R2F+是针对IOT领域,电动车安全、电动车充电桩、冷链资产管理、畜牧业动物测温标签等市场推出的大功率2.4G射频芯片,内置NVM可直接配置参数生成软件。为有源RFID标签提供在中长

2023-03-29 11:26:46

南京中科微Si24R1是一款通用型低功耗、高性能的2.4GHz无线射频收发器芯片,专为低功耗无线场合设计,工作频率范围为2400MHz-2525MHz,支持2Mbps,1Mbps,250Kbps三种

2023-03-27 14:32:18

时钟发生器代替。SI393可根据不同的应用场景对接收灵敏度进行调节,在保证接收灵敏度的情况下实现更长距离的通信。同时,自动调谐特性能确保芯片与期望的载波频率完美匹配,极大简化了天线调谐器。SI393可根据不同应用场景,通过切换曼彻斯特识别模式来达到方向定位和位置识别。

2023-03-27 11:08:45

高性能、低电流收发器

2023-03-24 14:49:11

电子发烧友App

电子发烧友App

评论