MAXQ7654在信号滤波中的应用

基于高性能、16 位RISC MAXQ20 核, MAXQ7654 提供16 通道、12 位模数转换器(ADC)和双通道、12 位数模转换器(DAC)。除模拟电路外,MAXQ7654 还具有完备的数字外设,包括:CAN 控制器、SPI 接口和4 个8/16 位定时器,可用作计数器或可编程脉宽调制器。MAXQ7654 提供128kB 的程序存储空间, 能够胜任绝大多数嵌入式混合信号处理应用。

本文所描述的应用旨在展示MAXQ7654 的混合信号特性。微控制器利用一个DAC 产生带噪声的正弦波。DAC 输出被接入一个ADC 输入通道进行采样。得到的采样通过一个简易的有限激励响应(FIR)滤波器,以衰减信号中的高频分量,从而在第二个DAC 产生连续,光滑的正弦波输出。

利用丰富的模拟和数字外设,在很多有意思的应用中都可施展MAXQ7654 的能力。本文聚焦于MAXQ7

集成的模拟功能和外设使信号滤波成为可能

MAXQ7654 集成了16 通道、12 位ADC,完成一次转换仅需16 个时钟周期。时钟频率为8MHz(最大值) 时,每秒可完成500,000 次采样。测量单端模拟信号时可对多达16 路信号进行采样,测量差分信号时可对多达8 路输入信号进行采样。该ADC 也可进行温度测量——MAXQ7654 内含温度传感器,可读取芯片(管芯)温度。

MAXQ7654 包括一个硬件乘加单元,用于信号处理。它能在一个周期中进行两个16 位乘法,并且还有一个可选的累加器功能,可工作于带符号或无符号模式。这样一来简化了FIR 和IIR 滤波器的实现;每个滤波因数只需3 个机器周期的处理,其中还包括了调用滤波器的开销。

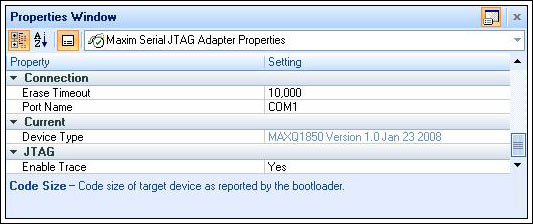

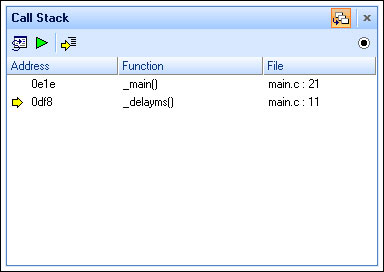

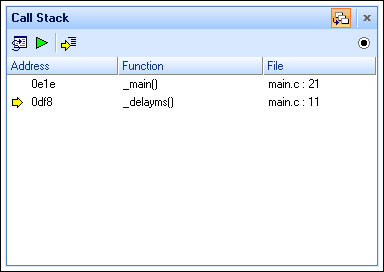

JTAG 调试引擎是MAXQ 平台公用的,当应用程序在目标硬件上运行时,利用它可完成寄存器和存储器的读、写操作。采用JTAG 后还省掉了昂贵的仿真器。主要的C 编译器提供商,如Rowley 、IAR 和Python 均支持MAXQ7654 及其调试功能。

MAXQ 平台的一个新增外设是控制器局域网(CAN) 2.0B 接口,它是常用于工业和汽车应用的通信协议。MAXQ7654 的CAN 控制器支持15 个消息中心,比特率高达1Mbps 。当受到或发出消息后以中断形式通知系统。

SPI.接口支持从机或主机模式,可进行8 位或16 位数据传输。SPI 常见于小型芯片当中,如可编程充电器、数字电位器、DAC、ADC 和存储芯片。

MAXQ7654 有4 个多功能定时器。这些定时器采用8 位或16 位计数方式,支持周期性中断、脉宽调制、捕获及比较功能的自动重装载。

滤波应用的软件架构

定时器产生中断时第一个DAC 输出带噪声的正弦波,以确保输出采样具有固定的间隔。设计用于生成正弦波的代码涉及到复杂的浮点计算,实现起来运算量很大。考虑到正弦波数据是周期性重复出现的。重新计 算那些不会随时间改变的正弦波数据会造成资源浪费。因此,在应用程序一开始就预先算出一组正弦波数据。

在正弦波数据初始化之后,定时器产生周期性中断。定时器中断程序代码中的一个伪随机数产生器用来产生噪声,噪声被直接叠加到干净的正弦波数据中。结果被传给DAC 产生输出信号。

为了保持演示程序代码的简洁,在用于产生输出正弦波的定时中断中同时对模拟输入信号进行采样。当读取输入采样后,采样信号通过简易的FIR 滤波软件处理,为使效率最大化,该滤波软件用汇编语言来实现。滤波后的采样信号随后从第2 个DAC 输出。用示波器来比较两个DAC 的输出,可以发现:一条正弦曲波较为粗糙,带有噪声,而另一条正弦波则看上去比较干净,由于FIR 滤波器的长度,带有轻微的相位延迟。

噪声正弦波的生成和采样

定时器中断程序代码如下,程序开始时已预先计算好正弦波数据,本段代码将其转换为噪声正弦波数据。

sample = static_sin_data[sinindex++]

;

sinnoise = ((sinnoise ^ 0x5C) * 31) + 0xabcd;

thisnoise = sinnoise;

if (thisnoise & 0x01)

{

thisnoise = thisnoise & 0x1ff;

}

else

{

thisnoise =

;

}

sample += thisnoise;

if (sample < 0)

sample = sample * -1;

if (sample > 4095)

sample = 8192 - sample;

DACI1 = sample; // Send value to DAC #1

if (sinindex >= SIN_WAVE_STEPS)

sinindex = 0;

sinnoise 变量用来存储伪随机噪声(可能是正的或负的)。噪声被叠加给干净的正弦波数据后,所产生的噪声正弦波数据被直接赋给DACI1 寄存器,以进行数模转换。

从ADC 读取采样数据的过程几乎同样简单。设置完ADC 的采样输入引脚后,软件可通过檠疊USY 位或者使能中断来获知转换已经结束。本实例代码使用了查询方式。

inputsample = ADC_Convert_Poll(AIN0 | START_CONV | CONTINUOUS)

;

..

.

unsigned int ADC_Convert_Poll (unsigned int Control_Reg)

{

ACNT = Control_Reg; // Set the ADC parameters

while( ACNT_bit.ADCBY == 1); // Wait till ADC is not busy

return ADCD; // Return the ADC result

}

注意,MAXQ7654 中ADC 的采样率是500ksps 。在8MHz 时钟下,只需等待16 个时钟周期便可完成一次转换。

设计一个简单的数字滤波器

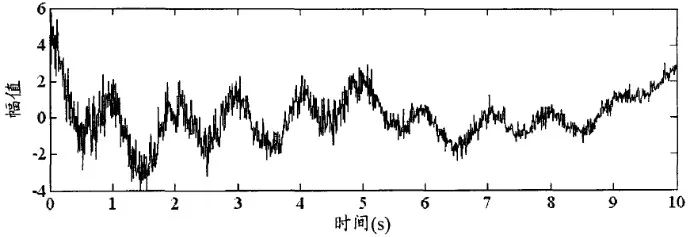

本应用所产生的波形中包含一个强低频信号和大量的高频噪声。用一个简单的低通滤波器可净化该信号。

一个通用的FIR 滤波器可用下式描述:

Y = An Xn

其中An 是滤波因数,Xn 是以前的采样输入,Y 是滤波器当前的输出。滤波因子决定滤波器的频率响应,即不同的频率成分是怎样被衰减或突出的。

可用一个Java 小程序(与本文源代码一同发布)来基于极-零图生成滤波因数(图1)。该程序可生成一组高精度的浮点滤波因数。不过,由于MAXQ7654 有16 位硬件乘加器,因此需要将浮点因数转换成16 位精度的定点因数。这一转换会给理想的滤波器变换引入误差。因此,该Java 程序也给出了建立在定点因数之上的实际变换结果,并以图形方式给出了误差。注意:尽管该程序既支持极点(突出频率分量)也支持零点(衰减频率分量),但演示代码只使用零点。无限激励响应滤波器(包含极点和零点)可以由另外的软件来实现。

在应用程序窗口底部的文本框中给出了生成的16 位定点滤波因数以及其中的小数位数。

图1. 图中给出了生成滤波器因数的Java 程序输出。该程序可生成理想转换结果、实际转换结果、误差和16 位滤波器因数。

高效数字滤波器的实现

本节讨论怎样在一个真正的数字滤波器里实现定点因数。为获得最佳性能,数字滤波器算法采用汇编语言编写。这使得应用设计人员可根据具体要求来优化滤波器程序。一两个额外的周期都可对应用的最大滤波器长度和采样率产生显著影响。

本演示程序所采取的两个关键措施使滤波器效率最大化。首先,该应用采用非滚动的滤

第2 个有助于改进滤波器效率的关键点是,将RAM 中的256 个字做为存储先前输入数据的环形缓冲器 (通用滤波器方程中的Xn 项)。如果滤波器有250 个因数,则无论如何必须储存250 个先前的输入值,这样一来RAM 中的256 个字并没有被浪费。这样设计的好处在于MAXQ 的基址-偏址指针可被用来生成硬件环形缓冲器。由于指针会自动在缓冲器边界滚动,因此滤波器软件不需要检查指针是否已达数据缓冲器的起始位置。以下是数字滤波器代码:

filtersample:

push DP[1]

push DPC

move AP, #0

sub #2048

move DPC, #10h

move BP, #W:sampletable

; preserve IAR's software stack

; probably needs this preserved

; select accumulator 0

; normalize the input sample

; DP[0] byte mode, BP word mode

; start of the sample table

move DP[0], #B:sampleindex ; point to sample current index

move AP, #1

move ACC, @DP[0]

move Offs, ACC

add #1

move @DP[0], ACC

move @BP[Offs], A[0]

move MCNT, #22h

filterloop:

;

; Unroll the filter loop for speed.

; select accumulator 1

; get current table index

; put it in the offset register

; increment the current index

; restore the table pointer

; store the current sample

; signed, accum, clear regs first

;

move MA, #0x16

move MB, @BP[Offs--]

move MA, #0x48

move MB, @BP[Offs--]

...

move MA, #0x7

move MB, @BP[Offs--]

move MA, #0x2

move MB, @BP[Offs--]

nop

move A[2], MC2 ; get MAC result HIGH

move A[1], MC1 ; get MAC result MID

move A[0], MC0 ; get MAC result LOW

代码中首先对输入采样标准化。由于MAXQ7654 有12 位ADC,因此输入值从0 到4095 。为了使用数字滤波器,输入值应被标准化为-2048 至+2047 ,也就是减去2048 (2048 = 211)。一旦输入采样的指针初始化完成,并且当前输入采样被储存,程序代码即开始执行滤波操作。

MAXQ 中的硬件乘加器单元使用起来十分方便。滤波器因数和输入采样载入乘法器寄存器,一个时钟周期之后便可获得相乘的结果。通过BP[OFF]指针可读取输入采样,滤波器因数采用硬件编码,从图1 所示的输出窗口直接获得(重现如下):

首行中的"14"表明滤波器中的数字其小数点之后有14 位,滤波完成后结果必须右移14 位。"27"表明滤波器有27 个因数。在这些控制参数之后,列出了滤波器系数,从A0 开始(0x16, 0x48, 0xad, ..) 。

滤波器算法执行完之后,累加结果即出现在乘加寄存器MC0、MC1、MC2 中。必须对该结果进行移位以补偿定点基数。

move MA, #COEFFICIENT_n

move MB, @BP[Offs--]

同时,如有必要,还注意应改变移位数。

结果

这个简易的滤波器工作得很理想。图2 给出了用示波器捕获的两个MAXQ7654 DAC 的波形。可以观察到由于FIR 滤波器的长度,在干净的输出信号中存在相移。

图2. 下面的波形是MAXQ7654 中DAC 输出的带噪声信号。它被采样、滤波并输出后显示为上面的波形。

评估板

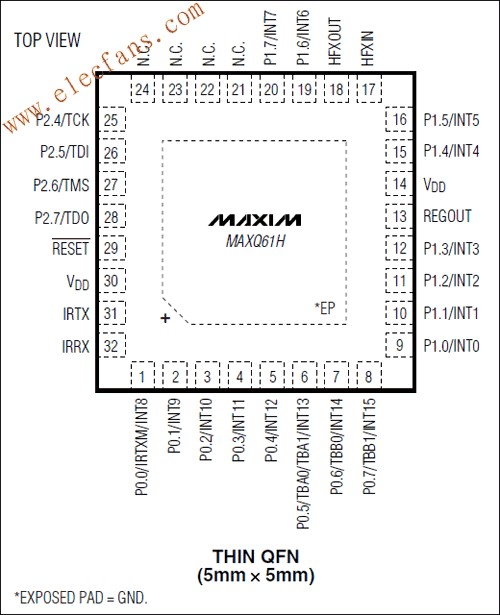

MAXQ7654 评估板的原理图随源代码一同发布。该评估板有很多用来评估MAXQ7654 微控制器的可选项。电源电压和外围器件配置可通过跳线进行选择,并且芯片的每个引脚在评估板上都有引出。MAXQ7654 评估板(参见图3)还集成了JTAG 硬件,因此加载或调试时无需外部电路板。

图3. MAXQ7654 评估板上有大量I/O、按钮和原型设计区,是评估MAXQ7654 的理想平台。

结束语

正如我们所见,MAXQ7654 是一个高性能、应用广泛的混合信号微处理器。MAXQ7654 简单的演示代码和高集成设计可使性能最大化,该器件可在信号滤波应用领域为设计者提供易于使用的解决方案。

电子发烧友App

电子发烧友App

评论