前言

在通信、雷达等数字信号处理系统的设计中,信号模拟器发挥着至关重要的作用。模拟器用来模拟实际工作过程中信号处理系统的各种输入信号,从而方便了系统调试。可以利用现有仪器模拟这些信号,也可以设计专门的模拟器。这两种方法各有特点:仪器模拟省去了模拟器的设计和调试过程,比较方便;但有时现有仪器并不能完全满足系统测试的要求,另外有些仪器的价格相当昂贵(专用的信道仿真设备一般在24000到500000美元之间[1])。因此,在信号模拟的方法上应视实际情况而定:对于ADC这样输入信号比较简单的的系统,可以利用任意波形发生器这些测试仪器进行测试;而对需要多输入或输入信号种类比较多的系统一般需要设计专用的模拟器。一般来说,能用容易得到仪器完成的信号模拟不需要设计专用模拟器。

近年来,随着电子技术的飞速发展,DSP、FPGA的性能得到很大提高的同时,其价格也在下降。因而,使DSP、FPGA得到了广泛的应用。另外,支持即插即用的USB总线技术,可以方便地完成与计算机的连接。本文利用DSP、FPGA完成了一个基于USB总线的可编程信号模拟器,该模拟器可以应用到雷达、通信等领域,尤其是无线个人网(WPAN)方面。

本文首先介绍模拟器所能完成的功能;接下来将对该模拟器的系统结构进行介绍;在第三部分,详细介绍各部分硬件的功能;在第四部分,介绍各部分软件结构;最后各该模拟系统的性能指标,以及模拟WPAN信号的方法。

1 模拟器的系统结构和功能

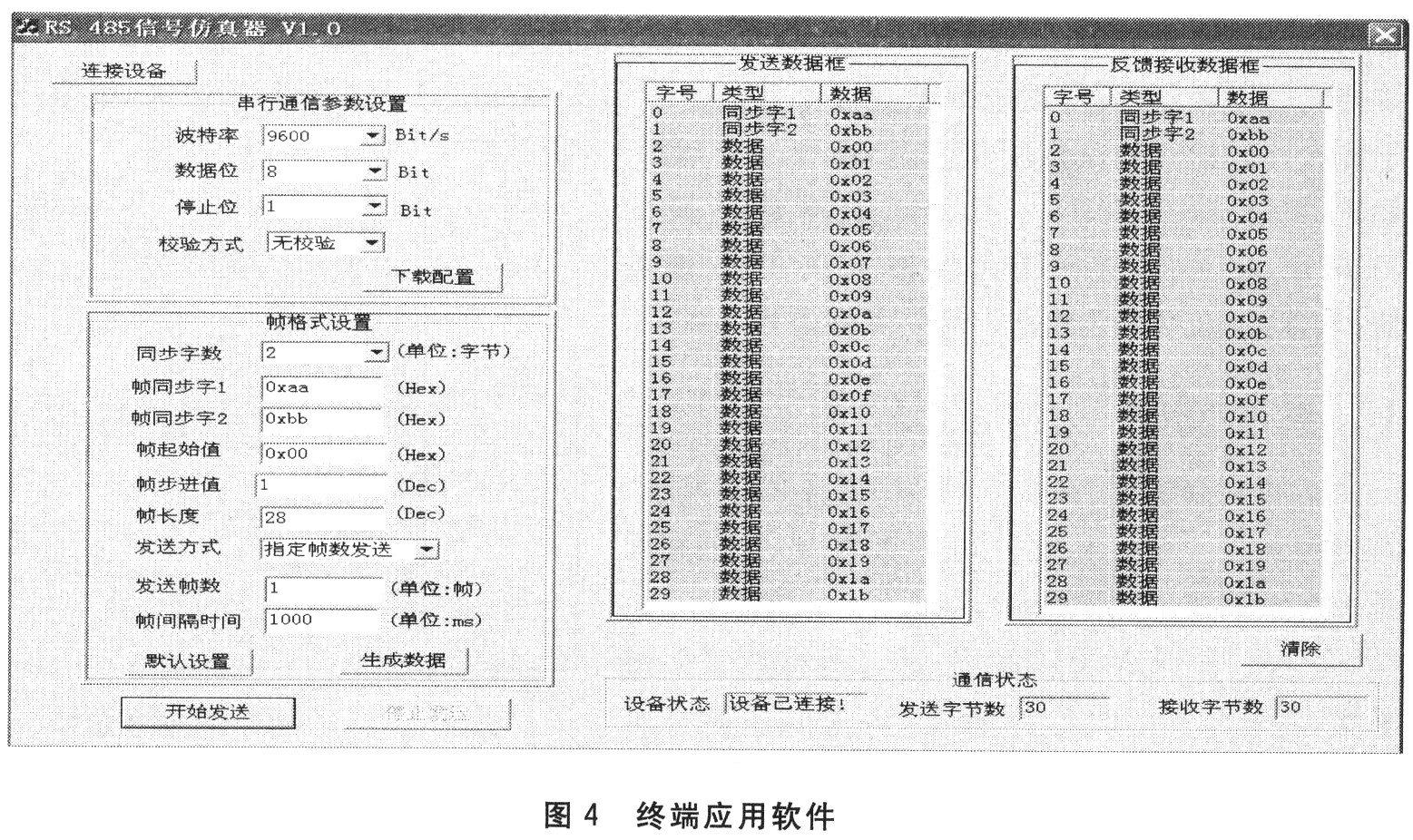

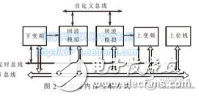

本模拟器的核心处理芯片采用TI的TMS320VC5402,该芯片是一款性价比较高的16bits定点DSP处理器。系统结构如图1所示。

该模拟器由4个外部接口:USB接口、双路模拟输出接口、数字量输出接口、用户可编程输出接口等。其中USB接口负责模拟器与计算机之间的通信,接收PC发送来的命令,向PC发送模拟器状态等;双路模拟/数字量输出接口以不同的方式将模拟结果送出系统;用户可根据自己的需要编程产生一些自定义数字量/PWM等信号经过用户可编程接口输出。该模拟器可以由PC机控制,产生I/Q两路信号进行模拟和数字量输出。预留有用户可编程接口,方便用户和其它系统进行无缝连接,如:RF模块等。

2 模拟器硬件组成

2.1 DSP处理器

该模拟器用到2个DSP处理器(TMS320VC5402),其处理能力可达100MIPS。其中DSP1负责控制USB接口芯片,与PC进行通信。并将接收到的数据和命令进行处理后,经FIFO或多缓冲同步串口(McBSP)与DSP2进行通信。DSP2进行最后的处理,产生相应的波形送给FIFO;同时向FPGA发送相应命令。FPGA根据命令控制DAC、及各输出接口,将波形数据输出。从而实时产生模拟数据和波形。

TMS320VC5402片内有16Kⅹ16bitsDARAM可以满足一般系统的处理要求,但考虑到系统扩展,在本系统中预留有外部RAM。该外部RAM可以分配为数据空间或程序空间,进行不同空间的大小扩展。

从系统结构图中可以看出,模拟器的数据流是单向的。DSP的数据总线为16bits宽,利用两片8bits异步单向FIFO(IDT72v01)进行宽度扩展,组成一个16bits的单向FIFO进行数据传输。可以将数据从DSP1传送到DSP2,由DSP2传送到各输出接口。另外,我们利用两个DSP的McBSP进行一些关键参数、及需要进行双向传输的数据进行通信传输。FIFO通信时,将其空/满标志经过译码连接到对应DSP的READY信号上。这样DSP在进行FIFO读写时,不会出现空读、和漏读现象。从而可以保证数据传输的可靠性和实时性。

2.2 USB总线接口

USB总线是一种通用的计算机串行接口总线标准,可以连接多个设备。USB总线标准目前有:1.0、1.1和2.0多个标准。其中:1.0、1.1标准最高提供12Mbps的传输速率;2.0标准最高提供480Mbps的传输速率。在该模拟器中,采用1.1标准的USB接口芯片USBN9602/3。

USBN9602/3是美国国家半导体公司生产的一款支持USB1.1标准的接口芯片。该芯片提供多种数据接口方式(8bits并口、并口复用、和MICROWIRE/PLUS),方便与控制器进行连接。相对来说,8b

its并口访问方式,访问简单读取速度比较快。该模拟器利用DSP对USBN9602/3进行控制,其数据线和地址线访问比较方便,因此采用8bits并口访问方式。USBN9602/3中断信号通知DSP进行时间处理。

2.3 可编程逻辑器件

本模拟器中两个DSP的外围器件的译码由一片CPLD完成。该CPLD根据DSP的PS、DS、IS、MSTROB、IOSTROB、WR、以及地址线译码得到外围器件(USBN9602/3、FIFO、RAM)的片选、读写等信号。

输出接口部分的FPGA负责完成对DAC、及FIFO的控制,产生他们需要的片选、读写、时钟等信号。模拟器中采用alteral公司的FPGA,在该器件中设计了多个PWM输出控制器、多个数字量输出控制寄存器。DSP2可以按照访问USBN9602/3的方式访问FPGA,对FPGA内部的寄存器进行操作。从而进行PWM和数字量输出。此外用和还可以根据自己的要求设计相应的功能,以满足不同用户的要求。alteral公司的FPGA由多种在线可编程方式,为了方便用户升级,我们采用8位并行加载方式。用户生成的下载文件经USB口传送给DSP1,由DSP1经过其总线下载导FPGA中。从而减少了利用EPROM、JTAG等其他方式加载时,对硬件进行的EPROM烧写、插拔等其他操作。对编程时FPGA和模拟器正常使用时一样,无需对硬件进行操作,做到了完全在线编程。

2.4 DAC模拟输出

本模拟器采用AD公司的8-Bit双路发射机用DAC AD9709作为数模转换芯片。该芯片的最大转换速率可达125MSPS,可以应用到通信、基站、数字合成、三维超声等领域。AD9709的数字输入端有双路并行、交织输入两种模式。我们采用能充分利用数据带宽的双路并行输入方式。AD9709模拟输出为两路差分信号,运放AD8041完成差分转单端。其功能框图如下:

3 软件结构

本模拟器的软件包括DSP和FPGA两部分。DSP1软件包括:USB控制,数据接收、处理、传输,FPGA配置,DSP2的引导等工作。DSP2软件相对较少,DSP1送来的数据进行处理,将处理后的数据送到各接口处,并控制各接口的工作状态。FPGA完成数字、模拟各接口的具体控制。图3为两个DSP的程序流程。

图3 两个DSP的程序流程

系统引导方式(Bootloader)。TMS320VC5402本身提供多种引导方式:HPI、串行EEPROM、并口、标准串口(McBSP0、McBSP1)、及IO 引导方式等。该系统的程序存放在FLASH中,该FLASH由DSP1访问。因此,DSP1采用并口引导,DSP2采用McBSP0 引导。在系统启动时,首先DSP1从并口将FLASH中的对应程序引导到DSP1的程序存储空间中,并执行相应程序。接着,DSP1从FLASH中读取DSP2的程序,将该数据经McBSP口传送给DSP2的McBSP0,对DSP2进行引导。在两片DSP引导、及运行过程中,利用BIO和XF引脚进行握手,从而对整个系统的运行进行同步和协调。

DSP1的处理流程如图3中左图所示,DSP1完成除了完成上面提到的两个DSP的引导外。还要完成USB控制、控制FPGA、处理数据、向DSP2传输数据。DSP1根据USBN9602/3的中断信号,读取USB的状态,判断,进行相应的控制(其中自然包括USB的枚举过程)。两个DSP之间由BIO和XF引脚进行握手,是并行系统的握手信号,对整个程序的协调执行进行同步。

DSP2根据DSP1发送的命令,对数据进行相应处理,并向FPGA发送控制字,调整FPGA的状态。由FPGA控制DAC、数字、PWM等接口的工作。

4 应用

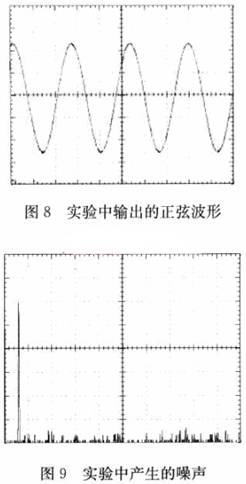

综上所述,该模拟器具有数字模拟输出接口,可以方便地和PC及进行连接控制。其性能较高,最高输出带宽可达50MHz。该模拟器经编程可以满足雷达、通信等领域应用的要求。下面以其在信道实时仿真中的应用,说明其应用过程。

信道仿真在通信系统设计中必不可少的,因此设计一个WPAN信道实时仿真系统具有一定的实用价值。WPAN有着广阔的前景,目前802.15.4标准尚未确定,商

用设备没有出现。尚处于开发研制阶段,而对于系统性能的调试、测试来说,信道实时仿真至关重要。我们知道,WPAN的数据率一般不大,在Kbps量级,也就是说信道仿真系统的数据吞吐率和数据处理量将不会太大。

该模拟器DSP1通过USB接收PC机发送来的MAC数据,DSP1种的发射机程序完成对数据的编码调制,产生相应的波形数据;该数据经过FIFO传送到DSP2,DSP2的信道模型程序模拟WSSUS信道处理数据,并向FPGA发送控制字,调整DAC的工作状态,经FIFO将波形数据送到模拟和数字输出接口。另外,用户自定义接口,模拟用户的特定的信号,可以和一些其他电路模块进行连接,以满足其他需要。例如,连接上RF模块就可以将波形数据发送到对应的无线信道等等。

5 结论

利用DSP+FPGA完成的模拟器具有良好的实用性和可编程性,适合雷达、通信等不同领域的应用。USB接口,可以利用PC机方便地进行通信和数据分析。多种输出接口模拟、数字、用户自定义接口更加扩展了应用领域。

电子发烧友App

电子发烧友App

评论