运算放大器构成加法器 可以分为同相加法器和反相加法器

2022-08-05 17:17:38 22396

22396

求助谁帮我设计一个32位浮点加法器,求助啊,谢谢啊 新搜刚学verilog,不会做{:4_106:}

2013-10-20 20:07:16

`流水线设计前言:本文从四部分对流水线设计进行分析,具体如下:第一部分什么是流水线第二部分什么时候用流水线设计第三部分使用流水线的优缺点第四部分流水线加法器举例第一 什么是流水线流水线设计就是将组合

2020-10-26 14:38:12

加法器的芯片如何选择?常用的有哪些?

2017-08-09 14:39:13

请问下大家,,进位选择加法器和进位跳跃加法器的区别是啥啊?我用Verilog实现16位他们的加法器有什么样的不同啊?还请知道的大神告诉我一下。。

2016-10-20 20:23:54

IP核加法器

2019-08-14 14:24:38

图一图二图三图四最近写了一个16位二级流水线加法器,并进行了一下仿真。发现在always块中采用阻塞赋值(=)和非阻塞赋值(

2016-09-09 09:18:13

了触发器,数据的采集需要发生在时钟上升沿),总处理数据的吞吐量增加了。流水线改造实例接下来我们用一个很简单的例子来说明如何对电路进行简单的流水线改造,假设我们现在要实现(4*a+6*b)-10,那么我们

2019-12-05 11:53:37

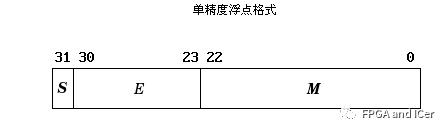

现代信号处理技术通常都需要进行大量高速浮点运算。由于浮点数系统操作比较复杂,需要专用硬件来完成相关的操作(在浮点运算中的浮点加法运算几乎占到全部运算操作的一半以上),所以,浮点加法器是现代信号

2019-07-05 06:21:42

什么是加法器?加法器的原理是什么 反相加法器等效原理图解析

2021-03-11 06:30:35

嗨,对于下面的代码片段,合成后会得到哪种类型的加法器?例如:半加法器,全加器,CLA,Ripple加法器?模块ee(输入a,e,输出reg c);总是@(*)c = a + e;endmodule

2020-03-19 09:49:31

只是想知道,如果我做一个大加法器,我可以说128位加法器。从LUT的角度来看,加法器的外观如何,因为我看到Spartan 6器件的片M具有与其他块连接的进位逻辑。如果可能,有人可以为加法器提供LUT透视框图,只需2 LUT之间的连接就可以理解这个想法。谢谢,

2019-08-08 07:13:38

如何理解fpga流水线

2015-08-15 11:43:23

前段时间发了个关于fpga的PID实现的帖子,有个人说“整个算法过程说直白点就是公式的硬件实现,用到了altera提供的IP核,整个的设计要注意的时钟的选取,流水线的应用”,本人水平有限,想请教一下其中时钟的选取和流水线的设计应该怎么去做,需要注意些什么,请大家指导一下。

2015-01-11 10:56:59

在数字化飞速发展的今天,人们对微处理器的性能要求也越来越高。作为衡量微处理器性能的主要标准,主频和乘法器运行一次乘法的周期息息相关。因此,为了进一步提高微处理器性能,开发高速高精度的乘法器势在必行

2019-09-03 08:31:04

如何进行数字相关器基本模型分析、流水线型数字相关器模型及信号处理流程 ?

2021-04-06 06:47:28

现代信号处理技术通常都需要进行大量高速浮点运算。由于浮点数系统操作比较复杂,需要专用硬件来完成相关的操作(在浮点运算中的浮点加法运算几乎占到全部运算操作的一半以上),所以,浮点加法器是现代信号

2019-08-15 08:00:45

我为64位加法器编写了一个Verilog代码,并在FPGA上进行了综合我想在Virtex FPGA板上为64位加法器进行功耗分析。任何人都可以指出可以帮助我顺利进行功率分析的材料。如果可能的话,我甚至想获得视频教程的链接。任何形式的帮助都可以谢谢

2020-07-18 13:41:42

需要设计一个模加法器,书上没有详细的讲解,只说是用端回进位加法器实现模2^n-1,可是具体应该怎么设计啊~~~~

2016-07-07 14:48:36

fpga:Spartan-6 xc6slx150-3fgg484我在资源密集型处理系统中使用了几百个8位加法器,因此资源使用很重要。用于加法器减法器的核心生成器为具有2个8位输入和8位输出,0延迟

2019-04-03 15:55:35

基于FPGA的64位流水线加法器的设计基本要求: FPGA 可自行选择可实现64位无符号数的加法运算8级流水线深度

2014-12-18 11:00:42

流水线技术是提高系统吞吐率的一项强大的实现技术,并且不需要大量重复设置硬件。20世界60年代早期的一些高端机器中第一次采用了流水线技术。第一个采用指令流水线的机器是IBM7030(又称

2023-03-01 17:52:21

在ARM中,关于 LDR流水线,分支流水线,中断流水线,其和 PC 之间的关系一直没整明白,求大神详解!!!

2019-04-30 07:45:25

请问一下高速流水线浮点加法器的FPGA怎么实现?

2021-05-07 06:44:26

我正在设计一个流水线递归加法器树。该设计适用于2个输入数的功率,但在达到奇数个输入时似乎失败。结构没问题,但是比特数关闭,这导致运行模拟时的不确定状态。请看一下。加布里埃尔adder_r1.sv 4

2019-04-25 13:53:44

FPGA重要设计思想及工程应用之流水线设

流水线设计是高速电路设计中的一 个常用设计手段。如果某个设计的处理流程分为若干步骤,而且整个数据处理 流程分

2010-02-09 11:02:20 52

52 摘要:加法运算在计算机中是最基本的,也是最重要的运算。传统的快速加法器是使用超前进位加法器,但其存在着电路不规整,需要长线驱动等缺点。文章提出了采用二叉树法设

2010-05-19 09:57:06 62

62 流水线技术在高速数字电路设计中的应用

2010-07-17 16:37:21 6

6 根据一款32位嵌入式CPU的400MHz主频的要求,结合该CPU五级流水线结构,并借鉴各种算法成熟的加法器,提出了一种电路设计简单、速度快、功耗低、版图面积小的32位改进定点加法器

2010-07-19 16:10:03 17

17 介绍了补码阵列乘法器的Pezaris 算法。为提高运算速度,利用流水线技术进行改进,设计出流水线结构阵列乘法器,使用VHDL语言建模,在Quartus II集成开发环境下进行仿真和功能验证

2010-08-02 16:38:00 0

0

图二所示为4位并行的BCD加法器电路。其中上面加法器的输入来自低一级的BCD数字。下

2009-03-28 16:35:54 11908

11908

第二十讲 加法器和数值比较器

6.6.1 加法器一、半加器1.含义 输入信号:加数Ai,被加数Bi 输出信号:本位和Si,向高位

2009-03-30 16:24:54 5502

5502

加法器:Summing Amplifier

The summing amplifier, a special case of the inverting amplifier, is shown in Figure 4. The circuit gives an

2009-05-16 12:38:34 2626

2626

什么是流水线技术

流水线技术

2010-02-04 10:21:39 3702

3702 加法器,加法器是什么意思

加法器 : 加法器是为了实现加法的。 即是产生数的和的装置。加数和被加数为输入,和数与

2010-03-08 16:48:58 5106

5106 加法器原理(16位先行进位)

这个加法器写的是一波三折啊,昨天晚上花了两三个小时好不容易写完编译通过了,之后modelsim莫

2010-03-08 16:52:27 10942

10942 十进制加法器,十进制加法器工作原理是什么?

十进制加法器可由BCD码(二-十进制码)来设计,它可以在二进制加法器的基础上加上适当的“校正”逻辑来实现,该校正逻

2010-04-13 10:58:41 12741

12741 流水线中的相关培训教程[4]

下面讨论如何利用编译器技术来减少这种必须的暂停,然后论述如何在流水线中实现数据相关检测和定向。

2010-04-13 16:09:15 4272

4272 为了提高快速傅里叶变换( FFT)处理数据的实时性,本文利用现场可编程阵列( FPGA)逻辑资源丰富、运算速度快的特点以及FFT算法的分级特性,实现了高速、高阶FFT的流水线工作方式设计。通

2011-10-01 01:52:51 55

55 为了提高快速傅里叶变换( FFT)处理数据的实时性,本文利用现场可编程阵列( FPGA)逻辑资源丰富、运算速度快的特点以及FFT算法的分级特性,实现了高速、高阶FFT的流水线工作方式设计。通

2011-10-28 17:11:26 32

32 设计了一种支持IEEE754浮点标准的32位高速流水线结构浮点乘法器。该乘法器采用新型的基4布思算法,改进的4:2压缩结构和部分积求和电路,完成Carry Save形式的部分积压缩,再由Carry Lo

2012-02-29 11:20:45 3269

3269 浮点运算器的核心运算部件是浮点加法器,它是实现浮点指令各种运算的基础,其设计优化对于提高浮点运算的速度和精度相当关键。文章从浮点加法器算法和电路实现的角度给出设计

2012-07-06 15:05:42 47

47 8位加法器和减法器设计实习报告

2013-09-04 14:53:33 133

133 为了缩短加法电路运行时间,提高FPGA运行效率,利用选择进位算法和差额分组算法用硬件电路实现32位加法器,差额分组中的加法单元是利用一种改进的超前进位算法实现,选择进位算

2013-09-18 14:32:05 33

33 Xilinx FPGA工程例子源码:Xilinx 公司的加法器核

2016-06-07 15:07:45 12

12 同相加法器输入阻抗高,输出阻抗低 反相加法器输入阻抗低,输出阻抗高.加法器是一种数位电路,其可进行数字的加法计算。当选用同相加法器时,如A输入信号时,因为是同相加法器,输入阻抗高,这样信号不太容易流入加法器,反而更容易流入B端。

2016-09-13 17:23:33 55184

55184

加法器VHDL程序,感兴趣的小伙伴们可以瞧一瞧。

2016-11-11 15:51:00 5

5 基于Skewtolerant Domino的新型高速加法器

2017-01-22 20:29:21 8

8 流水线状态机20进制,101序列检测,8位加法器流水线的程序

2017-05-24 14:40:47 0

0 加法器是为了实现加法的。即是产生数的和的装置。加数和被加数为输入,和数与进位为输出的装置为半加器。若加数、被加数与低位的进位数为输入,而和数与进位为输出则为全加器。

2017-06-06 08:45:01 22730

22730

最近在做基于MIPS指令集的单周期CPU设计,其中的ALU模块需要用到加法器,但我们知道普通的加法器是串行执行的,也就是高位的运算要依赖低位的进位,所以当输入数据的位数较多时,会造成很大的延迟

2018-07-09 10:42:00 19434

19434

加法器是产生数的和的装置。加数和被加数为输入,和数与进位为输出的装置为半加器。

2017-08-16 09:39:34 21933

21933

加法器是产生数的和的装置。加数和被加数为输入,和数与进位为输出的装置为半加器。减法电路是基本集成运放电路的一种,减法电路可以由反相加法电路构成,也可以由差分电路构成。基本集成运放电路有加、减、积分和微分等四种运算。一般是由集成运放外加反馈网络所构成的运算电路来实现。

2017-08-16 11:09:48 159697

159697

8位全加器可由2个4位的全加器串联组成,因此,先由一个半加器构成一个全加器,再由4个1位全加器构成一个4位全加器并封装成元器件。加法器间的进位可以串行方式实现,即将低位加法器的进位输出cout与相临的高位加法器的最低进位输入信号cin相接最高位的输出即为两数之和。

2017-11-24 10:01:45 28522

28522

摘要: 数字相关器在数字扩频通信系统中应用广泛,受数字信号处理器件速度限制,无法应用于高速宽带通信系统,在此提出了一种基于流水线加法器的数字相关处理算法。该算法最大限度地减少了加法器进位操作

2018-01-18 03:49:01 324

324 只产生9个部分积,有效降低了部分积压缩阵列的规模与延时.通过对5级流水线关键路径中压缩阵列和64位超前进位(CLA)加法器的优化设计,减少了乘法器的延时和面积.经现场可编程逻辑器件仿真验证表明,与采用Radix-8 Booth算法的乘法器相比,该乘法器速度提高了11%,硬件资

2018-03-15 13:34:00 6

6 一、什么是加法器加法器是为了实现加法的。即是产生数的和的装置。加数和被加数为输入,和数与进位为输出的装置为半

2018-03-16 15:57:19 20714

20714

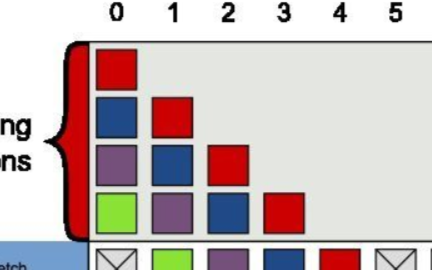

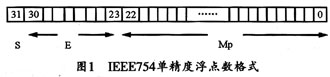

颜色表示了不同阶段的可配置性或可编程性:绿色表示该流水线阶段是完全可编程控制的,黄色表示该流水线阶段可以配置但不是可编程的,蓝色表示该流水线阶段是由GPU固定实现的,开发者没有任何控制权。实线表示该shader必须由开发者编程实现,虚线表示该Shader是可选的.

2018-05-04 09:16:00 3613

3613

第一部分什么是流水线 第二部分什么时候用流水线设计 第三部分使用流水线的优缺点 第四部分流水线加法器举例 一. 什么是流水线 流水线设计就是将组合逻辑系统地分割,并在各个部分(分级)之间插入寄存器

2018-09-25 17:12:02 4370

4370 如果有数字电路常识的人都知道,利用一块组合逻辑电路去做8位的加法,其速度肯定比做2位的加法慢。因此这里可以采用4级流水线设计,每一级只做两位的加法操作,当流水线一启动后,除第一个加法运算之外,后面每经过一个2位加法器的延时,就会得到一个结果。

2019-02-04 17:20:00 7563

7563 流水线的工作方式就象工业生产上的装配流水线。在CPU中由5—6个不同功能的电路单元组成一条指令处理流水线,然后将一条X86指令分成5—6步后再由这些电路单元分别执行,这样就能实现在一个CPU时钟周期完成一条指令,因此提高CPU的运算速度。

2019-11-29 07:06:00 2251

2251 流水线的平面设计应当保证零件的运输路线最短,生产工人操作方便,辅助服务部门工作便利,最有效地利用生产面积,并考虑流水线安装之间的相互衔接。为满足这些要求,在流水线平面布置时应考虑流水线的形式、流水线安装工作地的排列方法等问题。

2019-11-28 07:07:00 2039

2039 流水线又称为装配线,一种工业上的生产方式,指每一个生产单位只专注处理某一个片段的工作。以提高工作效率及产量;按照流水线的输送方式大体可以分为:皮带流水装配线、板链线、倍速链、插件线、网带线、悬挂线及滚筒流水线这七类流水线。

2019-11-28 07:04:00 3232

3232 二进制加法器是半加器和全加法器形式的运算电路,用于将两个二进制数字加在一起.

2019-06-22 10:56:38 24316

24316

加法器是产生数的和的装置。加数和被加数为输入,和数与进位为输出的装置为半加器。若加数、被加数与低位的进位数为输入,而和数与进位为输出则为全加器。

2019-06-19 14:19:17 7423

7423 加法器是产生数的和的装置。加数和被加数为输入,和数与进位为输出的装置为半加器。若加数、被加数与低位的进位数为输入,而和数与进位为输出则为全加器。常用作计算机算术逻辑部件,执行逻辑操作、移位与指令调用

2019-06-19 14:20:39 24786

24786

本文档的主要内容详细介绍的是使用流水线结构设计加法器的方案和工程文件免费下载

2020-09-07 18:21:28 3

3 加法器是产生数的和的装置。加数和被加数为输入,和数与进位为输出的装置为半加器。若加数、被加数与低位的进位数为输入,而和数与进位为输出则为全加器。常用作计算机算术逻辑部件,执行逻辑操作、移位与指令调用

2021-02-18 14:40:31 30941

30941

verilog实现加法器,从底层的门级电路级到行为级,本文对其做出了相应的阐述。

2021-02-18 14:53:52 5585

5585

介绍各种加法器的Verilog代码和testbench。

2021-05-31 09:23:42 19

19 按照流水线的输送方式大体可以分为:皮带流水装配线、板链线、倍速链、插件线、网带线、悬挂线及滚筒流水线这七类流水线。

2021-07-05 11:12:18 6087

6087

流水线一、定义流水线是指在程序执行时多条指令重叠进行操作的一种准并行处理实现技术。各种部件同时处理是针对不同指令而言的,他们可同时为多条指令的不同部分进行工作。• 把一个重复的过程分解为若干个子过程

2021-10-20 20:51:14 6

6 。二、半加法器的实现在解释这个半加法器之前,要明白计算机其实就是靠简单电路集成起来的复杂电路而已,而构成这些复杂电路最简单的逻辑电路就是“与”、“或”、“非”。而在他们的基础之上进行组合,...

2021-11-11 12:06:03 20

20 本文解释了流水线及其对 FPGA 的影响,即延迟、吞吐量、工作频率的变化和资源利用率。

2022-05-07 16:51:10 4734

4734

电子发烧友网站提供《4位加法器开源分享.zip》资料免费下载

2022-07-08 09:33:21 3

3 行波进位加法器和超前进位加法器都是加法器,都是在逻辑电路中用作两个数相加的电路。我们再来回顾一下行波进位加法器。

2022-08-05 16:45:00 886

886

jenkins 有 2 种流水线分为声明式流水线与脚本化流水线,脚本化流水线是 jenkins 旧版本使用的流水线脚本,新版本 Jenkins 推荐使用声明式流水线。文档只介绍声明流水线。

2023-05-17 16:57:31 613

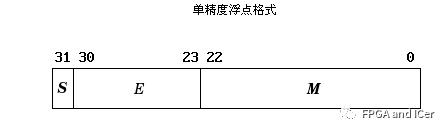

613 设计一个32bit浮点的加法器,out = A + B,假设AB均为无符号位,或者换个说法都为正数。

2023-06-02 16:13:19 590

590

有关加法器的知识,加法器是用来做什么的,故名思义,加法器是为了实现加法的,它是一种产生数的和的装置,那么加法器的工作原理是什么,为什么要采用加法器,下面具体来看下。

2023-06-09 18:04:17 3481

3481 加法器可以是半加法器或全加法器。不同之处在于半加法器仅用于将两个 1 位二进制数相加,因此其总和只能从 0 到 2。为了提高这种性能,开发了FullAdder。它能够添加三个 1 位二进制数,实现从 0 到 3 的总和范围,可以用两个输出位 (“11”) 表示。

2023-06-29 14:27:35 5478

5478

半加法器是一种执行二进制数相加的数字电路。它是最简单的数字加法器,您只需使用两个逻辑门即可构建一个;一个异或门和一个 AND 门。

2023-06-29 14:35:25 4648

4648

电子发烧友网站提供《4位加法器的构建.zip》资料免费下载

2023-07-04 11:20:07 0

0 镜像加法器是一个经过改进的加法器电路,首先,它取消了进位反相门;

2023-07-07 14:20:50 1189

1189

,浮点加法器是现代信号处理系统中最重要的部件之一。FPGA是当前数字电路研究开发的一种重要实现形式,它与全定制ASIC电路相比,具有开发周期短、成本低等优点。 但多数FPGA不支持浮点运算,这使FPGA在数值计算、数据分析和信号处理等方

2023-09-22 10:40:03 394

394

前段时间和几个人闲谈,看看在FPGA里面实现一个Mem加法器怎么玩儿

2023-10-17 10:22:25 279

279

![]()

电子发烧友App

电子发烧友App

评论