本文主要介绍JTAG总线的引脚定义、接口标准、边界扫描和TAP控制器。 JTAG(Joint Test Action Group;联合测试行动小组)是一种国际标准测试协议(IEEE 1149.1兼容

2020-11-27 14:13:28 13488

13488

提到边界扫描,就不得不提JTAG,因为边界扫描是JTAG接口的功能之一。

2023-09-22 14:12:17 1497

1497

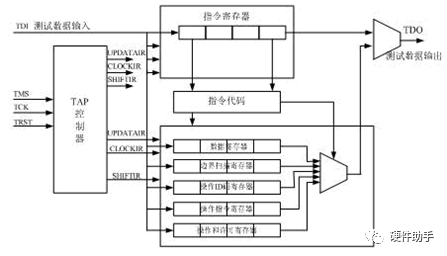

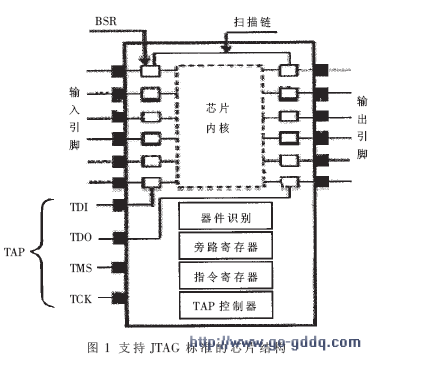

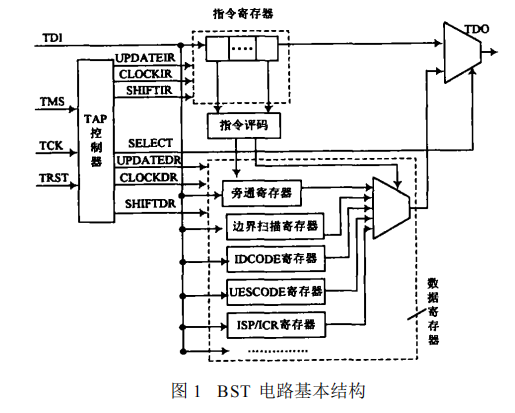

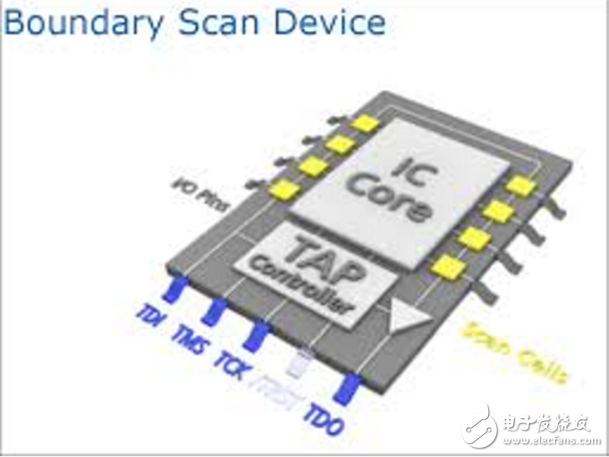

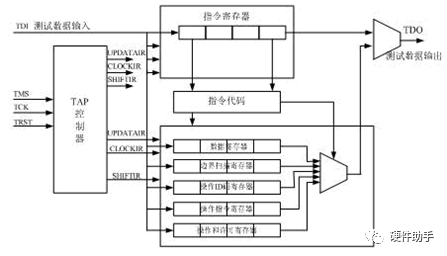

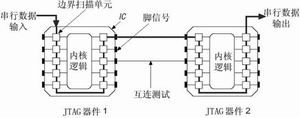

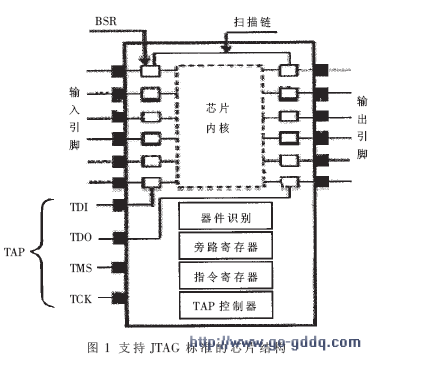

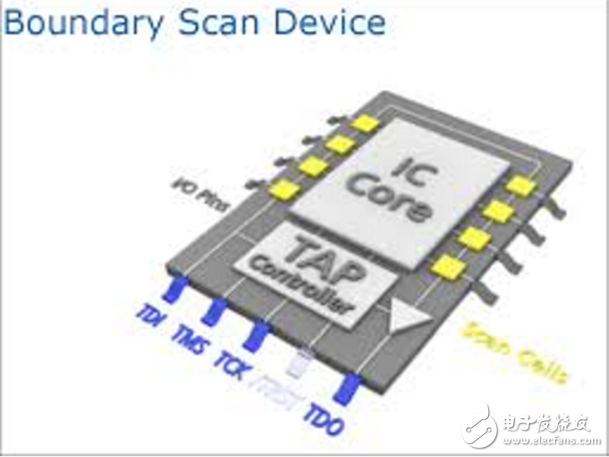

、JTAGJTAG的基本原理是在器件内部定义一个TAP(测试访问口),通过专用的JTAG测试工具对内部节点进行测试。除了TAP之外,混合IC还包含移位寄存器和状态机,该状态机被称为TAP控制器,以执行边界扫描功能。JTAG测试允许多个器件通过JTAG接口串联在一起,形成一个JTAG链,能实现对各个器件分别测试

2022-02-17 08:00:13

JTAG概述 JTAG组成结构 JTAG扫描链工作原理 结语 参考文献 JTAG扫描链工作原理 BSR可以相互连接起来,在芯片周围形成一个边界扫描链。(Boundary-Scan Chain

2018-07-02 04:26:39

我用AVR单片机写了一个边界扫描的程序,用于检测带JTAG的器件。在调试程序的过程中遇到了一些问题,不知有谁对边界扫描有过研究,可以帮我解决这些问题。硬件:MEGA16,使用内部8M时钟,作控制器

2013-06-01 16:47:08

有做过边界扫描控制器的大神吗?想问一下sn74act8990这个芯片有没有人用过啊,怎么使用,谢谢啦

2017-07-10 17:50:00

请教:我在使用c6678开发板,想使用边界扫描测试的功能,不知道除了开发板硬件之外,是不是还需要其他硬件和软件的配合?

2018-06-19 07:36:16

边界扫描测试技术 不属于 coresight架构,边界扫描测试技术 被 coresight 架构 使用.综述联合测试行动组(Joint Test Action Group,简称 JTAG)提出了边界

2022-02-17 07:33:41

边界扫描测试技术简介及原理 1. 简介 JTAG(Joint Test Action Group,联合测试行动小组)是1985年制定的检测PCB和IC芯片的一个

2009-10-15 09:32:16

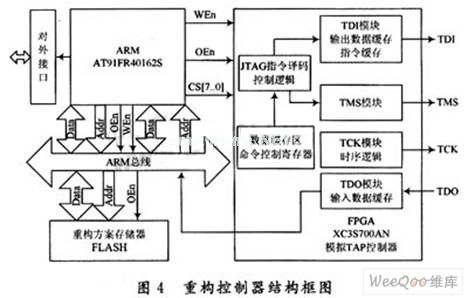

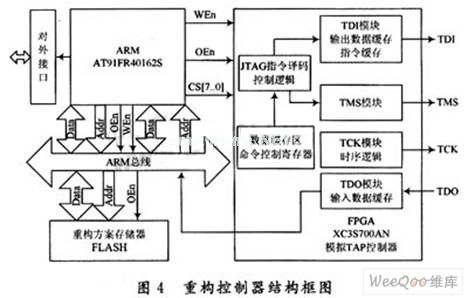

:TMS(模式选择)、TCK(时钟)、TDI(数据输入)、TDO(数据输出线)。本文利用JTAG标准协议设计一种针对同类FPGA进行动态重构配置的重构控制器。

2019-10-17 07:50:32

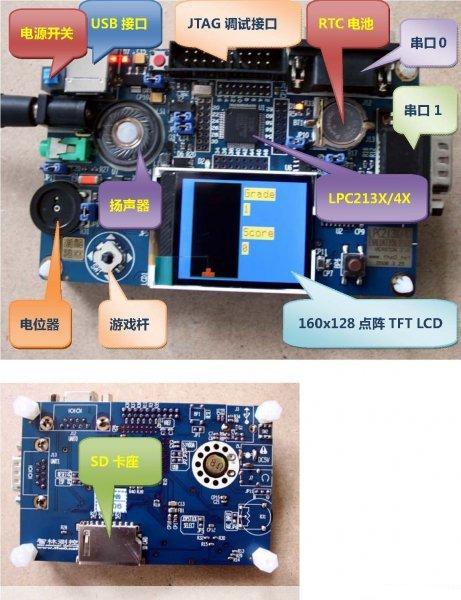

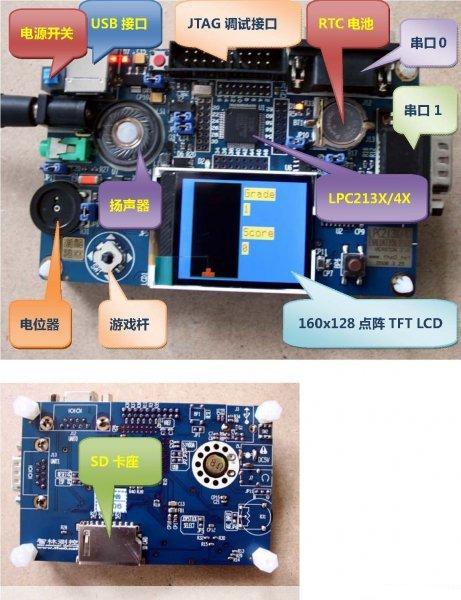

基于JTAG仿真器的调试是目前ARM开发中采用最多的一种方式。大多数ARM设计采用了片上JTAG接口,并将其作为测试、调试方法的重要组成。JTAG仿真器通过ARM芯片的JTAG边界扫描口与ARM

2019-10-18 06:33:42

本章介绍了 Cyclone® IV 器件所支持的边界扫描测试 (BST) 功能。这些 BST 功能与Cyclone III 器件中的相类似,除非另有说明。Cyclone IV 器件 (Cyclone

2017-11-14 10:50:26

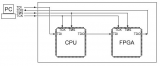

请教大家一个问题,板子上有两个FPGA,想用一个PROM配置,将PROM和两个FPGA用边界扫描下载方式连起来可以吗? 就是下图这种模式,可不可以再多串一个FPGA呢?

2014-03-24 15:53:09

而设定FPGA的逻辑功能。根据FPGA的容量不同、配置方式不同,全部重构时间为几ms到几秒不等。 对于常规FPGA来说,重载方式多种多样。在系统调试阶段,一般是通过JTAG电缆从主机下载配置数据

2011-05-27 10:22:59

我正在使用 IMX8m Plus 构建定制板,我想使用边界扫描来测试板的连接。为此,我正在 (8MPLUSLPD4-EVK) 上进行试验,以检查 JTAG 连接以及进入边界扫描模式需要执行的操作。我

2023-03-29 06:05:21

,易于对创作者群体进行扩展。项目在PYNQ框架下开发了可重构运动控制器,所提出的体系结构依赖于使用S曲线算法来控制轨道上的运动,而另一个则是为了验证概念。 1.什么是S型运动轨迹规划 市场上发现的许多

2021-01-07 17:17:14

提供了一种便捷的方式用于观测和控制所需调试的芯片。另外,芯片输入/输出引脚上的边界扫描(移位)寄存器单元可以相互连接起来,在芯片的周围形成一个边界扫描链(Boundary-Scan Chain)。边界

2012-03-01 09:26:05

控制边界扫描测试的各种工作状态。 1.1测试时钟输入端TCK TCK信号允许集成电路IC的边界扫描部分与系统内的时钟同步并独立工作。 1.2测试方式选择输入端TMS 测试方式选择TMS引脚为

2018-09-10 16:50:00

和 RK3399 相似应该是个 M 核,很可能用作管理单元?串行 SW 调试口说是主 APU 的,没问题。完整的 JTAG 是否有物理引脚边界扫描能力?SW 天生为 1 对 1,无法在板级串联,肯定

2023-01-06 15:15:24

DR。

5、边界扫描:

TAP控制器进入边界扫描模式时,DR链可以遍历每个IO块或者读或拦截每个引脚。在FPGA上使用JTAG,你可以知晓每个引脚的状态当FPGA在运行的时候。可以

2024-01-19 21:19:29

,FPGA器件处于主动地位,配置器件处于从属地位。配置数据通过DATA0引脚送入 FPGA。配置数据被同步在DCLK输入上,1个时钟周期传送1位数据。 PS配置方式则由外部计算机或其它控制器控制配置

2018-03-05 16:30:35

允许加载位文件,则相同的测试失败。什么是配置V5可以杀死我的边界扫描测试,其他所有东西保持相同?我认为一旦芯片处于JTAG“测试模式”,边界扫描寄存器就可以完全控制每个接口引脚。注意:我知道芯片成功处于测试模式,因为我可以观察输出引脚与边界扫描的输出数据之间的切换。

2020-06-03 14:06:20

信号和数据信号通过通信接口分别保存在边界扫描适配器内部的 寄存器中,然后适配器中的其它模块如TAP 控制器、信号采集模块和信号发生模块将依据 指令寄存器中的指令字进行相应的工作,包括发送JTAG 总线

2018-09-10 16:28:11

PID控制器的基本原理是什么?PI-PD控制器的结构是怎样构成的?基于PI-PD控制器的四旋翼姿态控制方式有什么优点?

2021-07-22 08:41:15

可重构技术是指利用可重用的软硬件资源,根据不同的应用需求,灵活地改变自身体系结构的设计方法。常规SRAM工艺的FPGA都可以实现重构,那我们具体该怎么做呢?

2019-08-09 07:35:02

边界扫描是什么原理?如何利用FPGA作为载体来实现边界扫描故障诊断仪的SOPC系统?

2021-04-12 06:07:03

与之相连的边界扫描寄存器“捕 获”该引脚上的输出信号。在正常的运行状态下,边界扫描寄存器对芯片来说是透明的,所以正常的运行不会受到任何影响。这样,边界扫描寄存器提供了一种便捷 的方式用于观测和控制所需

2022-05-24 15:53:14

我想使用边界扫描测试在 STM32F407VG 发现板上测试差分信号。我知道这个 soc 支持边界扫描测试,但是否也可以通过相同的方式测试/测量差分信号?

2023-01-31 08:28:49

嵌入式边界扫描是什么?嵌入式边界扫描系统主要有哪些结构?怎样去实现嵌入式边界扫描系统?

2021-04-15 07:01:49

怎样才能使JTAG边界扫描与功能测试相结合

2021-05-06 07:56:42

JTAG是什么?JTAG芯片的边界扫描寄存器通过使用TAP状态机的指令实行对FIash的操作

2021-04-26 06:35:31

嗨,所有,我试图执行JTAG指令与PIC32 MX100F016B微控制器。作为实验,我操作了不同频率的指令。我注意到,切换边界扫描链的指令(采样/预加载、ExtTest、高Z)只能从某个频率正常

2018-10-25 16:46:50

我想通过JTAG在我的设计中内部访问寄存器。1)如何挂钩fpga JTAG链?2)是否有JTAG控制器IP?我看了,没看到一个。谢谢,弗雷德

2020-05-29 06:13:24

各位大侠,有谁了解边界扫描工具的嚒?这个前景怎么样?

2012-06-11 21:34:54

大家好,我正在使用 STM32F407G-DISC1 开发板。我有 ST-Link V2 外部调试器(我附上了哪个图像),因为我不想使用板载调试器。我想进行边界扫描测试。你能建议我有没有免费的工具可用于 STM32F4 进行边界扫描测试。

2023-01-31 08:33:02

本文介绍支持JTAG标准的IC芯片结构,并以Xilinx公司的两块xc9572_ pc84芯片为例,探讨并利用边界扫描技术控制IC芯片处于某种特定功能模式的方法,并且针对IC芯片某种特定的功能模式设计该芯片的JTAG控制器。

2021-04-30 06:05:17

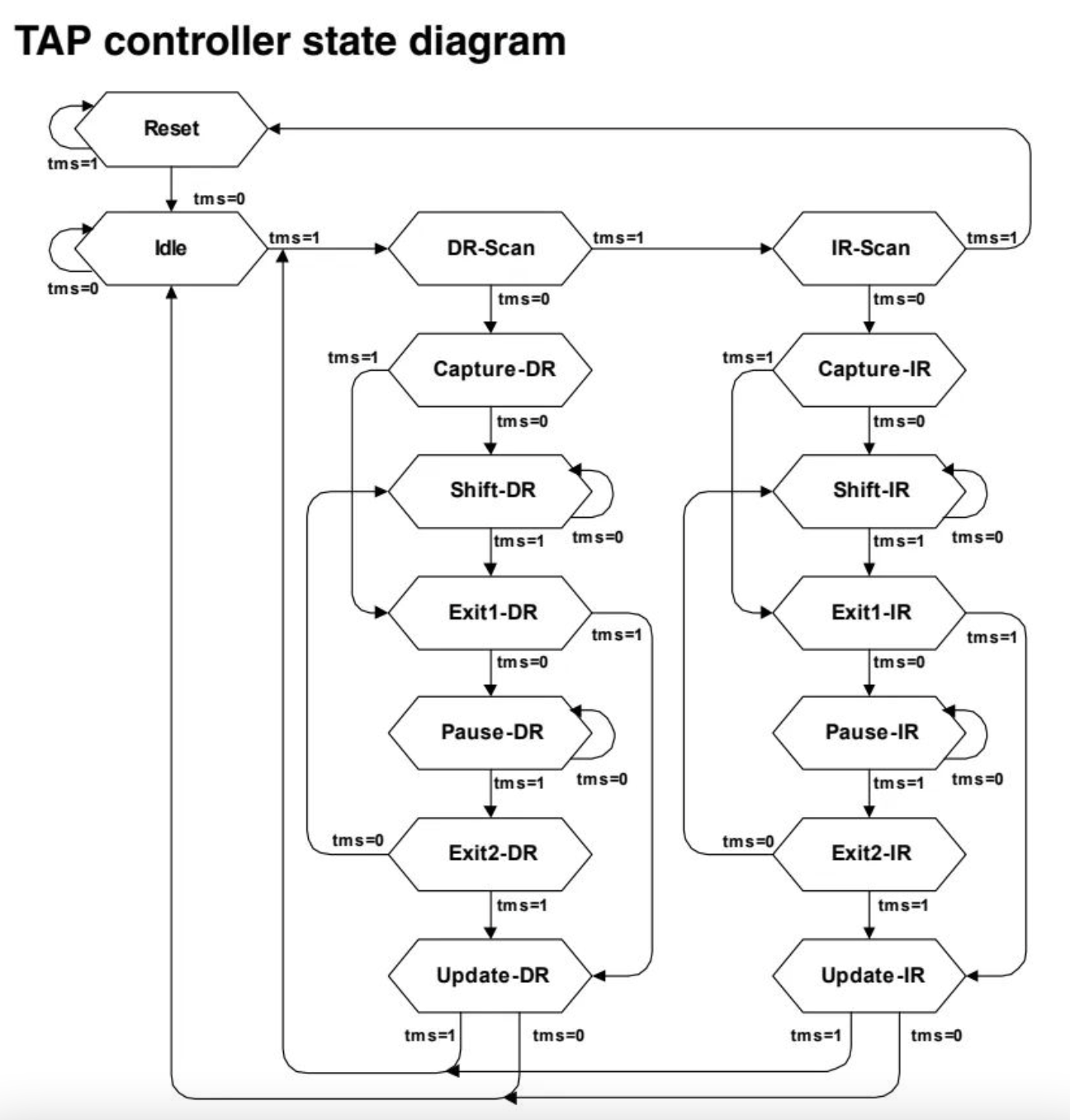

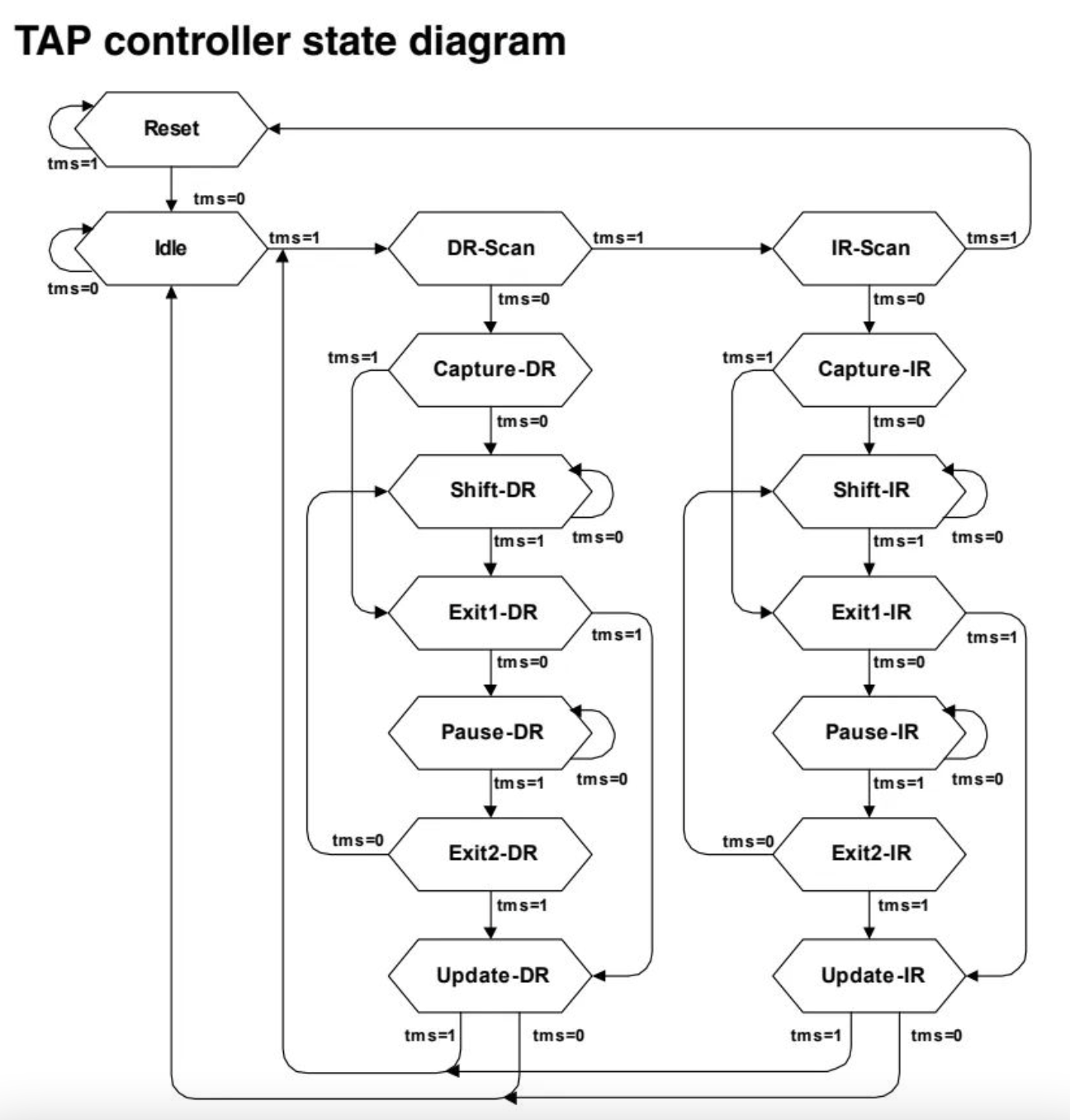

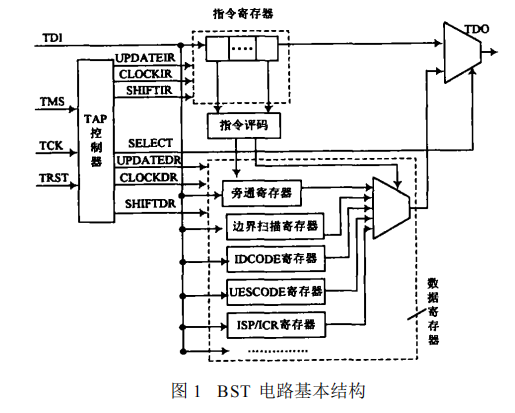

的数据寄存器通常执行内部测试功能。边界扫描设备有一个专用端口,称为测试访问端口(TAP),它将输入信号路由到称为TAP控制器的控制器和寄存器单元。 TAP控制器是一个控制边界寄存器的16状态机器。图中

2019-07-01 09:31:59

运动控制器就是控制电动机的运行方式的专用控制器:比如电动机在由行程开关控制交流接触器而实现电动机拖动物体向上运行达到指定位置后又向下运行,或者用时间继电器控制电动机正反转或转一会停一会再转一会再停

2021-09-07 07:40:34

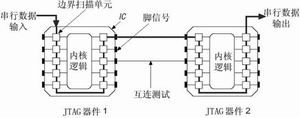

JTAG标准(IEEE 1149.1)可以测试互连的粘连、开路和短路等故障情况,这是通过“EXTEST”指令实现的,在该指令操作下TAP控制器利用BSC从互连中分离出内核逻辑。但这种测试的目的并不是测试互连

2009-10-13 17:17:59

分析边界扫描测试技术的工作机制和对测试支撑系统的功能需求,提出一种基于USB总线的高速边界扫描测试主控器的设计方案。利用CY7C68013作为USB2.0接口控制器,使用CPLD实现JTAG主控

2009-04-03 08:43:25 17

17 通过JTAG 实现对Flash 在线编程。首先, 介绍JTAG 的定义、结构及引脚的定义, 并阐述JTAG 状态机的工作原理。然后,介绍JTAG口的边界扫描寄存器,给出实现JTAG在线写Flash的电路, 和

2009-04-16 10:00:04 59

59 本文提出将广泛用于测试领域的边界扫描技术应用在基于FPGA的计算机硬件实验课程中,利用边界扫描技术解决FPGA的配置和测试两大关键问题。在PC机上编写边界扫描主控器的C语

2009-08-18 10:10:21 17

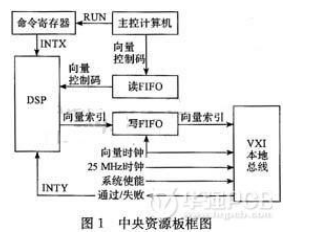

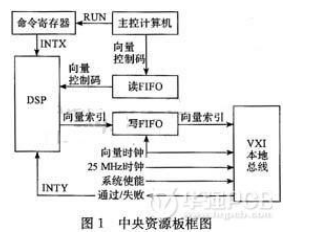

17 XI边界扫描模块接口电路的设计:根据IEEE1149.X标准和VXI总线规范,采用EDA技术对VXI边界扫描模块的接口电路进行了研究和设计,通过仿真和实际测试验证了设计的正确性,很好地

2009-10-10 14:43:06 29

29 根据系统级边界扫描测试技术的应用需求,基于VXI总线的多功能边界扫描测试控制器具备三种操作模式:IEEE1149.1 TAP模式、IEEE1149.5主控制器模式和从控制器模式。由上位机控制模件

2009-12-05 16:27:27 26

26 应用于FPGA的边界扫描设计蒋晓(中国电子科技集团 38 研究所,合肥230031)摘要:针对在FPGA芯片中的应用特点,设计了一种边界扫描电路,应用于自行设计的FPGA新结构之中

2009-12-14 11:27:14 22

22 基于ARM+FPGA的可重构控制器设计及其在加载系统中的应用:文章提出了一种基于ARM+FPGA结构的可重构控制嚣的设计方法.并采用此方法开发了用于加载系统的2通道电液伺服控制器

2010-03-02 12:03:21 29

29 JTAG边界扫描技术设计方案

JTAG(Joint Test Action Group�联合测试行动小组)是一种国际标准测试协议IEEE 1149.1兼容),主要用于芯片内部测试。现在多数的高级器

2010-03-04 14:40:05 29

29 摘要:本文介绍了支持JTAG标准的IC芯片结构、以PC机作平台,针对由两块Xilinx公司的xc9572一pc84芯片所互连的PCB板,结舍边界扫描技术,探讨了芯片级互连故障的测试与诊断策略。体

2010-05-14 09:00:17 13

13 摘 要: 本文论述了边界扫描技术的基本原理和边界扫描在电路板测试及在FPGA、DSP器件中的应用。介绍了为提高电路板的可测试性而采用边界扫描技术进行设计时应注意的一些基本

2006-03-11 13:45:44 1602

1602

摘要:MAXQ®微控制器提供的JTAG启动加载程序使外部JTAG主机能够利用一组标准命令,轻松地识别MAXQ微控制器,并对其进行编程。本应用笔记中的代码可以用作构建全功能JTAG启动加

2009-04-23 16:22:22 1341

1341

摘要: 结合自适应算法、CX-TB导通测试算法以及二进制计数测试序列,给出了用软件控制EPM9320LC84边界扫描链路,以输出图形并采集引脚对图形的响应,然后通过比

2009-06-20 10:50:13 985

985

基于ARM+FPGA的重构控制器设计

可重构技术是指利用可重用的软硬件资源,根据不同的应用需求,灵活地改变自身体系结构的设计方法。常规SRAM工艺的FPGA都可以实现

2010-03-02 10:58:41 719

719

基于JTAG仿真器的调试是目前ARM开发中采用最多的一种方式。大多数ARM设计采用了片上JTAG接口,并将其作为测试、调试方法的重要组成。

JTAG仿真器通过ARM芯片的JTAG边界扫描

2010-06-30 15:20:03 3001

3001

介绍了支持JTAG 标准的IC 芯片结构和故障测试的4-wire 串行总线,以及运用 边界扫描 故障诊断的原理。实验中分析了IC 故障类型、一般故障诊断流程和进行扫描链本身完整性测试的方案

2011-07-04 15:08:47 30

30 分析了 边界扫描 测试技术的工作机制对测试主控系统的功能需求, 提出了一种基于 USB总线 的低成本边界扫描测试主控系统的硬件设计方案; 该系统以便携式计算机为平台, 用FPGA 实现

2011-07-04 15:18:15 25

25 随着支持IEEE1149.1标准的边界扫描芯片的广泛应用,传统的电路板测试方法如使用万用表、示波器探针,已不能满足板级测试的需求,相反一种基于板级测试的边界扫描技术得到了迅速发

2012-05-30 15:06:42 45

45 边界扫描测试的原理及应用设计,有需要的下来看看。

2016-02-16 18:25:44 24

24 电子专业单片机相关知识学习教材资料之Cyclone_IV器件的JTAG边界扫描测试

2016-09-02 16:54:40 0

0 BSDL边界扫描语言的边界扫描是一个完善的测试技术。 边界扫描在自当联合测试行动组(JTAG)90年代初发明了一种解决方案来测试使用了许多新的印刷电路,正在开发和制造的地方几乎没有或根本没有测试探针板的物理访问。

2017-04-19 14:49:48 7918

7918

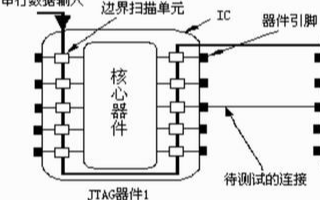

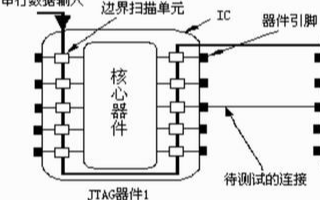

的测试系统方案及其实现,并着重介绍了JTAG总线控制器的设计。 边界扫描测试的基本原理 边界扫描测试的物理基础是IEEEll49.1测试总线和设计在集成电路内的边界扫描结构。集成电路边界结构示意图如图1所示。

2017-12-01 10:50:16 19

19 介绍了支持JTAG标准的IC芯片结构、边界扫描测试原理以及利用边界扫描技术控制IC芯片处于特定功能模式的方法。针对IC芯片某种特定的功能模式给出了设计思路和方法,并用两块xc9572 pc84芯片

2018-05-10 16:52:00 5114

5114

边界扫描测试有两大优点 :一个是方便芯片的故障定位,迅速准确地测试两个芯片管脚的连接是否可靠,提高测试检验效率;另一个是,具有 JTAG接口的芯片,内置一些预先定义好的功能模式,通过边界扫描通道来使芯片处于某个特定的功能模式,以提高系统控制的灵活性和方便系统设计。

2018-03-03 14:15:15 23575

23575

对于需要进行IC元件测试的设计人员来说,只要根据TA P控制器的状态机,设计特定的控制逻辑,就可以进行IC元件的边界扫描测试或利用JTA G接口使IC元件处于某个特定的功能模式。

2018-03-03 14:26:08 6531

6531

Hercules系列微控制器使用教程选择JTAG仿真器

2018-08-13 02:37:00 3750

3750 安捷伦边界扫描软件包支持符合IEEE标准1149.1的数字设备的测试。测试开发人员可以有效和高效地测试数字设备,同时显著减少测试开发时间。当边界扫描被实现时,故障覆盖和诊断可以增加。本章提供了关于边界扫描和IEEE标准1149.1的概述和背景信息。

2018-12-04 08:00:00 0

0 边界扫描技术的基本思想是在芯片管脚和内部逻辑之间增加了串联在一起的移位寄存器组,在边界扫描测试模式下,寄存器单元在相应的指令下控制引脚状态,从而对外部互连及内部逻辑进行测试。边界扫描结构定义了4个基本硬件单元:测试存取口(TAP)、TAP控制器、指令寄存器和测试数据寄存器组。

2019-04-25 15:09:57 1202

1202

JTAG的接口是一种特殊的4/5个接脚接口连到芯片上 ,所以在电路版上的很多芯片可以将他们的JTAG接脚通过Daisy Chain的方式连在一起,并且集成电路只需连接到一个“JTAG端口”就可以访问一块印刷电路板上的所有集成电路。

2019-11-15 07:08:00 3349

3349

会进行边界扫描测试,然后进行全面的功能测试,以确保正确的实时数字和模拟性能。

2019-08-14 23:00:00 5123

5123 JTAG是Joint Test Action Group的缩写,是IEEE 1149.1标准。使用JTAG的优点:JTAG的建立使得集成电路固定在PCB上,只通过边界扫描便可以被测试。在ARM7TDMI处理器中,可以通过JTAG直接控制ARM的内部总线、I/O口等信息,从而达到调试的目的。

2020-07-20 14:46:30 3718

3718 JTAG是Joint Test Action Group的缩写,是IEEE 1149.1标准。使用JTAG的优点:JTAG的建立使得集成电路固定在PCB上,只通过边界扫描便可以被测试。在ARM7TDMI处理器中,可以通过JTAG直接控制ARM的内部总线、I/O口等信息,从而达到调试的目的。

2020-08-10 16:42:33 2021

2021 边界扫描技术的核心思想是在器件内部的核心逻辑与I/O引脚之间插入的边界扫描单元,它在芯片正常工作时是“透明”的,不影响电路板的正常工作。各边界扫描单元以串行方式连接成扫描链,通过扫描输入端将测试矢量

2020-08-23 10:56:42 703

703

JTAG是Joint Test Action Group的缩写,是IEEE 1149.1标准。使用JTAG的优点:JTAG的建立使得集成电路固定在PCB上,只通过边界扫描便可以被测试。

2020-08-27 14:18:48 2860

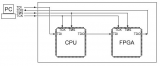

2860 JTAG可以控制(or hijack)所有IC的引脚。在图片上,也许JTAG将使所有CPU引脚输出,以及所有FPGA引脚输入。然后,通过从CPU引脚发送一些数据,并从FPGA引脚读取值,JTAG可以确保电路板连接良好。

2020-11-29 11:21:14 2280

2280

针对含DSP电路板的测试与诊断问题,本文提出一种利用边界扫描技术和传统的外部输入矢量测试相结合的方法,对含DSP电路板中的边界扫描器件的器件及非边界扫描器件进行了测试。较大的改善了含DSP电路板的测试覆盖率和定位精度,具有非常重要的实用价值。

2021-04-13 16:35:03 9

9 边界扫描测试技术 不属于 coresight架构,边界扫描测试技术 被 coresight 架构 使用.综述 联合测试行动组(Joint Test Action Group,简称 JTAG)提出

2021-12-20 19:47:33 20

20 一、JTAGJTAG的基本原理是在器件内部定义一个TAP(测试访问口),通过专用的JTAG测试工具对内部节点进行测试。除了TAP之外,混合IC还包含移位寄存器和状态机,该状态机被称为TAP控制器,以执行边界扫描功能。JTAG测试允许多个器件通过JTAG接口串联在一起,形成一个JTAG链,能实现对各个器件分别测试

2021-12-22 19:05:58 17

17 边界扫描,一种系统级嵌入式测试的使能技术

2022-11-15 19:33:58 0

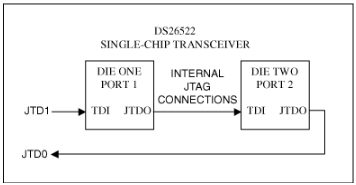

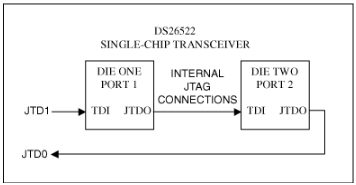

0 本应用笔记描述了DS26522双端口、单芯片收发器的JTAG硬件边界扫描链。DS26522由两个骰子组成,JTAG功能与两个以菊花链方式连接在一起的独立器件相同。本应用笔记包含JTAG扫描链的完整细分,并解释了如何访问边界中的所有扫描单元。

2023-01-11 15:53:32 913

913

通过使用一组标准化命令,MAXQ微控制器提供的JTAG引导加载程序允许外部JTAG主机轻松识别和编程任何MAXQ微控制器。

2023-02-21 11:22:46 719

719

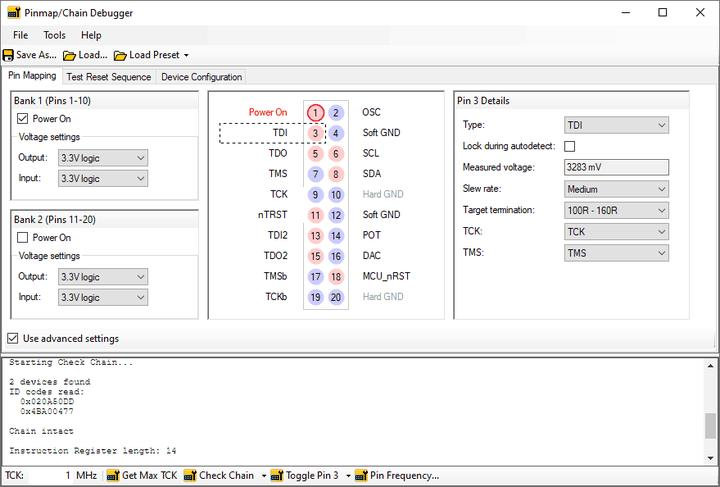

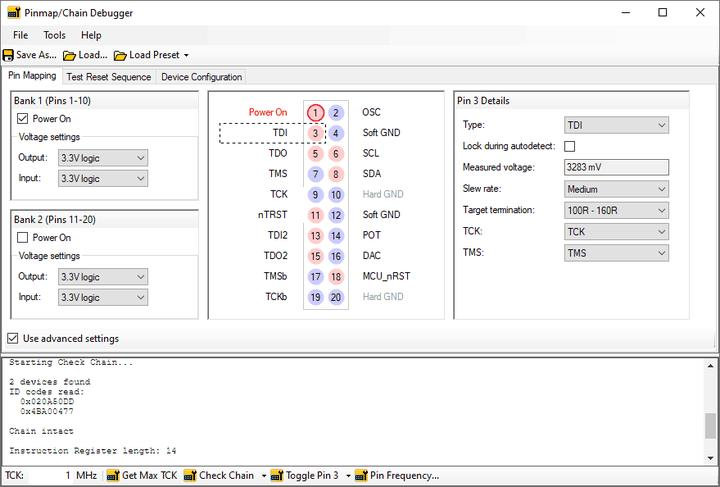

JTAG链调试器(JTAG Chain Debugger),随XJTAG的安装包一起安装,是一个功能强大的工具,旨在帮助您解决JTAG链的问题。

2023-07-19 14:41:07 318

318

BSDL文件可以在一些边界扫描的软件中被使用,如XJTAG,TopJTAG等等,通过加载对应的BSDL文件可以实现对芯片外部所有管脚的读取和控制。具体使用方法,我会在后面的文章介绍。

2023-09-10 10:15:09 446

446

前面两篇文章介绍了边界扫描的基本原理和BSDL文件,本文文章介绍边界扫描测试实际使用的两款软件工具,在后面的实战应用部分,会演示基于STM32和FPGA的边界扫描测试应用。

2023-09-11 14:34:56 1278

1278

前面几篇文章,介绍了关于JTAG边界扫描的一些基础知识和常用的调试软件。

2023-09-12 12:27:33 585

585

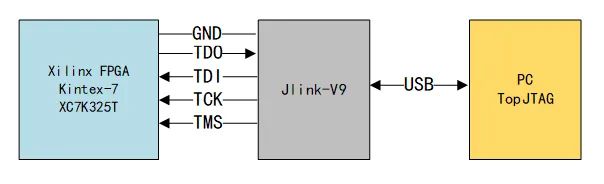

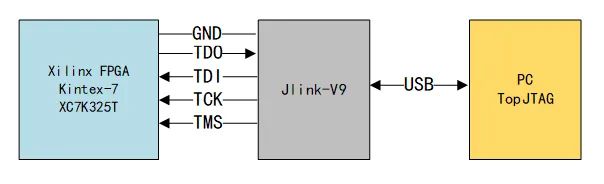

上一篇文章,介绍了基于STM32F103的JTAG边界扫描应用,演示了TopJTAG Probe软件的应用,以及边界扫描的基本功能。本文介绍基于Xilinx FPGA的边界扫描应用,两者几乎是一样。

2023-09-13 12:29:37 655

655

电子发烧友App

电子发烧友App

评论