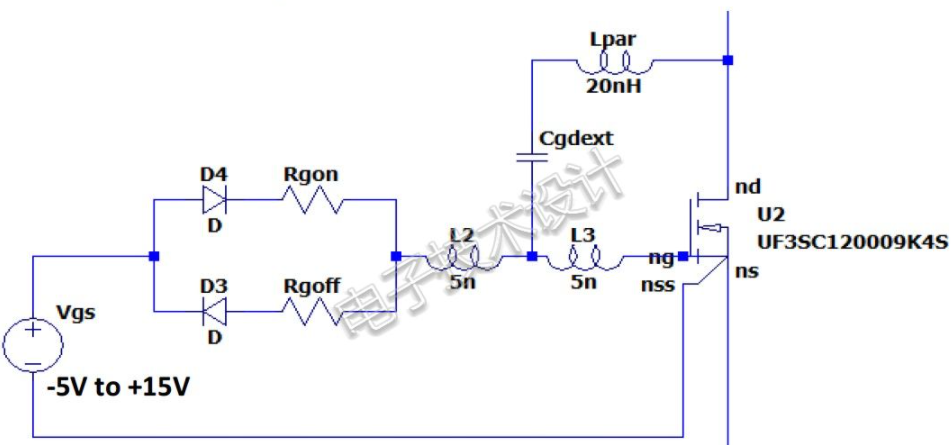

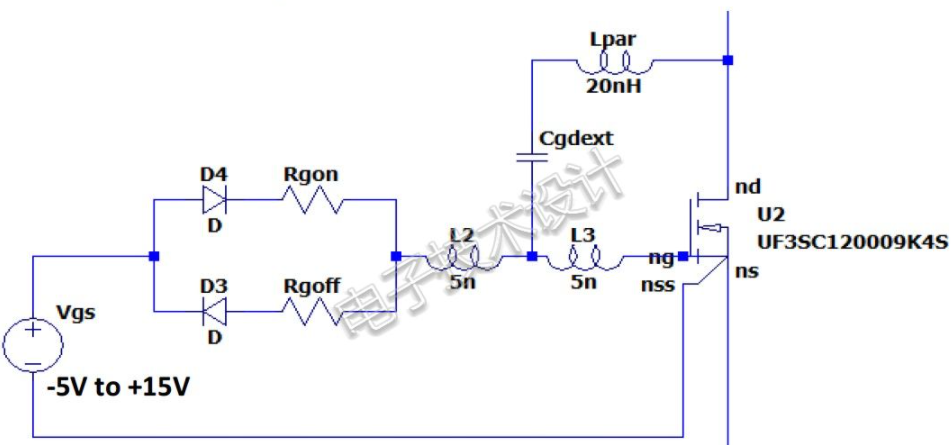

当热插拔控制电路的输出发生短路时,会触发内部断路器功能并断开电路。但在内部断路器做出反应之前,刚开始的短路电流可能达到数百安培。通常热插拔控制器断路器的延迟时间是200ns至400ns,再加上栅极下拉电流有限,栅极关闭时间可能需要10µs至50µs。在此期间,会产生较大的短路电流。

2019-03-18 14:11:00 26

26 本文重点而又全面地介绍了三种将dv/dt从45V/ns降至5V/ns而不带来过长开/关延迟时间的方法:使用外部栅漏电容器、对器件增加RC缓冲电路,以及使用JFET直接驱动。在每种情况下,都是

2021-01-05 16:10:32 2844

2844

20个常用模拟电路分享

2023-09-08 10:26:55 2886

2886

100欧姆 1K,10K三档量程怎么自动换挡的电路图

2011-08-31 12:27:35

200Smart模拟量变频器控制应用一、变频器控制1.开关量多段速2.模拟量控制PLC输出0-10V或者0-20mA控制变频器的频率为0-50HZ给PLC0-27648,PLC会输出标准模拟

2021-07-02 08:08:12

200NS - Standard Recovery Diodes (Stud and Flat Base Type) - Naina Semiconductor ltd.

2022-11-04 17:22:44

20个模拟电路,

2011-11-28 02:45:28

20个经典模拟电路 介绍的都是基本电路 很值得小白去学习!!!

2016-06-29 10:46:16

20个经典模拟电路, 你必须会的哦.

2013-06-09 10:57:24

正向压降(VSD)为1.5V,反向恢复时间(trr)为158NS。 20N20参数描述型号:20N20封装:TO-220F特性:低功耗场效应管电性参数:20A 200V连续二极管正向电流

2021-12-02 16:32:11

针对模拟电路中存在的非线性问题,提出一种以模拟电路分形特征为输入量的故障诊断方法。通过对多测试分量数据进行分形特征提取,输入神经网络建立信息融合中心融合处理各分形特征量,利用多源性互补信息减少模拟

2010-05-06 08:57:26

值、相位都和仿真值接近,但用示波器观测输出信号时发现,输出波形有非常大的底噪,并且测了一会电路莫名其妙失效了,输入为10Hz,6V幅值的正弦波,运放的in-和out端只能输出-11.84V直流,没有

2018-11-26 15:03:16

` 本帖最后由 仅侑的执着 于 2017-11-1 09:55 编辑

产品简介 ASD906A(20V/10A)模拟电池电源具有输出供电和输入充电功能,可模拟电池的充电、放电。该设备主要

2017-10-31 13:46:47

无毛刺 。 可 ADuM3200 的输出 却总是 存在 10nS 到20nS 的毛刺。 急求 AD 公司 技术专家 给予 解答 ,万分感谢 。。急。。

2018-08-17 06:59:53

Photodiode 200ns

2023-03-28 18:44:36

Photodiode 200ns

2023-03-28 18:44:36

您好,我们公司已购买示波器:“MSOX3024A示波器:200 MHz,4,模拟增强16数字通道”。我们在测试的硬件设备中对SDRAM执行测量信号。信号周期可以是0.5ns(10 ^( - 9)秒

2019-02-14 16:47:49

”,REFCKF_FREQUENCY是200.0(默认值)如果我将CNTVALUEIN设置为31(最高抽头),那么我得到2.5 ns的DATAOUT延迟(应该是5 ns而不是?)。如果我订

2020-06-13 08:47:07

本帖最后由 现在/明白 于 2018-1-24 10:10 编辑

门延迟大于cpu时钟?那cpu中的运算器是怎样工作的呢?它内部是不是低于1ns延迟的门电路呀?

2018-01-24 10:07:29

线3D7428-2.5延迟线DDU222F-200延迟线3D7428-4延迟线DDU222F-250延迟线3D7428-5延迟线DDU224F-10延迟线3D7428-7.5延迟线DDU224F-20延迟

2021-06-04 17:02:58

特征•总延迟62ns•2ns延迟步进增量•在±5V电源下运行•高达122MHz带宽•低功耗•20 Ld QFN(5毫米x 5毫米)包装•无铅(符合RoHS)应用•RGB的倾斜控制•模拟波束形成

2020-09-17 17:22:08

Cyclon IV FPGA做个信号采集转换的电路,加了个IS61WV5128BLL的ram,按手册FPGA用50MHz(20ns)读写RAM正常,但换到100MHz时钟时就出现读出的数据是上个地址写入的数据,手册上貌似这个RAM是可以10ns读写的啊。。。

2018-05-23 16:21:19

我的程序和仿真都没有问题,但是仿真的时候,发现软件默认的周期是200ns,我想要得到周期20ns的应该怎么设置?先谢谢给位前辈了{:soso_e183:}!!

2012-05-05 15:10:02

各位前辈,我是一个新手,我在做仿真的时候需要一个周期为20ns的时钟信号,但是发现软件系统默认的是200ns的,请问我在如何设置?{:soso_e183:}小生在这里先谢谢各位前辈了!

2012-05-05 15:18:22

盛铂科技SWFA200捷变频频率综合器是一款在频率范围内任意两点频率的跳频时间在4uS以内的高速跳频源,其输出频率范围为200MHz至20GHz,频率的咨询4006218906最小步进为10

2021-11-04 13:46:16

详细说明:TLP352是可直接驱动中等容量IGBT或者功率MOSFET的DIP8封装的IC耦合器。该产品的延迟时间为200 ns,光电耦合器之间的传输延迟时间差(PDD*) 为90 ns(上述

2019-09-20 09:03:36

有没有大佬知道TMS320C6748IO口中断的响应和建立时间是多少啊? 手里现在打算用IO口中断检测一个周期为200ns的FPGA时钟信号,但是测试时发现IO中断很慢,和需求差别很远,这个FPGA

2021-10-14 15:17:35

UPS的延迟启动电路及UPS输出负载百分比指示电路

2019-05-10 11:31:13

·集成阶跃恢复二极管输出:50Ω,SMA(母);·< 60ps过渡时间;两路2.5V~6V可调幅度输出;·±1ns时间偏移,1ps步进;·200ns~4μs脉冲宽度;1μs~1s内部时钟周期

2017-06-21 09:47:01

在Verilog的建模中,时间尺度和延迟是非常重要的概念,设置好时间尺度和延迟,可以充分模拟逻辑电路发生的各种情况和事件发生的时间点,来评估数字IC设计的各种要求,达到充分评估和仿真的作用。注意延迟

2021-08-16 14:16:54

类型,因此参考clk为200M,因此最大延迟时间约为2.5ns(31 * 78ps)。对? 我该怎么做才能产生3 ns的dq延迟?以上来自于谷歌翻译以下为原文Hi,I am adding a NAND

2019-03-29 14:03:35

在stm32f1中,如何使用定时器对一个脉宽为200ns的脉冲(模拟信号)进行计数。是否可以用内置比较器对脉冲信号进行整流后再用定时器计数?f1系列能否完成200ns的采样?

2020-04-27 14:53:08

9300超低压降:45mV/20mA, 2.3V至5.5V的工作电压,电流匹配精度为±1%;NS9300驱动4路LED,每路电流20mA;NS9300 PWM调光:调光频率高达50KHz;NS9300内置过热保护电路,无EMI和开关噪声, 关机电流

2011-08-07 19:33:26

; data_b = 1;//200ns之后,data_a=0;data_b=1;13#200 data_a = 1; data_b = 0;//200ns之后,data_a=1;data_b=0

2019-12-13 16:43:08

,刚开始的短路电流可能达到数百安培。通常热插拔控制器断路器的延迟时间是200ns至400ns,再加上栅极下拉电流有限,栅极关闭时间可能需要10µs至50µs。在此期间,会产生较大的短路电流。本电路用于

2019-03-18 14:01:13

LMH7220的上升和下降时间约为 0.6 ns,而传播延迟时间约为2.7 ns。5V供电时,中心频率为70MHz,带宽为10Hz-20MHz。根据芯片资料,这款芯片应该能对80MHz的正弦信号进行

2023-03-20 16:22:35

4.5v,Convb信号200ns,低脉冲,Busy始终为低电平。若只提供3.3v供电,AVCC实测为2.5v,Busy信号正常,为4us左右的高脉冲。

现想咨询这个情况该如何排错?电路参考的是手册中9电容的电路图/

2023-12-04 06:14:01

进行音量自动调节,延迟时间可以控制的自动增益延迟音响放大器。基本要求1) 输入音频信号(10Hz~1KHz),输出可以带200Ω负载或驱动8Ω喇叭(2~5W),输出波形基本不失真。(20分)2) 当

2016-05-23 19:48:14

如何使用ucf约束文件为输入数据添加一个小延迟?我试图为来自名为“chana_rd”的引脚的输入数据添加一个小延迟,如何添加此延迟?另外,我对chana_rd有一个约束如下。这会如何影响延迟

2019-03-28 12:03:32

我有什么: STM32L496,模拟信号输入。我需要的是:在某种级别的模拟信号上,以一定的延迟开始 ADC 转换(80...200 ns。基本上,55-80 ns 是内置比较器的传播延迟,20 ns

2023-01-06 07:11:14

**第一至第三章**Q1. 若存储器的数据总线宽度为32位,存取周期为200ns,则存储器的带宽是多少?存储器的带宽指单位时间内从存储器进出信息的最大数量。存储器带宽 = 1/200ns ×32位

2021-07-28 06:23:01

对于晶振为24M的,C8051F310.延迟10us的 延迟函数怎么编写{:4:}{:4:}{:4:}

2014-08-13 13:13:38

当今的一些高精密模拟系统需要低噪声正负电压轨来为精密模拟电路供电,这些电路包括模数转换器 (ADC)、数模转换器 (DAC)、双极放大器等等。如何产生清洁、稳定的正负电压轨为噪声敏感型模拟组件供电是摆在我们面前的一个设计挑战。

2019-08-13 06:03:34

1.7ns?以下引自DS152:2.如果上述问题的答案是肯定的,我该如何处理不同的ADC采样率?例如,如果ADC以20MHz @ 10bit运行,则LVDS输出频率为100MHz,位宽为5ns。如果我将

2020-06-17 16:16:23

若存储器的数据总线宽度为32位,存取周期为200ns,则存储器的带宽是多少?说明刷新有几种方法?指令是指什么?

2021-10-19 10:20:42

指针式万用表RX10K档电压为12V,其它电阻档为2.4V。那么为什么会有电压呢,这样测量电阻时会不会破坏电阻啊

2014-09-15 15:41:11

约为16 ns,但我试图将其降低到10 ns以内。我尝试了OFFSET约束,它将延迟从21ns降低到16ns。但是我还能用什么来进一步降低延迟?或者,如果这是最好的FPGA芯片(Spartan 3E

2019-03-25 14:59:33

(ADC0809的说明书要求start的脉冲宽度不超过200ns,典型值为100ns),请大佬们帮帮忙若是需要换一个频率较大的晶振,请问这样还能与PC机进行通信吗?波特率会受影响吗?使用较大晶振后,再编写程序,会有什么影响(使用的keil 4)?麻烦大佬们帮忙

2018-03-01 17:46:04

有个问题身边也没有人问 只能来论坛请教了 请各位大神指导啊!!!想实现FPGA接DA芯片输出模拟电压,DA芯片为SPI传输,FPGA程序为计数,计数一次步长时间为200ns左右,FPGA时钟频率为

2015-04-24 22:35:09

LTC2325-12

1 应用:通过MCU软件控制ADC进行不定时的单次采样,可能数秒钟1次或者连续以200ns时间间隔采集n组数据等突发式的采集。ADC不进入待机状态。这种数秒钟1次的单次或者

2024-01-08 06:55:22

分五档 10,15,20,25,30,自动改变转速

2015-12-27 16:46:06

选择1X档时,信号是没经衰减进入示波器的。而选择10X档时,信号是经过衰减到1/10再到示波器的。当选择10X档时,应该将示波器上的读数也扩大10倍,这就需要在示波器端可选择X10档,以配合探头

2019-05-20 14:43:22

问题:能否在200 ns内开启或关闭RF源?

2019-03-01 08:56:59

提出一种独特但简单的栅极脉冲驱动电路,为快速开关HPA提供了另一种方法,同时消除了与漏极开关有关的电路。实测切换时间小于200 ns,相对于 1 μs 的目标还有一些裕量。其他特性包括:解决器件间差异

2018-10-24 10:21:59

如题 请教!时钟:内部64M为何我实际测量约在400ns而不是200ns左右?

2019-03-01 08:23:26

有没有办法在电路包络模拟中使用延迟元件,这样只会延迟包络波形(而不是RF波形)? 以上来自于谷歌翻译 以下为原文Is there a way to use a delay element

2019-07-22 06:46:33

大家好,我目前正在为我的项目寻找评估委员会。我的设计中有一条时间关键路径。该路径需要4个触发器,2个多路复用器和一个用于操作的逻辑门。通过该路径的传播时间(延迟)应小于30ns。这可能与FPGA有关吗?如果是这样,可以推荐哪种评估板和时钟频率?最好的祝福

2019-09-26 10:12:35

输入信号。 SY89296L是一款可编程延迟线,可通过数字控制和模拟控制延迟输入信号。延迟时间从2.2ns到12.43ns不等。此外,输入为LVPECL,使用2.5V或3.3V电源

2019-03-05 08:20:02

工程师应该掌握的20个模拟电路

对模拟电路的掌握分为三个层次。初级层次是熟练记住这二十个电路,清楚这二十个电路的作用。只要是电子爱

2010-03-29 11:35:15 1323

1323 本文提出了一种数字延迟单元的设计方案,该方案能够实现0.1ns的延迟度精度和10ms的动态范围,通过调节该方案的工作参数可以很方便的实现更大的动态范围。该电路在Virtex5系列的FPGA

2010-07-17 18:03:31 19

19

具有20ns转换时间的精密振荡器电路图

2009-04-15 09:31:02 474

474

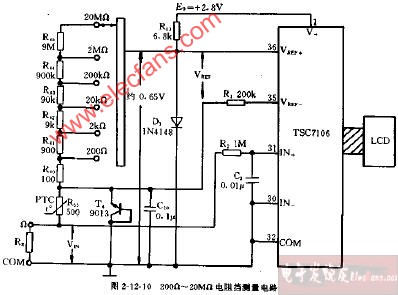

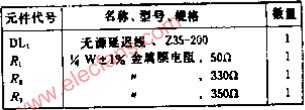

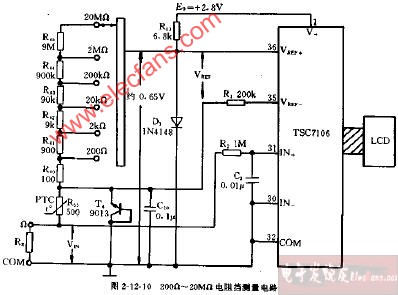

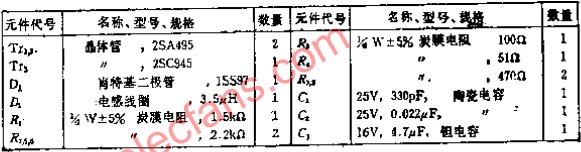

DT890B型200Ω~20MΩ电路图

2009-07-18 17:26:15 1062

1062

延迟线电路,延迟线电路是什么意思

延迟线电路的定义

2010-03-09 11:30:46 1148

1148 延迟时间在5NS以内的高速响应微分脉冲发生电路

电路的功能

使用

2010-05-10 16:54:51 1460

1460

电子电路工程师必备的20种模拟电路电子电路工程师必备的20种模拟电路

2016-01-11 14:04:33 0

0 工程师应该掌握的20个模拟电路,入门必备

2016-02-17 15:31:12 37

37 20个经典模拟电路资料_全学懂后基础就扎实了。

2016-06-21 17:02:48 145

145 包含电子工程师应该掌握的20个经典的模拟电路

2016-08-25 15:52:39 79

79 工程师应该掌握的20个模拟电路,感兴趣的小伙伴们可以瞧一瞧。

2016-09-18 17:34:53 0

0 基于NS2模拟器的TCP仿真的设计和实现_钱开国

2017-03-17 17:32:28 2

2 WSF25N10-TO-252 N 200V20A

2017-07-10 14:06:25 11

11 电子发烧友网为你提供Broadcom(ti)ASMT-BB20-NS000相关产品参数、数据手册,更有ASMT-BB20-NS000的引脚图、接线图、封装手册、中文资料、英文资料,ASMT-BB20-NS000真值表,ASMT-BB20-NS000管脚等资料,希望可以帮助到广大的电子工程师们。

2019-07-04 11:58:02

手册本文档的主要内容详细介绍的是NS-SW300和NS-SW200型超低音扬声器的维修手册免费下载。

2019-11-19 08:00:00 19

19 学习51单片机及模拟电路资料包括20个模拟电路和C语言程序免费下载。

2021-03-12 17:40:45 42

42 LT1721 Demo Circuit - 0ns to 10ns Pulse Width Generator

2021-03-24 21:46:28 9

9 LTC6994/LTC6993演示电路延迟单次(延迟50ms,单次10ms)

2021-04-10 10:35:33 4

4 初学者必知的20个模拟电路

2021-05-29 09:27:46 436

436 LT1721演示电路-0 ns至10 ns脉冲宽度发生器

2021-06-03 16:35:16 25

25 LTC6994 LTC6993演示电路延迟单次(延迟50ms,单次10ms)

2021-06-09 20:54:37 93

93 由于内部断路器延迟和有限的MOS栅极下拉电流,许多热插拔控制器在短路输出后的前10μs至50μs内不限制电流。结果可能是几百安培的短暂流量。一个简单的外部电路通过最小化初始电流尖峰并在200ns至500ns内终止短路来解决这个问题。

2023-03-17 11:34:07 623

623

由于内部断路器延迟和有限的MOS栅极下拉电流,许多热插拔控制器在短路输出后的前10μs至50μs内不限制电流。结果可能是几百安培的短暂流量。一个简单的外部电路通过最小化初始电流尖峰并在200ns至500ns内终止短路来解决这个问题。

2023-03-31 11:15:30 570

570

电子发烧友App

电子发烧友App

评论