大型时钟树使用多种类型的传输线,跨越多块电路板和多条同轴电缆,通过多个时钟器件路由时钟信号的情况并不少见。即使采用最佳实践做法,这些介质中的任何一种都可能带来大于10ps的相位偏差。然而,在一些

2023-04-06 14:22:35 914

914

简单时钟电路图

2009-07-16 11:00:19 11000

11000

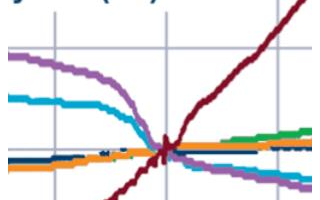

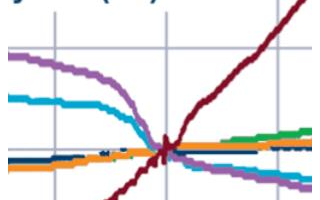

高增益设计良好的时钟缓冲器将倾向于抑制AM并且仅通过相位(定时)误差。然而,没有输入时钟缓冲器是完美的,并且可以发生一些AM-PM转换。这种转换的机制和数量通常会根据调制频率而有所不同。

2018-03-23 09:07:32 8888

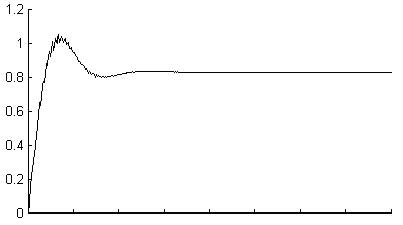

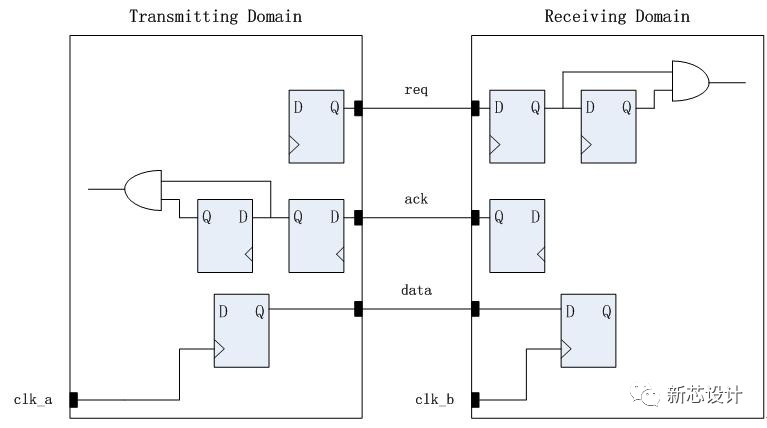

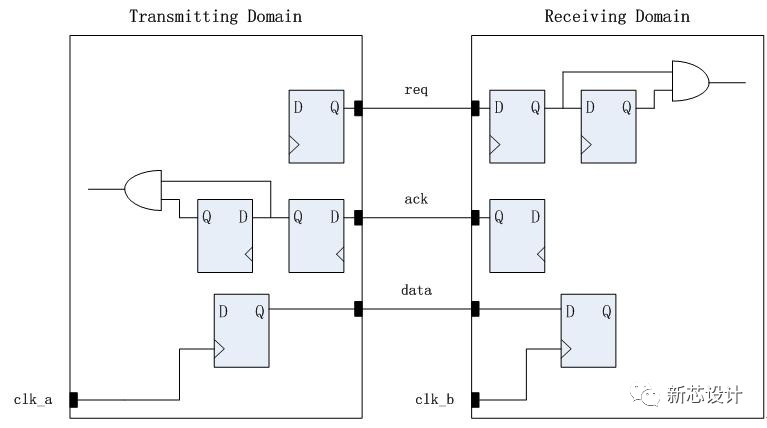

8888 在多时钟设计中可能需要进行时钟的切换。由于时钟之间可能存在相位、频率等差异,直接切换时钟可能导致产生glitch。

2020-09-24 11:20:38 5317

5317

在所有器件特性中,噪声可能是一个特别具有挑战性、难以掌握的设计课题。本文主要介绍时钟噪声对于高速DAC相位噪声的影响。

2022-07-28 09:35:18 931

931 32单片机时钟相关知识使用HSE配置系统时钟,可以用来控制灯的亮灭快慢

2021-12-06 07:01:47

(第2次书写,不对请指正,谢谢)HSE:高速外部振荡器,晶体/阻谐振器、负载电容器(其值根据HSE调整)尽可能靠近振荡器引脚 置“1”时释放外部时钟源(HSE旁路) 时钟控制寄存器信号

2022-02-17 07:20:34

时钟相噪对ADC性能的影响是什么?锁相环的基本原理和相噪优化方式

2021-04-07 06:25:40

经常容易搞错AM,FM或PM,他们很难区分呢?时钟相位噪声图中的杂散信号为什么会影响时钟的总抖动?

2021-03-05 08:06:14

AD7606的关于SPI通信的时钟极性和时钟相位要求是什么?

我的主控芯片采用SPI有AD7606通信,我在数据手册中好像没有看到专门关于SPI通信时钟极性和时钟相位的描述和规定?请问AD7606的SPI通信对时钟极性和时钟相位的规定是什么?

谢谢。

2023-12-01 06:56:43

本章节介绍了 Cyclone® IV 器件系列中具有高级特性的层次时钟网络与锁相环 (PLL),包括了实时重配置 PLL 计数器时钟频率和相移功能的详尽说明,这些功能使您能够扫描 PLL 输出频率,以及动态调整输出时钟相移。

2017-11-14 10:09:42

HbirdV2-SoC中QSPI0的时钟极性CPOL和时钟相位CPHA可以通过SPI_SCKMODE寄存器来配置;在QSPI1和QSPI2中没有找到相关寄存器,如何配置QSPI1和QSPI2的时钟极性CPOL和时钟相位CPHA。

2023-08-12 06:17:48

LTC6915的采样时钟是多少,与FPGA 系统时钟相同吗

2023-11-14 07:55:38

,我觉得指令周期应该随时钟周期变化的吧,为什么手册上直接写它的指令周期是62.5ns呢?在程序中只禁看门狗,对时钟相关寄存器不操作的情况下,使用内部晶振,此时的指令周期到底是多少呢?

2013-07-25 11:22:30

RTC实时时钟相关知识点汇总,不看肯定后悔

2021-11-23 07:12:17

Xilinx FPGA配置clocking时钟动态相位输出

2019-08-05 11:35:39

我使用megawizard生成PLL,外部50M,生成3个依次延迟90度的100M时钟,C0 0度, C1 90度 ,C2 180度,然后使用modelsim 门级仿真,出来的结果不太对啊!不应该是依次延迟1/100M/4么?RTL级仿真是对的。。这该如何解决。。再调那个相位值?

2015-01-20 17:44:39

最近使用megawizard生成PLL,外部50M,生成3个依次延迟90度的100M时钟,C0 0度, C1 90度 ,C2 180度,然后使用modelsim 门级仿真,出来的结果不太对啊!不应该是依次延迟1/100M/4么?RTL级仿真是对的。。这该如何解决。。再调那个相位值?

2015-01-13 16:43:02

你好,我们在设计中需要使用 hmc7044 产生一系列频率为 204MHz 且相位对齐的时钟,并且所有的 204MHz 时钟都由 外部VCO输入时钟 816MHz 所产生。

目前所有的时钟都已经获取

2023-12-01 10:15:39

关于SPI的配置问题,就是时钟的极性和时钟相位问题

2016-07-04 16:54:19

我需要生成一个与外部信号相位匹配的FPGA内部时钟。通过相位匹配,我的意思是外部信号和内部时钟的相对相位是已知且稳定的。有证据表明这是PLL inV5 / 6的预期使用模型。 V6时钟指南说

2019-01-14 12:32:53

STM32F030_RTC详细配置说明今天总结RTC(Real Time Clock)实时时钟相关的知识。在进行RTC的讲解前,我先对BKP进行一个简单的讲解。STM32的RTC模块和时钟配置系统

2021-08-05 08:19:21

当试图另两片AD9361的LO和BB时钟相位固定时,手册上提供了两种办法,一个是两片AD9361的XTALN共源(低频30Mhz-80Mhz),然后片内的TxRFPLL/RxRFPLL/BBPLL

2023-12-13 07:51:02

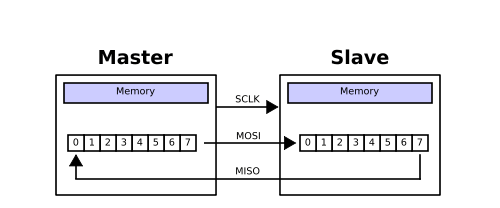

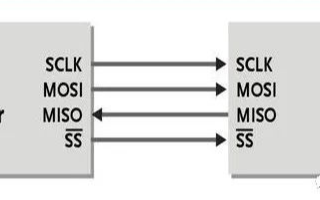

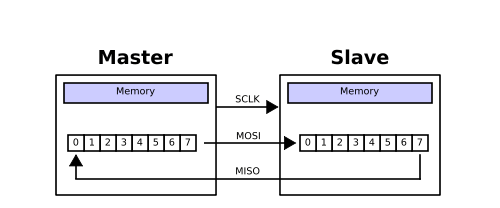

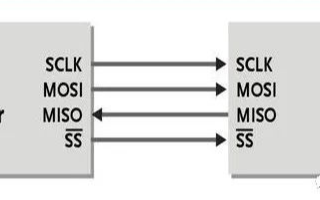

按位传输,高位在前,低位在后,为全双工通信,数据传输速度总体来说比 I2C 总线要快,速度可达到 Mbps 级别。根据时钟极性和时钟相位的不同,SPI 有四个工作模式。 时钟极性有高、低两极: 1

2018-11-30 11:42:41

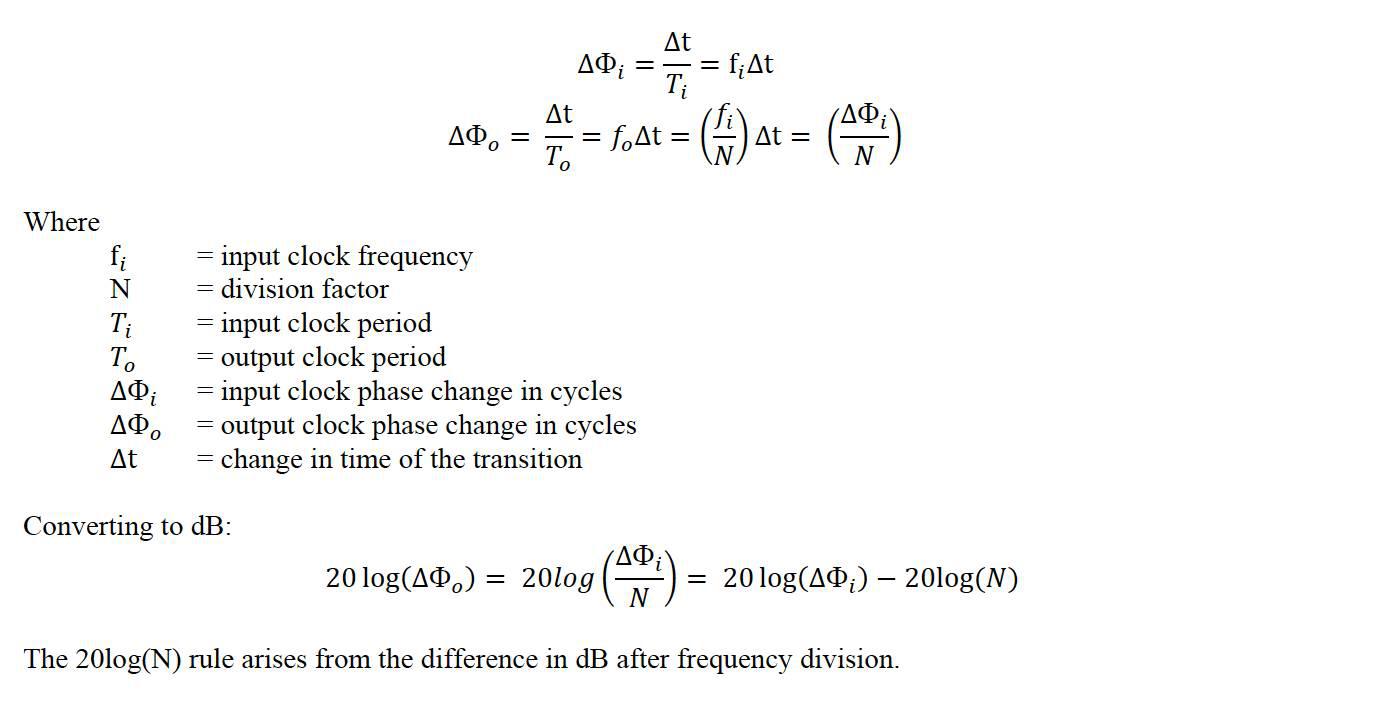

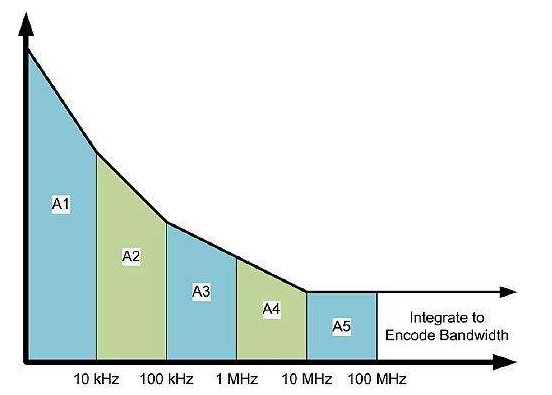

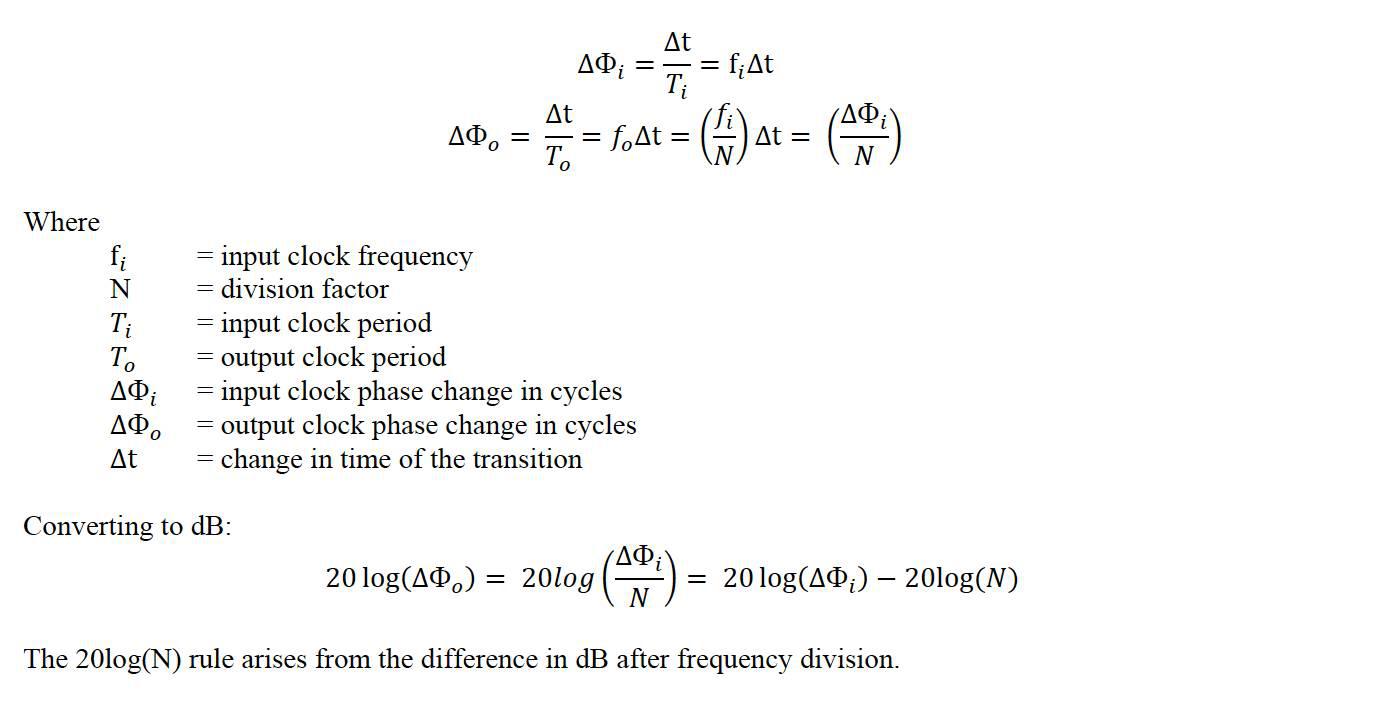

本期我将讨论在测量较低时钟频率的相位噪声和相位抖动时出现的一个非常常见的问题。在所有条件相同的情况下,我们通常期望分频的低频时钟产生比高频时钟更低的相位噪声。在数量上,你可能会记得这是20log(N

2021-06-24 07:30:00

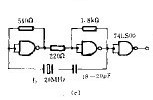

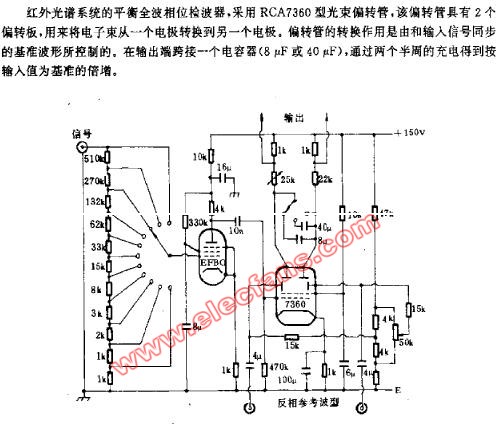

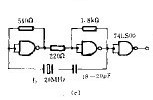

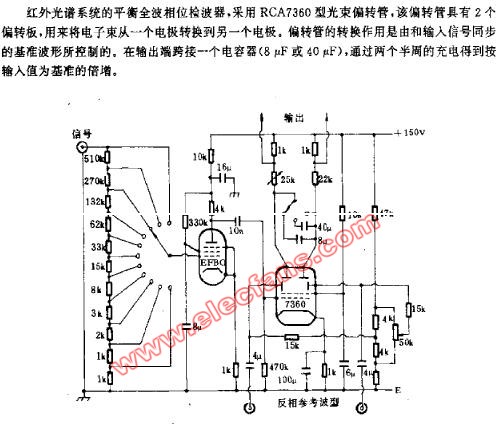

电压电流相位检测电路

目的是想知道电压电流的相位谁超前谁。这样可以调整频率使得电路工作在谐振状态,达到功率最大,效率最高。这个电路应该不能检测出具体的相位差是多少吧?如果要检测出具体的相位

2023-12-22 18:21:23

所有噪声源,便可分析和管理相位噪声,并确保信号链设计一次成功。图22.相位噪声预算示例参考电路Brannon,Brad。应用笔记AN-756,采样系统以及时钟相位噪声和抖动的影响。ADI公司,2004

2018-10-17 10:22:55

22所示。图中也显示了仿真的相位噪声曲线,其与测量结果相当吻合。在某些区域,时钟相位噪声仍占主导地位。图21.AD9162相位噪声结语面对上文讨论的所有噪声源,设计人员可能会茫然不知所措。一种简单的做法

2017-05-10 14:39:39

我目前想要使用FPGA上自带的LVDS模块实现FPGA之间的通信。首先我测试了一块FPGA自收自发,我的全局时钟25M,数率200M,4个通道,8位因子,然后测试中我发现必须调整接收模块的输入时钟相位

2014-04-03 23:27:32

的0-8输出时钟之间可以实现相位同步,那2个AD9576之间怎么实现同步来保证16个AD输出时钟相位都同步?

2023-12-05 08:16:23

HMC7044锁相环可以配出8路2.5G,相位可调的时钟吗,其中7路DCLK加一路SDCLK。特别是同组里面的两路时钟可以分开,分别调整相位吗?

2018-08-02 07:08:29

,输出80MHz;0x019寄存器中关于R、A、B计数器设置成SYNC信号同步或者异步reset。 但是发现,PLL锁定后,经过内部分频器分频出来的时钟信号和参考信号的相位差并不固定:每次上电或者给

2018-10-15 14:37:15

您好! 请问ADI是否这样的锁相环芯片,在外参考输入时钟不关的情况下,开关锁相环芯片,锁相环输出时钟相位保持一致,也就是说只要输入参考不变,开关锁相环芯片,输出时钟相位保持不变,若变,变化范围是多大, 若无此类锁相环芯片,请问ADI是否有此类问题的解决方案。 十分感谢!!

2018-08-31 11:00:43

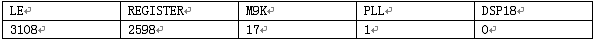

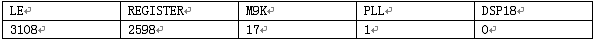

EP3C10T144C7,时钟脉冲宽度最小值0.625ns,经过仿真验证其工作频率可以达到400MHz。在时钟调整模块后加一个简单的二分频电路,就可以实现12个时钟相位的调整精度,根据不同器件的性能很

2009-10-24 08:38:08

占空比的功能。对于一个简单的设计来说,FPGA整个系统使用一个时钟或者通过编写代码的方式对时钟进行分频是可以完成的,但是对于稍微复杂一点的系统来说,系统中往往需要使用多个时钟和时钟相位的偏移,且通过编写

2022-01-18 09:23:55

种类的脉宽调整电路。这些电路大致可以分为以下三类:第一类最为简单,即采用2分频器产生占空比为50%的时钟,2分频器并不是专为调整占空比而采用的,但的确达到了这一需求;第二类通过负反馈机制,采用数字或

2008-11-19 14:39:36

相位噪声是制约DDS用于高稳定频率源的的关键指标。文中定量给出了DDS内部相位截断误差、幅度量化误差、DAC以及参考时钟源对相位噪声的影响,并着重分析了DDS外围电路对相位

2010-10-20 16:36:17 26

26 随着支持直接IF采样的更高分辨率数据转换器的上市,系统设计师在选择低抖动时钟电路时,需要在性能/成本之间做出权衡取舍。许多用于标定时钟抖动的传统方法都不适用于数

2010-11-27 17:12:46 32

32 相位表电路图

2008-02-25 21:49:13 699

699

应用于锁相环的脉宽调整电路的设计

前言

在锁相环PLL、DLL和时钟数据恢复电路CDR等电路的应用中,人们普遍要求输出时钟信号有50%的占空比,以便在时钟上升及下

2008-10-16 08:59:42 1034

1034

相位检波电路图

2008-12-24 21:54:58 5227

5227

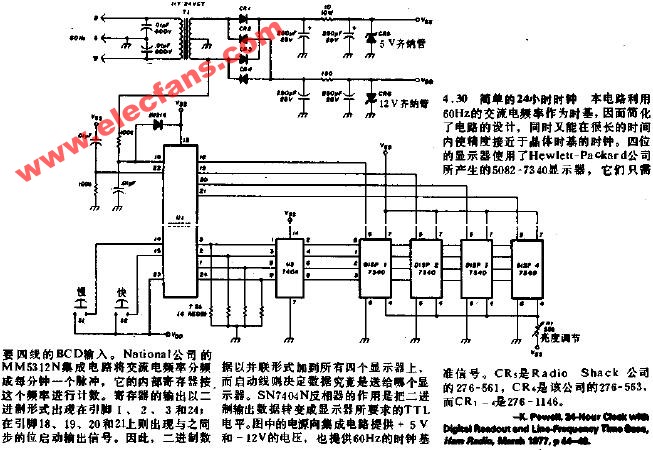

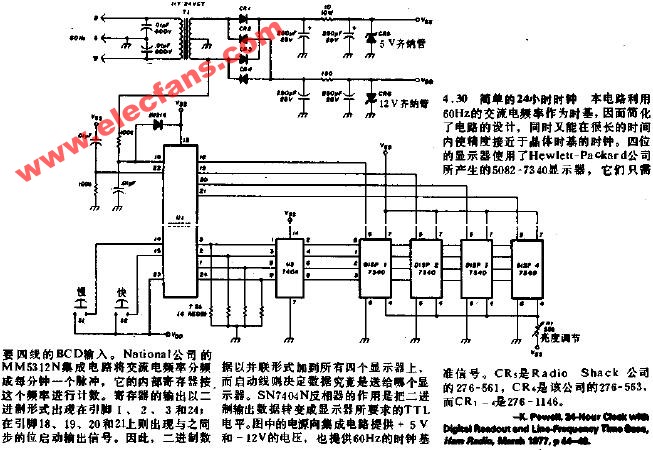

简单的24小时时钟电路

2009-01-13 20:15:47 3849

3849

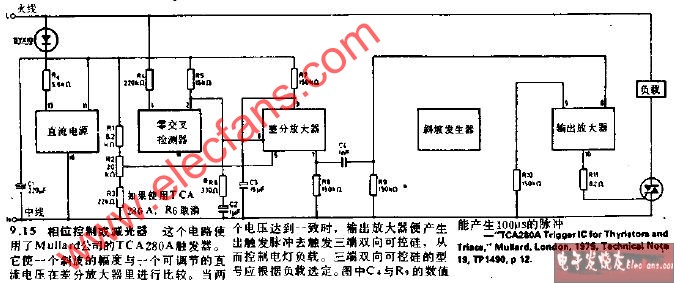

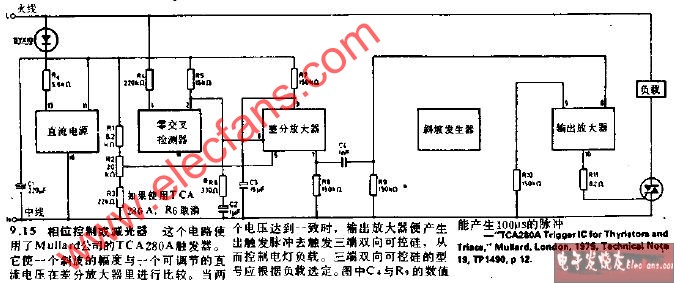

相位控制或减光器电路

2009-01-21 01:34:39 1620

1620

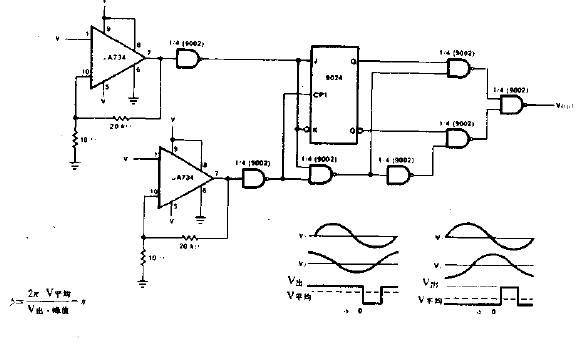

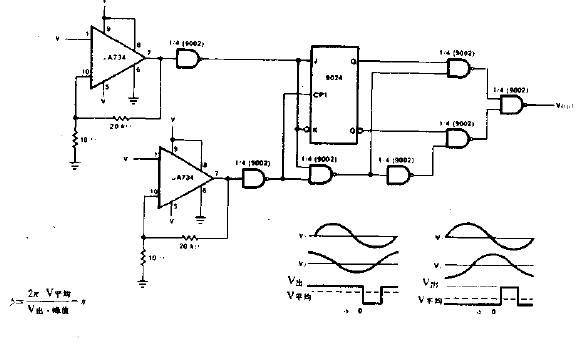

相位计电路图

2009-04-02 09:41:00 751

751

摘要:这是一篇关于时钟(CLK)信号质量的应用笔记,介绍如何测量抖动和相位噪声,包括周期抖动、逐周期抖动和累加抖动。本文还描述了周期抖动和相位噪声谱之间的关系,并介绍

2009-04-22 10:16:50 3736

3736

Inverter Amp. 反相位放大电路:

2009-10-22 09:44:19 1243

1243

在低成本FPGA中实现动态相位调整

在FPGA中,动态相位调整(DPA)主要是实现LVDS接口接收时对时钟和数据通道的相位补偿,以达到正确接收的目的。ALTERA

2010-03-25 11:45:07 2338

2338

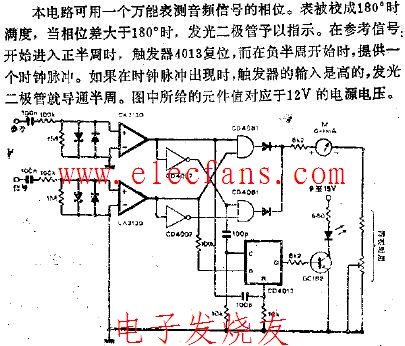

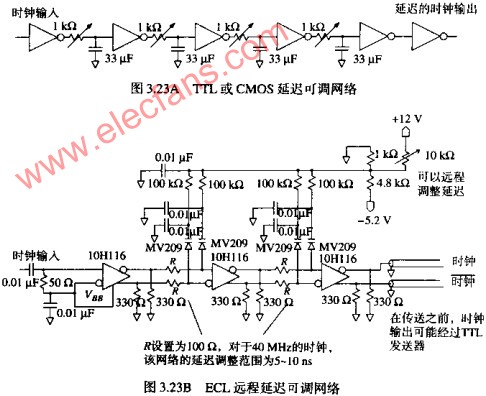

图3.24给出了CADILLAC时钟相位调整电路的框图。对于大规模生产测试,可能值得构造这样的电路。对于普通的实验测试,则太麻烦了。

2010-06-07 18:19:03 1124

1124

本文根据光纤接入数位中频系统的时钟使用情况,分析时钟抖动对类比数位转换器(ADC)和相位锁定回路(PLL)性能影响的塬理,包括相位锁定回路基本原理和相位杂讯优化方式,最后提出采用双相位锁定回路完成去抖和时钟分发的解决方案。

2013-02-26 14:13:06 1354

1354

一种基于FPGA的时钟相移时间数字转换器_王巍

2017-01-07 22:23:13 2

2 。通常的相位对齐技术由于引入了Delay_Aligner,会带来2~4nS的相位不确定,不能满足系统指标要求。 这里介绍一种利用MMCM实现多芯片相位对齐的串行收发器纠偏方法: 1) 利用图1所示电路实现多芯片间的全局时钟相位对齐。

2018-01-12 05:53:14 2356

2356

简单LED数字时钟

2018-01-18 14:18:44 49

49 本文主要介绍了七款数字时钟设计电路图。数字钟是一种用数字电路技术实现时、分、秒计时的钟表。与机械钟相比具有更高的准确性和直观性,具有更长的使用寿命,已得到广泛的使用。

2018-01-26 11:14:30 158047

158047

在FPGA中,动态相位调整(DPA)主要是实现LVDS接口接收时对时钟和数据通道的相位补偿,以达到正确接收的目的。ALTERA的高端FPGA,如STRATIX(r) 系列中自带有DPA电路,但低端的FPGA,如CYCLONE(r)系列中是没有的。下面介绍如何在低端FPGA中实现这个DPA的功能。

2018-02-16 17:32:33 10343

10343

串行外围设备接口是由 Motorola 公司开发的,用来在微控制器和外围设备芯片之间提供一个低成本、易使用的接口。这种接口可以用来连接存储器、AD/DA转换器、实时时钟日历、LCD驱动器、传感器、音频芯片,甚至其他处理器。

2018-03-20 11:43:29 12697

12697

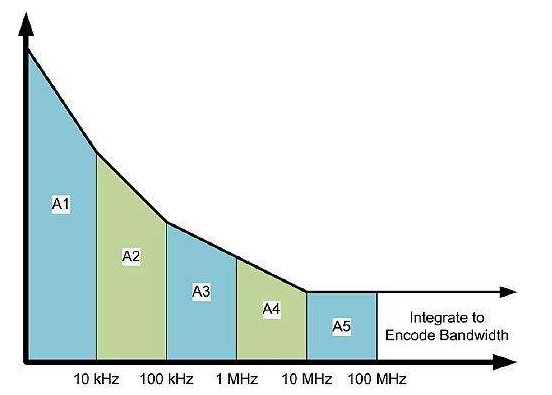

仔细观察某个采样点,可以看到计时不准(时钟抖动或时钟相位噪声)是如何形成振幅变化的。由于高 Nyquist 区域(例如,f1 = 10 MHz 到 f2 = 110 MHz)欠采样带来输入频率的增加,固定数量的时钟抖动自理想采样点产生更大数量的振幅偏差(噪声)。

2018-05-14 08:51:40 3

3 本文介绍了一种通过单边带来估计时钟源的相位噪声的通用公式。载波比(SSCR),振荡周期的周期抖动。该链接允许无缝聚合。

外部时钟源相位噪声,通常以dBC/Hz给出,与片上时钟同步电路的相位稳定

2018-05-16 17:56:54 5

5 如果一个时钟的载波频率下降了N倍,那么我们预计相位噪声会减少20log(N)。例如,每个除以因子2的除法应该导致相位噪声减少20log(2)或大约6dB。这里的主要假设是无噪声的传统数字分频器。

2018-09-28 08:14:00 10038

10038

今天我们讲一下与时钟(clock)相关的PCB的设计考虑,主要分两部分:原理图设计 - 针对时钟电路应该放置哪些器件?以及PCB布局和走线 - 如何摆放与时钟相关的元器件并正确连线达到理想的性能。

2018-11-25 11:09:41 1440

1440 大型时钟树使用多种类型的传输线,跨越多块电路板和多条同轴电缆,通过多个时钟器件路由时钟信号的情况并不少见。即使采用最佳实践做法,这些介质中的任何一种都可能带来大于10 ps的相位偏差。然而,在一些

2019-04-04 08:25:00 2648

2648

一个不寻常的电路,“tanktwanger”,提供了一些优于传统时钟合成方法的时钟产生和调整优势。您可以针对众多应用调整主电路,但在构建此VHF设计时必须注意。

2019-08-08 10:51:20 2346

2346

时钟极性(CPOL)和时钟相位(CPHA)用于设定从设备何时采样数据。CPOL决定SCLK为高时总线为空闲(CPOL=1)还是SCLK为低时总线为空闲(CPOL=0)。CPHA决定在SCLK的哪一个边沿将数据写入。

2020-07-17 15:59:36 3057

3057

SPI是单片机外设电路中常用的一种通讯方式,适用于近距离通信,通常用于芯片间的通讯,有四根线。在SPI通讯中总线时钟和总线相位也两个比较重要的概念,一般在使用SPI通信时都使用默认设置,所以容易

2020-11-12 18:09:23 13935

13935

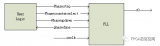

PLL 是一种用来同步输入信号和输出信号频率和相位的相位同步电路,也可用来实现时钟信号的倍频(产生输入时钟整数倍频率的时钟)。在 FPGA 芯片上,PLL 用来实现对主时钟的倍频和分频,并且 PLL

2020-11-16 17:04:44 3292

3292 一、时钟相关概念 理想的时钟模型是一个占空比为50%且周期固定的方波。Tclk为一个时钟周期,T1为高脉冲宽度,T2为低脉冲宽度,Tclk=T1+T2。占空比定义为高脉冲宽度与周期之比,即T1

2021-01-15 09:37:38 4405

4405

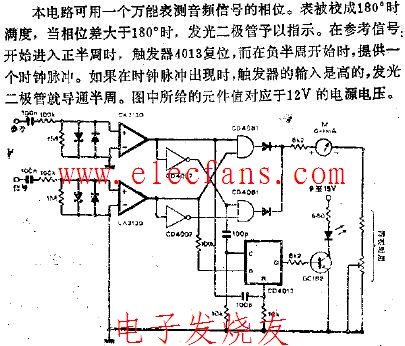

相位检测电路与仿真说明。

2021-03-18 16:14:51 68

68 电子发烧友网为你提供测量较低时钟频率的相位噪声和相位抖动资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-03-27 08:40:37 10

10 电子发烧友网为你提供如何生成和使用杂散进行测试:时钟相位噪声探讨资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-03-30 08:44:35 7

7 电子发烧友网为你提供为什么杂散会带来额外抖动?时钟相位噪声测量解析资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-04-02 08:55:37 5

5 电子发烧友网为你提供STM32F030_RTC实时时钟相关的知识资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-04-04 08:55:10 12

12 32单片机时钟相关知识使用HSE配置系统时钟,可以用来控制灯的亮灭快慢

2021-11-23 18:21:18 8

8 SWM系列关于UART/CAN/PLL等时钟相关模块,计算波特率的方法。

2022-03-18 16:52:25 6267

6267 频点变成2,399,883,450Hz,约100KHz的频偏),造成蓝牙与标准频率的对端无法通信。因此一个好的时钟电路是非常必要的,此篇文章对时钟电路中的晶振电路layout简单做一下阐述。

2022-06-06 17:12:23 6120

6120 时钟抖动使随机抖动和相位噪声不再神秘

2022-11-07 08:07:29 4

4 为高,则 CPOL 为 1。时钟相位 (CPHA) 由数据有效的边沿决定。如果数据在 SCLK 的第一个边缘有效,则 CPHA 为 0。如果数据在 SCLK 的第二个边缘有效,则 CPHA 为 1。

2023-01-12 17:05:24 555

555

大型时钟树使用多种类型的传输线,跨越多块电路板和多条同轴电缆,通过多个时钟器件路由时钟信号的情况并不少见。即使采用最佳实践做法,这些介质中的任何一种都可能带来大于10ps的相位偏差。然而,在一些

2023-03-29 02:15:02 348

348

类似于电源域(电源规划与时钟规划亦是对应的),假如设计中所有的 D 触发器都使用一个全局网络 GCLK ,比如 FPGA 的主时钟输入,那么我们说这个设计只有一个时钟域。假如设计有两个输入时钟,分别给不同的接口使用,那么我们说这个设计中有两个时钟域,不同的时钟域,有着不同的时钟频率和时钟相位。

2023-06-21 11:53:22 2002

2002

异步电路不能根据时钟是否同源来界定,时钟之间没有确定的相位关系是唯一准则。

2023-06-27 10:32:24 614

614 这是为数不多的跨越围栏是有利的情况之一。目前市面上的许多时钟产品都指定器件的相位噪声,而不指定抖动。让我们来看看如何从相位噪声变为抖动。然后,我们将能够预测具有一定抖动的ADC的SNR。一个例子将不得不等待,因为我在这里只有这么多空间。现在让我们专注于数学。下图显示了我们如何根据时钟源的相位噪声计算抖动。

2023-06-30 16:58:01 566

566

本实验活动介绍锁相环(PLL)。PLL电路有一些重要的应用,例如信号调制/解调(主要是频率和相位调制)、同步、时钟和数据恢复,以及倍频和频率合成。在这项实验中,您将建立一个简单的PLL电路,让您对PLL操作有基本的了解。

2023-07-10 10:22:24 794

794

在 SPI 中,主机可以选择时钟极性和时钟相位。在空闲状态期间,CPOL 为设置时钟信号的极性。空闲状态是指传输开始时 CS 为高电平且在向低电平转变的期间,以及传输结束时 CS 为低电平

2023-07-21 10:08:55 2924

2924

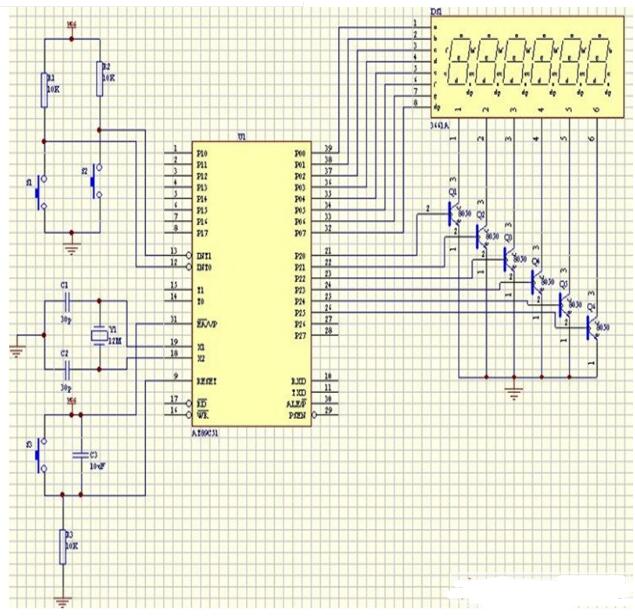

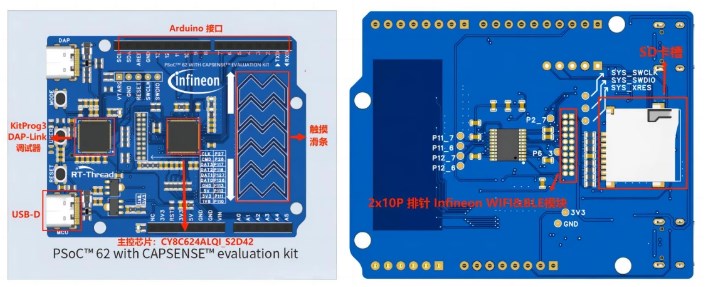

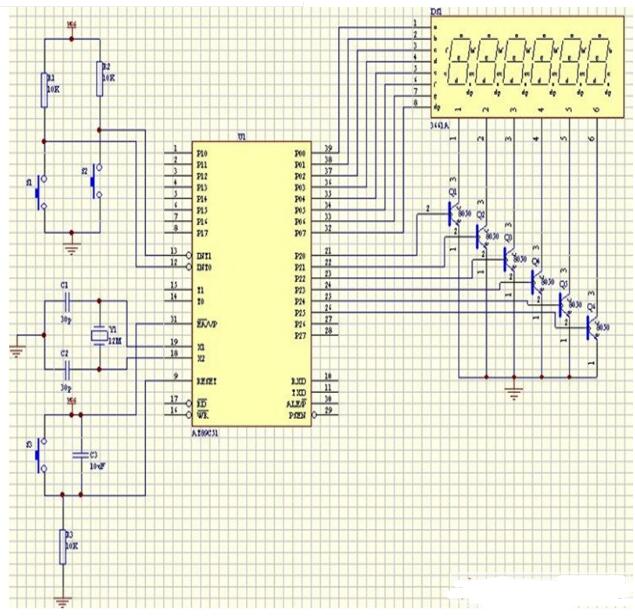

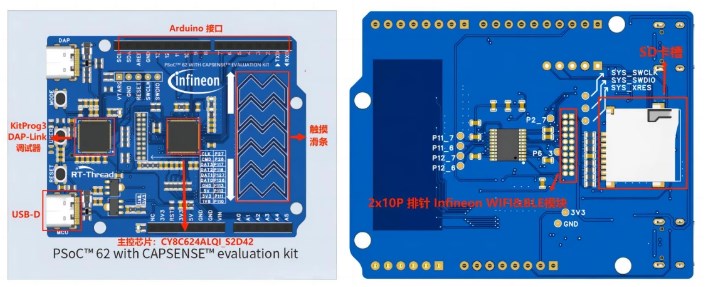

近年来,随着电子产品的发展,人们对时钟的要求越来越高。时钟系统是一种用数字电路技术实现年、月、日、周、时、分、秒计时的装置,与机械式时钟相比具有更高的准确性和直观性,且无机械装置,具有更更长的使用寿命,因此得到了广泛的使用。此时钟系统是基于posc6设计的,该系统包括了硬件电路部分和程序实现部分。

2023-07-31 14:51:22 562

562

)。晶体振荡器利用晶体的机械和电学特性,在特定的频率上产生稳定的振荡信号。RC振荡器则使用电阻和电容组成的回路,产生频率较低但相对简单和经济的振荡信号。PLL则通过反馈控制的方式,将输入信号与本地振荡器的输出信号同步,并提供具有可控频率和相位的时钟信号。

2023-08-24 15:40:10 8089

8089 的相位关系对于理解电路的行为非常重要。在纯电阻电路中,电流和电压之间的相位关系比较简单,本文将详细介绍纯电阻电路的电压与电流的相位关系。 一、什么是纯电阻电路 纯电阻电路是指电路中仅包含电阻器的电路,电路中没

2023-09-02 11:37:02 4927

4927 电子发烧友网站提供《大型多GHz时钟树中的相位偏差设计.pdf》资料免费下载

2023-11-22 16:56:01 0

0 相位补偿原理是什么?集成运算电路是否一定要进行相位补偿? 相位补偿原理是指通过合适的电路设计和调整,来解决信号在电路中传输过程中产生的相位偏移问题。在电路中,信号经过传输、放大等处理后,往往会产生相位

2024-02-02 09:50:37 350

350 什么是相位补偿电路?反激式开关电源光耦反馈电路为什么要相位补偿电路? 相位补偿电路是一种用于调整或补偿信号相位差的电路。它在电子设备和电路中起到重要的作用,特别是在反激式开关电源的光耦反馈电路

2024-02-02 09:50:46 412

412 移相电路是指对输入信号的相位进行调整,以便实现对信号的相位移动。相位差是指两个或多个信号波形之间的相位差异。要了解引起相位差的原因,我们需要先了解相位、频率和波形之间的关系。 相位是指用于描述信号

2024-03-11 15:49:29 221

221

电子发烧友App

电子发烧友App

评论