停电应急灯自动转换器工作原理

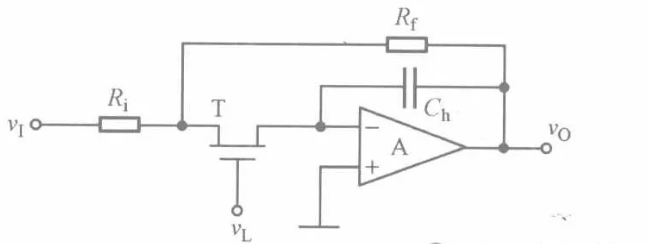

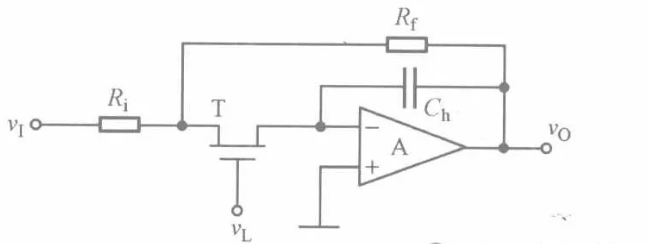

该装置的应用电路工作原理见下图。在一些不允许照明灯间断的特殊场合(如正在做外科手术等),利用LCE模

2009-12-29 17:59:16 6717

6717

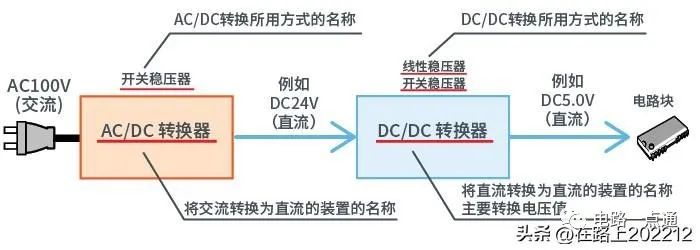

模拟数字转换器即A/D转换器,或简称ADC,通常是指一个将模拟信号转变为数字信号的电子元件。通常的模数转换器是将一个输入电压信号转换为一个输出的数字信号。由于数字信号本身不具有实际意义,仅仅表示

2023-02-20 16:52:19 9764

9764

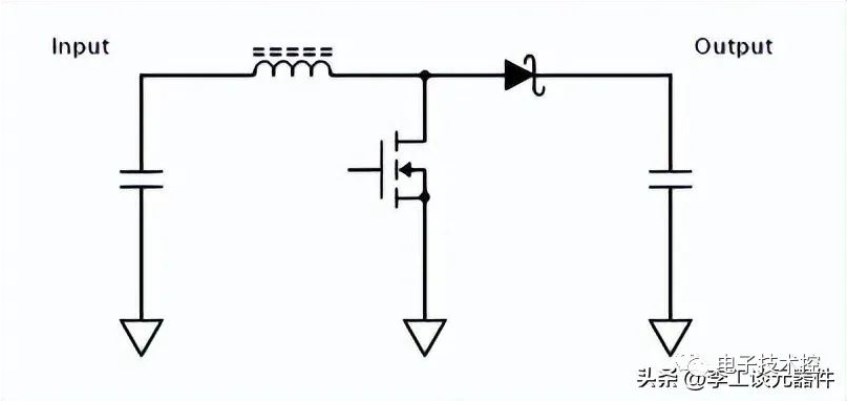

DC-DC 转换器 - Zeta 转换器

2023-08-14 16:59:32 3263

3263

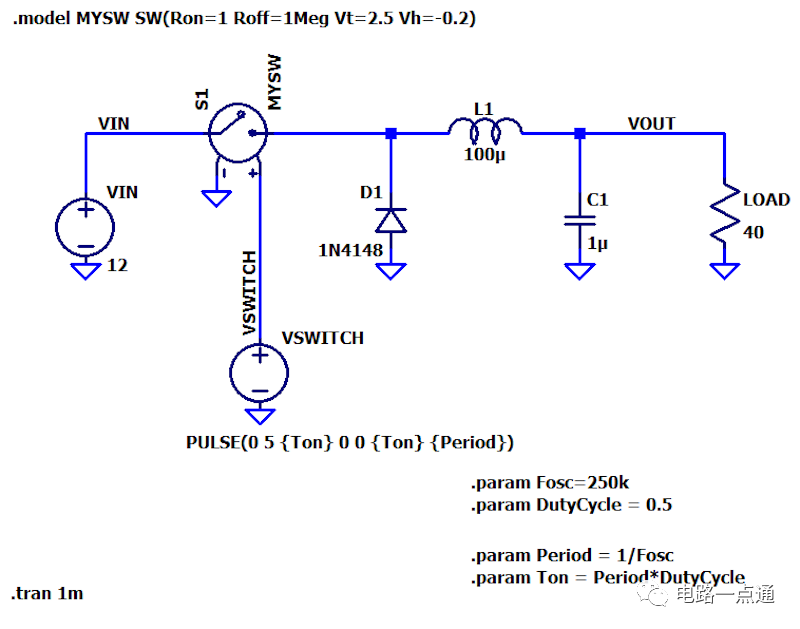

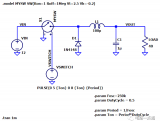

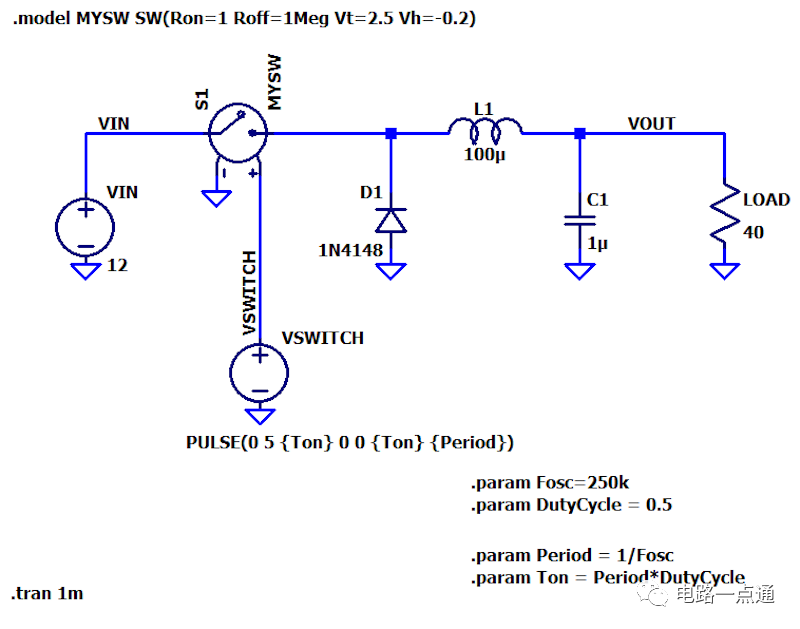

本文将详细分析降压 DC/DC 电压转换器的工作原理。使用 SPICE 仿真,我们将研究输出电压稳定、电压纹波以及电感器和负载电流。

2023-10-18 09:07:08 3490

3490

ADC转换器,希望有用的着AD5791.pdf

2014-5-18 15:27 上传

点击文件名下载附件

772.48 KB, 下载次数: 44

ADC

2018-07-13 00:44:58

ADC转换器选型怎么搞?如何选择最合适的ADC转换器?选型的时候除了考虑时序、精确度和可重复性还要考虑什么?

2021-04-06 07:07:08

目录1,浅谈常用ADC的工作原理与选型!2,ADC的选型(技术指标)3 转换速率(Conversion Rate):1,浅谈常用ADC的工作原理与选型!2,ADC的选型(技术指标)首先看精度和速度

2022-01-13 06:36:13

ADC的内部结构和特点是什么?ADC的工作原理是什么?ADC的启动方式有哪些?进行A/D转换时应注意的问题

2021-04-21 06:40:50

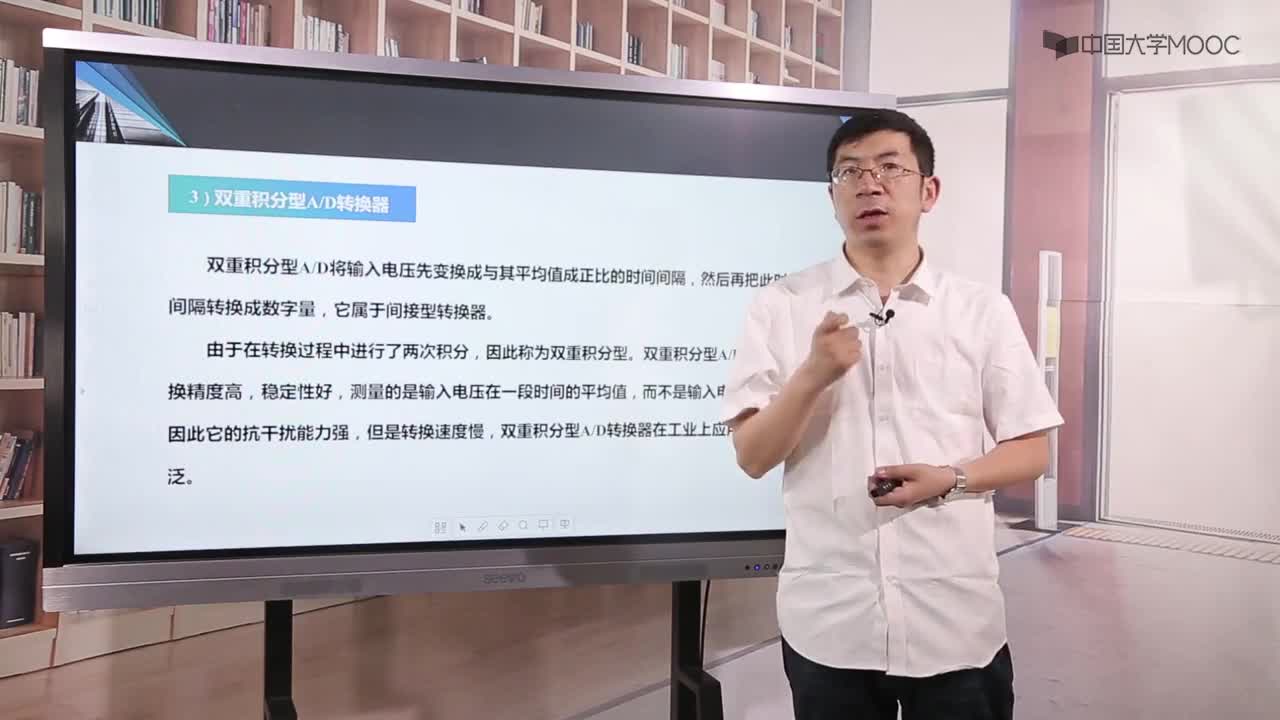

A/D转换器的基本原理和分类双积分式A/D转换器的基本原理

2021-04-06 07:08:36

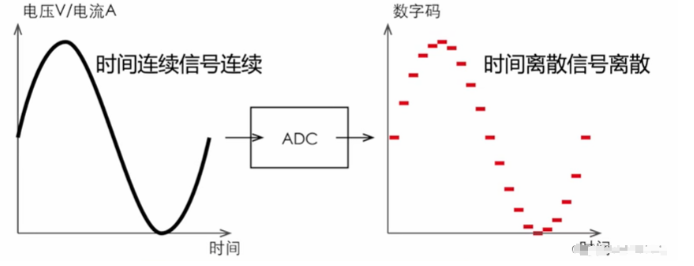

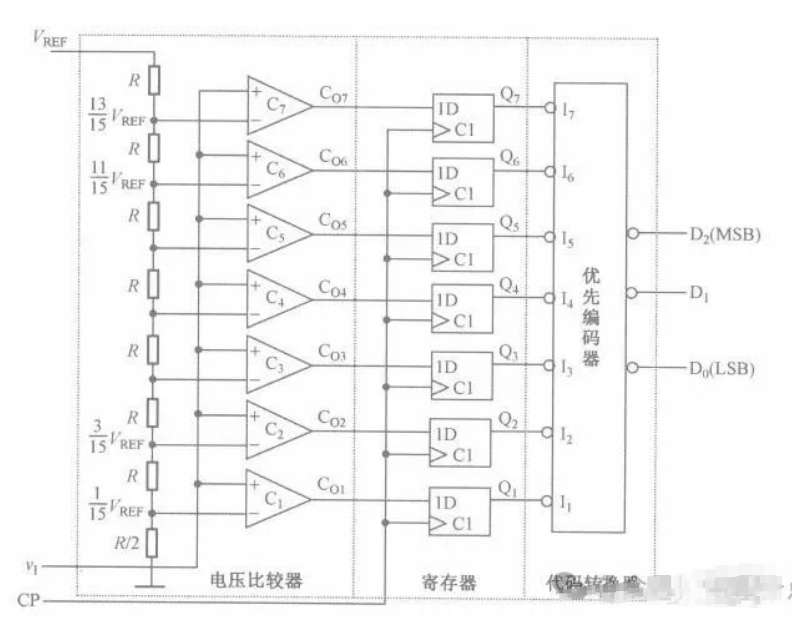

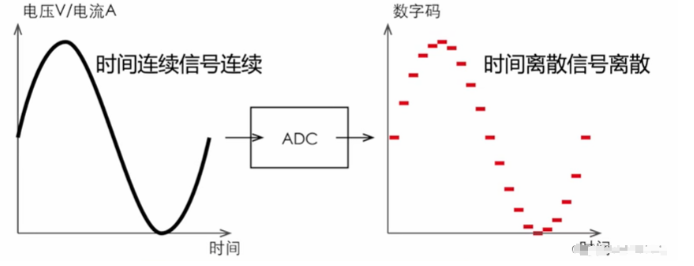

将模拟信号转换成数字信号的电路,称为模数转换器(简称a/d转换器或adc,analog to digital converter),A/D转换的作用是将时间连续、幅值也连续的模拟量转换为时间离散、幅值也离散的数字信号,因此,A/D转换一般要经过取样、保持、量化及编码4个过程。

2019-10-22 09:01:02

求问8位斜波式AD转换器的工作原理

2017-06-15 20:36:15

这里有一个AD转换器,LVDS是68针的,转换器型号:ADC120-LVDS,采集速率是30帧,怎么改成25帧

2013-01-16 15:16:46

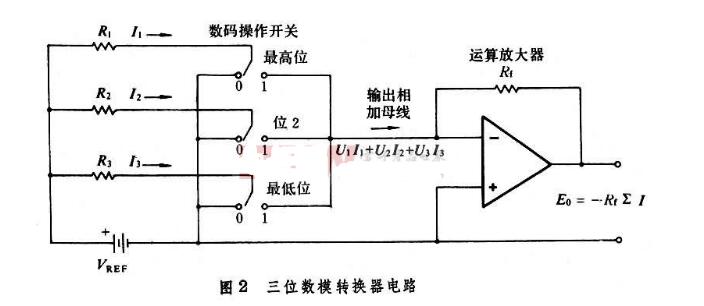

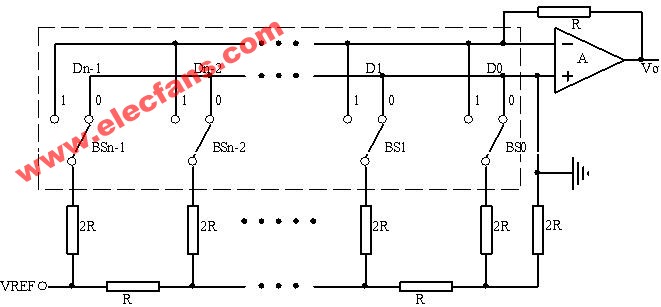

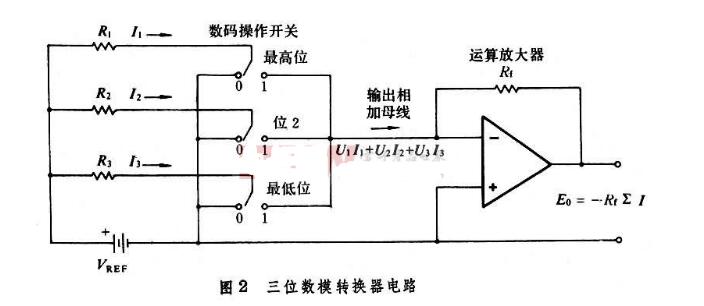

DA转换器工作原理

2012-08-20 18:00:27

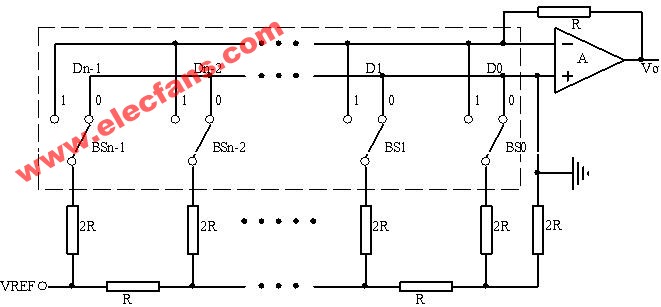

和语音信息处理等。二、工作原理D/A转换器输入的数字量是由二进制代码按数位组合起来表示的,任何一个n位的.

2021-12-10 07:05:25

目录:一、ADC原理1.ADC概述2.STM32ADC介绍3.STM32ADC工作原理二、STM32ADC库函数配置参考资料一、ADC原理1.ADC概述 ADC是Analog-to-Digital

2021-12-10 07:59:49

ADC模数转换器是什么?ADC模数转换器的相关寄存器有哪些?

2021-11-08 08:47:52

ADC模数转换器是什么?为什么需要ADC?STM32的ADC模数转换器有哪几种工作模式及应用呢?

2021-11-15 08:08:32

ADC以频率kfs采样单音信号的频谱分析 图3数字滤波器对噪声频谱的滤除效应2、 噪声成形通过下图所示的一阶Σ-Δ调制器的工作原理,可以理解噪声成形的工作机制。Σ-Δ调制器包含1个差分放大器、1个积分器

2016-08-03 09:02:37

1 AD7760(Σ-Δ模数转换器)1.1 Σ-Δ型ADC的工作原理的ADC不同,Σ-Δ型ADC不是直接根据采样数据的每一个样值的大小进行量化编码,而是根据前一量值与后一量值的差值即所谓的增量的大小

2021-08-09 07:38:19

ADC的工作原理是什么?ADC的主要特征有哪些?ADC的转换模式有哪几种?

2021-11-02 06:11:10

模数转换器定义ADC转换器是将模拟信号转换为数字信号的系统。这是一个过滤、采样并保持、量化和编码的过程。模拟信号通过带限滤波、采样保持电路,成为梯形信号,再通过编码器,使梯形信号中的每一电平

2023-02-15 18:16:05

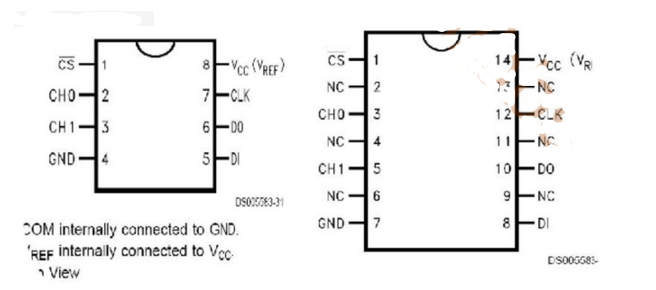

模数转换原理是什么?它的过程是怎样的?八位串行A/D转换器ADC0832具有什么特点?工作原理是什么?

2021-09-29 06:50:05

模数转换器 (ADC) 关于三角积分 (ΔƩ) 转换器,模拟传感器信号链面临着哪些高精度挑战?ΔƩ ADC 的工作原理又是什么? ΔƩ ADC 如何进行 数字扩展?

2021-03-11 07:24:56

如何进行模数转换器误差分析? 转换器内部何种程度才会导致这些误差的出现?

2021-03-07 07:44:47

AVR单片机实验六 AD转换应用实验1 实验目的通过实验,了解AVR单片机模数转换器的初始化,及以定时器自动触发AD转换的方法和工作原理。2 实验内容(1)调整可变电阻, 以获取模拟电压输入至ADC

2021-11-23 08:04:36

更愿意选用传统的逐次(SAR )型ADC 。 Σ- Δ转换器的模拟部分非常简单(类似于一个1 位ADC ),而数字部分要复杂得多,按照功能可划分为数字滤波和抽取单元。由于Σ- Δ型ADC 更接近于数字器件,因而其制造成本非常低廉。揭秘∑-Δ ADC的工作原理

2011-10-21 11:35:11

时间数字转换器TDC的工作原理是什么?TDC产品系列与应用有哪些?

2021-04-12 06:20:55

模数转换器(ADC)的基本原理是什么?常用的几种ADC类型的基本原理及特点是什么?

2021-09-28 08:21:04

ESP32 之 ESP-IDF 学习笔记(七)——模数转换器(ADC)文章目录ESP32 之 ESP-IDF 学习笔记(七)——模数转换器(ADC)一、简介1、两个 ADC 通道简介:2、减小

2022-02-17 06:28:34

介绍将模拟电子信号转换成数字信号的电路,称为模数转换器,简称A/D转换器或ADC。同理,将数字信号转换成模拟信号的电路称为数模转换器,简称D/A转换器或DAC目录1.逼近式ADC原理ADC控制寄存器

2022-02-18 06:54:10

模数转换器(ADC)是什么?模数转换器(ADC)的配置有哪些流程?配置流程的代码是什么?

2021-07-14 08:43:54

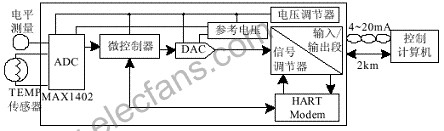

电流转换器输出4~20mA直流经电流转换器转换成0~10mA直流电流送给记录仪或Ⅱ型执行机构,反之,Ⅱ型变送单元输出0~10mA直流电流经电流转换器转换成4~20mA直流电流输送给控制室内S型仪表。

2019-09-12 09:12:33

ADC转换器的工作电压是多少?

2021-01-01 07:39:14

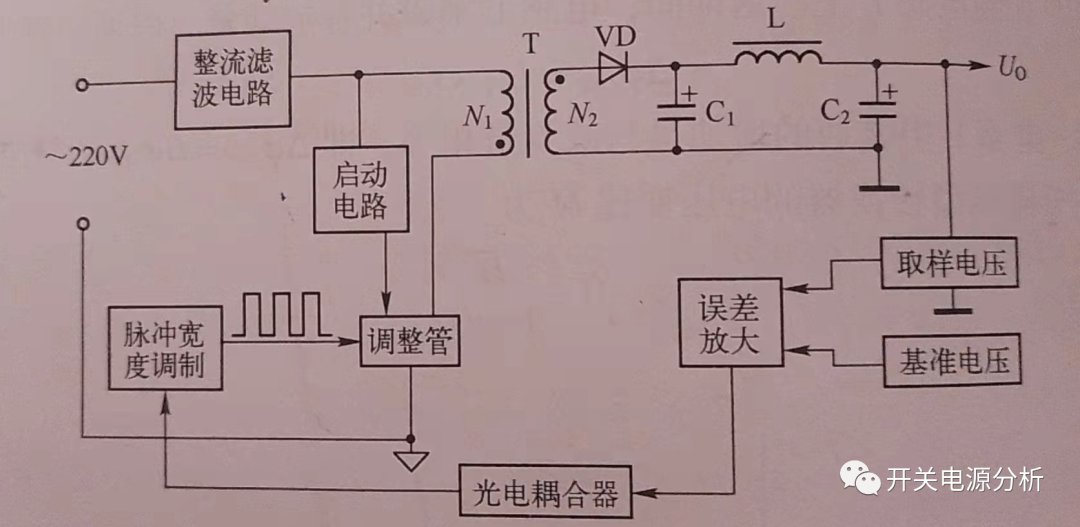

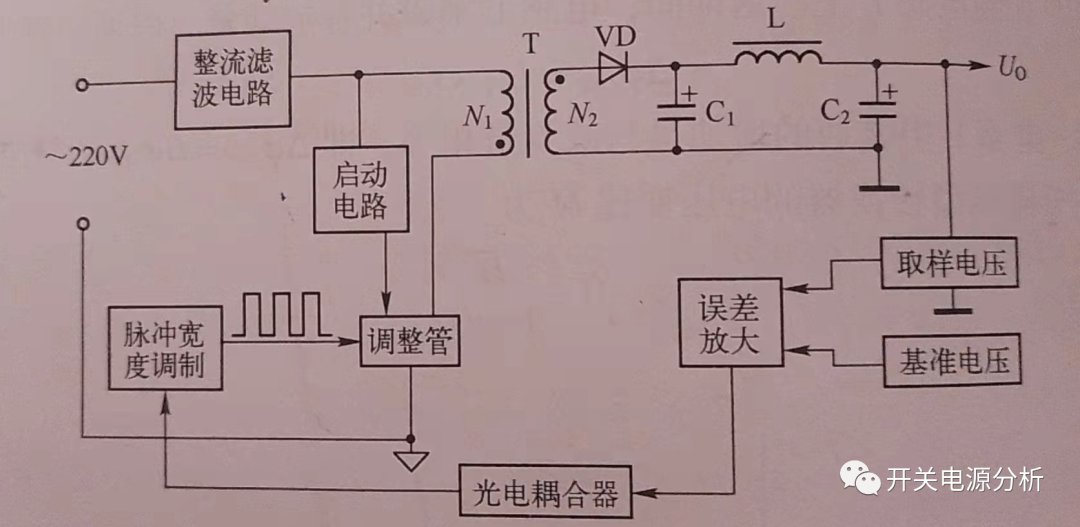

隔离反激式转换器的工作原理:当开关管VT导通时,变压器T初级Np有电流Ip,并将能量储存于其中(E=Lp*Ip?/2)。

2020-03-05 09:01:08

集成式DC/DC转换器结构是怎样的?如何去分析它的工作原理?

2021-04-07 07:03:09

电荷泵转换器工作原理:This paper analyzes the charge pump circuit operation principles. Useful formulas

2009-11-20 14:24:55 66

66 D/A转换器工作原理D/A转换器输入的数字量是由二进制代码按数位组合起来表示的,任何一个n位的二进制数,均可用表达式 DATA=D020+

2009-01-14 12:10:49 9248

9248

放映室灯光同步转换器工作原理

该装置的应用电路工作原理见下图。在放映幻灯或电影、录像时,往往要将室内的照明灯熄灭。放映结束时,

2009-12-29 18:00:47 2187

2187

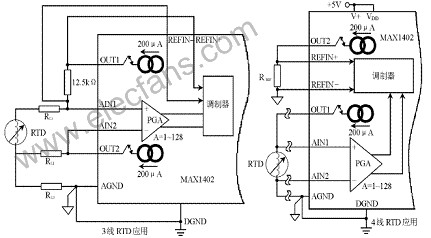

电流积分模数转换器(ADC),什么是电流积分模数转换器(ADC)

模数转换器(Analog to digital Converter,简称ADC)是模拟与数字世界的接口,为了适应计算机、通

2010-03-24 13:31:38 3461

3461 -A/D转换器是一种高精度的模数转换器,它和传统的A/D转换器不同,具有高分辨率、高集成度、造价低和使用方便的特点, 并且越来越广泛地使用在一些高精度仪器仪表和测量设备中。

2013-05-16 17:28:05 127

127 本文深入介绍模/数转换器(ADC)的工作原理,重点关注难以理解的数字概念:过采样、噪声整形和抽样滤波等。同时包括Σ-Δ转换器的多种应用。

2015-10-02 10:26:14 11332

11332 模数转换器也是转换器的一种类型,大家是否有使用过呢?模数转换器的功能是什么呢?又是如何发挥这些功能的呢?下面就让小编来给大家介绍一下模数转换器的工作原理。

2017-06-06 14:09:04 5589

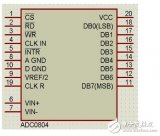

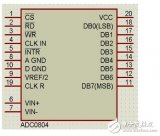

5589 集成A/D转换器品种繁多,选用时应综合考虑各种因素选取集成芯片。一般逐次比较型A/D转换器用的比较多,ADC0804就是这类单片集成A/D转换器。ADC0804是一款8位、单通道、低价格A/D转换器

2017-11-12 09:21:12 36848

36848

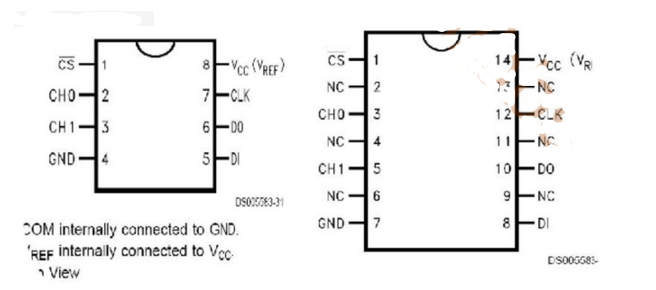

AD0832是8位逐次逼近模数转换器,可支持两个单端输入通道和一个差分输入通道。是8位逐次逼近模数转换器,可支持两个单端输入通道和一个差分输入通道。当ADC0832未工作时其CS输入端应为高电平,此时芯片禁用,当要进行A/D转换时,

2018-01-24 10:41:05 20588

20588

本文首先介绍了数模转换器的概念与结构,其次阐述了数模转换器工作原理与数模转换器的速度极限,最后介绍了数模转换器两个应用实例。

2018-04-20 11:18:15 7321

7321

演讲者:Marco Panizza,Vicor欧洲应用工程部经理。本课程讲解了 DC-DC 转换器的工作原理,以及Maxi,Maxi,Micro模块的方块图,和零电流开关架构的功率转换拓扑。

2018-06-19 09:46:00 9021

9021

本文主要介绍全新双向DC-DC转换器的设计与分析。这项全新的拓扑及其控制策略彻底解决了传统双向DC-DC转换器(电源容量及效率有限)中存在的电压尖峰问题。该转换器不仅可用作电池组和DC母线接口,而且

2022-03-24 13:56:00 31041

31041 本文档的主要内容详细介绍的是ADC转换器的基础知识详细资料说明包括了:1.ADC简介,2.采样与量化,3.ADC工作原理,4.ADC选型,5.checklist

2019-07-18 08:00:00 5

5 因为隔离式转化器的工作原理,我们也可以将它称为逆变整流转换器,我们常见的主要类型有:反激式、正激式、推挽式、半桥式和全桥式。

2022-11-02 14:56:49 4486

4486

随着前几期的介绍,大家应该已经对降压转换器各个组成部分有了足够的认识。这一期视频我们则会讲解降压转换器的工作原理,希望通过这一期视频,大家可以真正入门并灵活地推导应用相关关系式。

2022-11-21 14:48:33 2671

2671 数据转换器是一种仪器、装置,也是一种电子元器件,它的主要作用是将其他类型的电能信号转换成另一种,并且能够将一种电能因数信号转换成另一种电能因数信号。数据转换可分分为两大类:电能信号转换和电能因数信号转换。下面AMEYA360电子元器件采购网详细介绍:数据转换器的基本工作原理及使用方法!

2023-05-15 11:29:38 3013

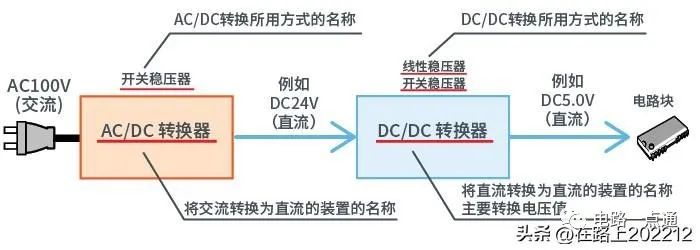

3013 DC-DC转换器工作原理是什么? DC-DC转换器是一种电子设备,它可以将电源输入电压(VIN)变成不同的电压输出(VOUT),通常用于电路设计中,以实现电源管理和控制。这些转换器将直流电(DC

2023-08-18 15:01:13 5841

5841 等领域。ADC的作用是将模拟信号转换成数字信号,数字信号可以更好地被储存和处理,进一步实现信号的分析与处理,提高信息的精度和可靠性。本文将详细介绍ADC模数转换器的作用。 一、模拟信号与数字信号的区别 模拟信号是指连续变化的信号,如声音、电压等;数字信号是指离散的

2023-09-02 10:13:13 3683

3683 降压转换器(Buck Converter)和升压转换器(Boost Converter)都是常见的直流-直流(DC-DC)转换器,用于将直流电压转换为不同的电压水平。降压转换器将输入电压降低到输出电压以下,而升压转换器将输入电压提高到输出电压以上。

2023-10-05 16:15:00 4000

4000 模数转换器(ADC,Analog-to-Digital Converter)是一种将模拟信号转换为数字信号的设备。在现代电子系统中,ADC在各种应用中发挥着重要作用,如传感器信号处理、通信系统、医疗

2023-09-27 17:11:24 9530

9530 ADC模数转换器的延时原理主要与其内部的采样和保持电路、比较器、计数器等有关。以下是一般的ADC转换延时过程:

2023-11-16 15:59:24 1832

1832 电子发烧友网站提供《数据转换器中采样过程的工作原理.pdf》资料免费下载

2023-11-27 10:50:37 0

0 模数转换器(DAC)是将数字信号转换为模拟信号的设备。其工作原理可以简单描述如下

2023-11-27 18:27:00 2225

2225 电子发烧友网站提供《数据转换器中采样过程的工作原理.pdf》资料免费下载

2023-11-28 10:31:26 1

1 光电转换器(Photovoltaic Converter)是一种将光能转化为电能的设备。它的作用是将太阳光中的光能转换为直流电能,以满足日常生活和工业生产中对电能的需求。 光电转换器的工作原理

2023-12-21 16:32:13 12151

12151 DC-DC转换器电路图 Boost升压型DC-DC转换器的工作原理

Boost升压型DC-DC转换器是一种常用的电源管理电路,它可以将较低的直流输入电压转换成较高的直流输出电压。其工作原理主要

2024-01-19 18:28:42 4843

4843 升压转换器的工作原理、优点和应用 升压转换器是一种电力电子器件,用于将输入电压提升到较高的输出电压。其工作原理基于电感储能和开关控制,是一种非常常见和重要的电源转换器。 升压转换器的简化原理图 一

2024-02-01 14:08:17 4884

4884

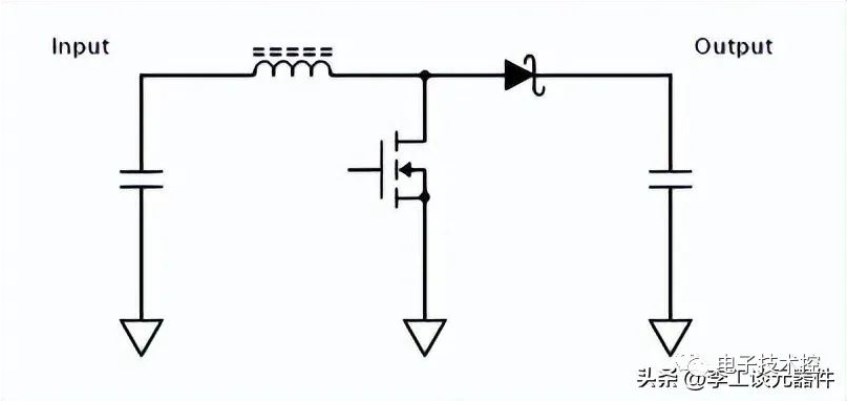

降压DC/DC电压转换器,又称为降压转换器、低压降转换器或简称为降压器,是一种电力转换器,它能够将其输入的直流电压转换成一个更低的直流输出电压。降压转换器的基本工作原理是通过开关电路和能量存储元件

2024-02-16 09:37:00 3252

3252

多个不同电压级别的应用中。 工作原理 DC/DC转换器的工作原理基于能量转移和控制。它们通过储能组件(如电感、电容或两者的组合)临时存储能量,然后以不同的方式释放这些能量,从而实现电压的变换。根据设计,DC/DC转换器可以升高(升压)

2024-02-04 10:06:31 6151

6151

在电子技术不断创新的今天,压频转换器作为连接电压与频率的关键组件,发挥着重要作用。但是您是否好奇它是如何运作的?本文将揭开压频转换器的神秘面纱,解析其工作原理及应用前景。 一、压频转换器的基本概述

2024-04-30 15:46:09 2222

2222 揭开DC-DC转换器工作原理的神秘面纱。 一、DC-DC转换器概述 DC-DC转换器,即直流-直流转换器,是一种将一个直流电压转换为另一个直流电压的电子设备。它的工作原理是通过开关管(如MOSFET、IGBT等)的高速开关动作,将输入的直流电压斩波成脉冲波

2024-05-15 15:51:50 4644

4644 的传输和处理提供了可能。本文将详细阐述数模转换器的基本概念、工作原理、分类、应用及其特点,以期为读者提供全面而深入的理解。

2024-05-21 15:59:32 6224

6224 模数转换器(ADC,Analog-to-Digital Converter)是数字电子系统中不可或缺的重要组件。它实现了模拟信号到数字信号的转换,为数字系统提供了处理连续时间模拟信号的能力。本文将对模数转换器的基本概念、工作原理、分类、应用及其特点进行详细的阐述,以期为读者提供全面而深入的理解。

2024-05-21 16:05:14 3259

3259 在电力和电子领域中,变压器和转换器都是至关重要的设备。它们各自在电路中发挥着特定的作用,虽然有些功能看似相似,但两者的工作原理和实际应用却存在显著的差异。本文将详细介绍变压器和转换器的工作原理,并探讨它们之间的区别。

2024-05-22 18:14:42 3775

3775 在电子技术和电力电子领域中,降压转换器(Buck Converter)是一种至关重要的设备。它以其独特的功能和高效的工作原理,广泛应用于各种电子设备、通信设备、汽车电子以及工业自动化等领域。本文将详细探讨降压转换器的功能、工作原理以及其在各个领域的应用,以期为相关领域的读者提供深入的了解和参考。

2024-05-23 16:40:04 2184

2184 AC-AC转换器,即交流-交流转换器,是一种将一种交流电转换为另一种交流电的电子设备。在现代电子系统中,AC-AC转换器扮演着至关重要的角色,它们被广泛应用于电力电子、工业自动化、通信系统等多个领域。本文将详细阐述AC-AC转换器的工作原理,并介绍其主要类型。

2024-05-23 17:09:24 10857

10857 在电子技术的快速发展中,电源转换器作为电子设备的重要组成部分,其性能直接影响到整个系统的稳定性和可靠性。反激式转换器,作为电源转换器的一种,因其独特的结构和工作原理,在电源领域得到了广泛的应用。本文将详细阐述反激式转换器的工作原理以及其主要类型,并探讨其在现代电子技术中的应用。

2024-05-23 17:10:49 1723

1723 LLC谐振转换器是一种基于谐振振荡原理工作的电力转换器,它以其高效率、低电磁干扰和宽输入输出范围等特点,在电力电子领域得到了广泛应用。以下将详细阐述LLC谐振转换器的工作原理。

2024-07-16 11:29:33 6935

6935 同步降压转换器(Synchronous Buck Converter),作为一种重要的电源管理电路,其工作原理和作用在电子技术和电力电子领域中占据着重要地位。以下是对同步降压转换器工作原理和作用的详细阐述。

2024-08-14 09:51:15 4774

4774 设备、电力系统等众多领域中得到广泛应用。以下将详细阐述交直流转换器的工作原理,包括整流过程、逆变过程及其相关电路和技术。

2024-08-14 10:51:14 5808

5808 领域得到了广泛应用。以下将详细阐述LLC电源转换器的工作原理,包括其主要组成部分、工作过程、调制方式、工作区域及其特性、效率提升措施以及应用实例等。

2024-08-20 17:17:12 4267

4267 LLC电源转换器的工作频率是一个关键参数,它直接影响到变换器的性能、效率和稳定性。然而,要详细阐述LLC电源转换器的工作频率,需要深入探讨其工作原理、设计考虑、实际应用以及技术挑战等多个方面。以下是对LLC电源转换器工作频率的详细分析。

2024-08-20 17:19:28 3369

3369 为离散的数字信号,以便数字系统进行处理、存储和传输。这一转换过程涉及采样、量化、编码等多个步骤,是连接模拟世界与数字世界的桥梁。以下将从A/D转换器的定义、工作原理、关键参数、特点、应用以及发展趋势等方面进行详细阐述。

2024-08-30 14:36:07 5450

5450 其工作原理和设计特点所决定的。 LLC转换器的工作原理 LLC转换器是一种谐振型开关电源,其核心组成部分包括一个主开关、一个谐振电感、一个谐振电容以及一个辅助开关。在LLC转换器的工作原理中,主开关和辅助开关交替工作,通过谐振电感和谐

2024-09-06 15:46:00 2555

2555 在电子系统中,模数转换器(Analog-to-Digital Converter,简称ADC或A/D转换器)是至关重要的一环,它负责将连续的模拟信号转换为离散的数字信号,以便于数字系统进行处理和分析

2024-10-05 11:36:00 8502

8502 ADC(Analog-to-Digital Converter,模数转换器)采样保持电路是ADC转换过程中的一个重要组成部分,其工作原理和技术指标对于确保ADC转换的精度和可靠性至关重要。以下是对ADC采样保持电路工作原理和技术指标的详细阐述。

2024-10-05 14:33:00 6652

6652

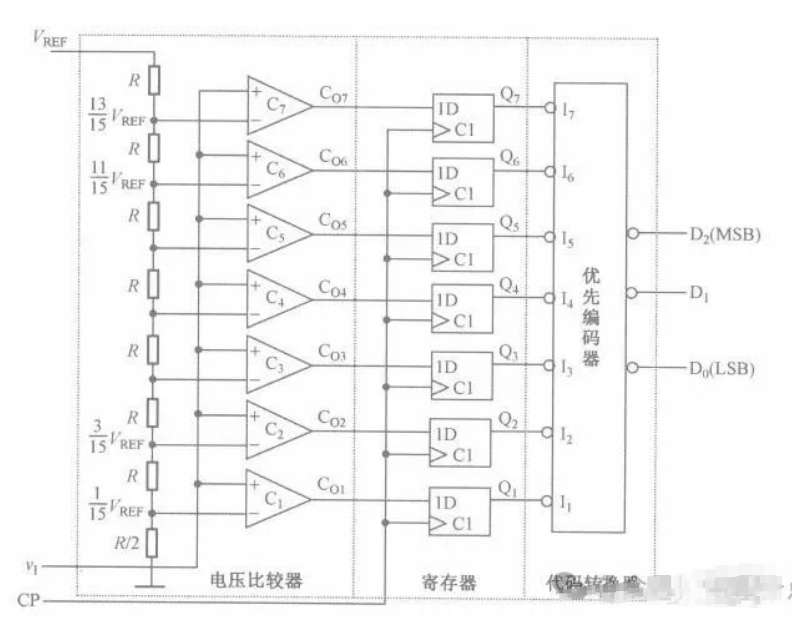

并行比较型AD转换器是模数转换器(ADC)中速度最快的一种类型。其工作原理基于并行处理技术,通过多个比较器同时工作,将输入的模拟信号与多个参考电压进行比较,从而一次性完成所有位的转换。

2024-10-05 14:48:00 5338

5338

技术和相对较高的转换精度而著称。以下是对双斜率积分A/D转换器的详细概述,包括其工作原理、组成结构、特点及应用等方面。

2024-10-05 14:53:00 2875

2875 在数字电子技术飞速发展的今天,模拟信号与数字信号之间的转换变得尤为重要。ADC转换器,即模拟-数字转换器,正是实现这一转换的关键技术。 一、ADC转换器的工作原理 采样(Sampling) 模拟信号

2024-10-18 14:00:01 2400

2400 ADC0809是一款8位逐次逼近型模数转换器(ADC),广泛应用于需要将模拟信号转换为数字信号的场合。它能够将0到5伏的模拟电压信号转换为8位二进制数字信号。 ADC0809的基本结构

2024-10-21 09:32:19 3764

3764 在现代电子系统中,模拟信号和数字信号之间的转换是必不可少的。模拟信号,如温度、声音、光强等,需要被转换成数字信号,以便进行进一步的处理、存储或传输。模拟/数字转换器(ADC)正是完成这一任务的设备

2024-10-31 10:34:43 1371

1371 模数转换器(Analog-to-Digital Converter,简称ADC)是现代电子系统的核心组件,承担着将连续变化的模拟信号转换为离散数字信号的关键任务,方便数字系统进行处理、存储和传输。

2025-10-28 14:24:32 237

237 Sigma Delta型模数转换器又称Σ-Δ型模数转换器,模数转换器(ADC)作为连接物理世界与数字系统的关键部件,广泛应用于工业控制、汽车电子和物联网设备中。其中,Σ-Δ型模数转换器凭借其高分辨率和优良的抗噪性能,成为高精度测量领域的首选技术。

2025-11-10 17:25:41 717

717

电子发烧友App

电子发烧友App

评论